Vitis™ HLS 是一种高层次综合工具,支持将 C、C++ 和 OpenCL™ 函数硬连线到器件逻辑互连结构和 RAM/DSP 块上。Vitis HLS 可在Vitis 应用加速开发流程中实现硬件内核,并使用 C/C++ 语言代码在 Vivado® Design Suite 中为赛灵思器件设计开发 RTL IP。

Vitis 高层次综合用户指南(UG1399)包括Vitis HLS 入门、Vitis HLS 硬件设计方法论、Vitis HLS C 语言驱动程序参考资料、Vitis HLS 命令参考资料、Vitis HLS 库参考资料,以及Vitis HLS 移植指南。由于本指南较长,下文仅摘录部分内容。如果您希望查阅完整版,请至文末链接点击下载。

Vitis HLS 简介

在 Vitis 应用加速流程中,在可编程逻辑中实现和最优化 C/C++ 语言代码以及实现低时延和高吞吐量所需的大部分代码修改操作均可通过 Vitis HLS 工具来自动执行。在应用加速流程中,Vitis HLS 的基本作用是通过推断所需的编译指示来为函数实参生成正确的接口,并对代码内的循环和函数执行流水打拍。Vitis HLS 还支持自定义代码以实现不同接口标准或者实现特定最优化以达成设计目标。

Vitis HLS 设计流程如下所述:

编译、仿真和调试 C/C++ 语言算法。

查看报告以分析和最优化设计。

将 C 语言算法综合到 RTL 设计中。

使用 RTL 协同仿真来验证 RTL 实现。

将 RTL 实现封装到已编译的对象文件 (.xo) 扩展中,或者导出到 RTL IP。

高层次综合基础

赛灵思 Vitis HLS 工具可将 C 语言或 C++ 语言函数综合到 RTL 代码中,用于在可编程逻辑内进行加速。Vitis HLS 与Vitis 核开发套件和应用加速设计流程紧密集成。

使用高层次综合 (HLS) 设计方法论的优势包括但不限于:

编译、仿真和调试 C/C++ 语言算法。

查看报告以分析和最优化设计。

将 C 语言算法综合到 RTL 设计中。

使用 RTL 协同仿真来验证 RTL 实现。

将 RTL 实现封装到已编译的对象文件 (.xo) 扩展中,或者导出到 RTL IP。

⬇️上下滑动查看更多内容⬇️

HLS 包含以下阶段:

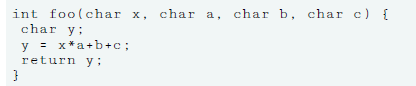

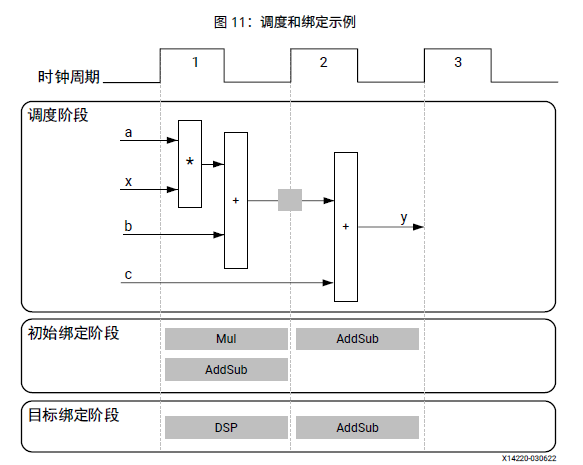

以调度和绑定为例,下图显示了此代码示例的调度和绑定阶段的示例:

在此示例的调度阶段,根据高层次综合的调度,在每个时钟周期内将执行以下操作:

第一个时钟周期:乘法和第一次加法

第二个时钟周期:如果在第二个时钟周期内第一次加法的结果可用,则执行第二次加法并输出生成。

在最终的硬件实现中,高层次综合将顶层函数的实参实现为输入和输出 (I/O) 端口。在此示例中,实参是简单数据端口。因为每个输入变量都是 char 类型,所以输入数据端口位宽均为 8 位。return 函数为 32 位 int 数据类型,而输出数据端口位宽为 32 位。

在此示例的初始绑定阶段,高层次综合使用组合乘法器(Mul)实现乘法运算,并使用组合加法器/减法器(AddSub)实现两次加法运算。

在目标绑定阶段,高层次综合使用 DSP 模块资源实现乘法器和其中一项加法运算。部分应用使用大量二进制乘法器和累加器,这些乘法器和累加器最好在专用 DSP 资源内实现。DSP 模块是 FPGA 架构中可用的计算块,可在高性能和高效实现之间达成理想的平衡。

Vitis HLS 进程概述

Vitis HLS 基于工程,可包含多个变体(称为“解决方案”)以驱动综合与仿真。每个解决方案均可将 Vivado IP 流程或Vitis 内核流程设定为目标。基于目标流程,每个解决方案都将指定不同的约束和最优化指令,如 启用 Vivado IP 流程和启用 Vitis 内核流程中所述。

以下提供了典型设计流程中的综合、分析与最优化步骤:

1

创建新的 Vitis HLS 工程。

2

利用 C 语言仿真来验证源代码。

3

运行高层次综合以生成 RTL 文件。

4

分析结果,包括检验时延、启动时间间隔 (II)、吞吐量和资源使用情况。

5

执行最优化,并按需重复此步骤。

6

使用 C/RTL 协同仿真验证结果。

Vitis HLS 基于目标流程、默认工具配置、设计约束和您指定的任意最优化编译指示或指令来实现解决方案。您可使用最优化指令来修改和控制内部逻辑和 I/O 端口的实现,以覆盖工具的默认行为。

⬇️上下滑动查看更多内容⬇️

C/C++ 代码综合方式如下:

综合后,您可以对先前生成的各项报告中的结果进行分析,以确定结果质量。分析结果后,您可以为工程创建其它解决方案,指定不同的约束和最优化指令,并对这些结果进行综合与分析。您可对不同解决方案的结果进行比较,查看哪些有效,哪些无效。您可重复此过程,直至设计达成所期望的性能特性为止。您可使用多种解决方案持续进行开发,同时仍可保留先前的解决方案。

扫描二维码下载完整指南

或点击“阅读原文”下载