点击上方蓝字关注我们

FPGA已然成为一种策略性技术,它被视为“穷人的ASIC”,且能够为少量应用提供客制化IC;而当它仍然在许多系统中以这种方式被应用的同时,在以下两个量很大、高成长的应用中,也变得更具策略上的重要性:

云端数据中心:连网、储存与安全性;

通信系统:基地台和5G等等。

事实上,因为FPGA对数据中心所具备的策略性意义,促使英特尔(Intel)收购Altera (EETT编按:2015年完成收购),还有最近AMD对赛灵思(Xilinx)的并购。这是因为在许多状况下,处理器的工作负载正被移转到FPGA上。

大量利用FPGA的数据中心,能提供处理器所无法实现的平行可程序化能力(有一个客户称之为“在硬件速度下的可程序化能力”)。这些FPGA与具有特定功能的IC搭配应用,例如网络接口芯片(network interface chip,NIC)和网络交换器芯片。

每个数据中心有不同的工作负载,因此以标准化产品来满足所有的需要是行不通的,每个数据中心有不同的数量规模和资本,以根据需求进行优化。通信系统则是长期以来使用FPGA处理数百个国家级频段和通信协议;在当前5G的环境中,FPGA则被用来管理复杂性,和诸如O-RAN等持续变化中的标准。

尽管FPGA的可程序化能力如前面所述相当有价值,该类组件的功率和尺寸又是另一个故事──今日的数据中心和通信厂商想要将FPGA整合到SoC里,以缩小尺寸和功耗。

近十年来,包括Achronix、Flex Logix和Menta等厂商,已经具备提供嵌入式FPGA (eFPGA)产品的能力。eFPGA现在可使用180纳米到7纳米工艺节点生产,容量从1K查找表(LUT)到100K LUT,并即将迈向1M LUT,亦可供应DSP和Block-RAM选项。

以下是eFPGA获得整个产业采用的一些重要事件:

第一家宣布成功使用eFPGA的客户是美国桑迪亚国家实验室(Sandia National Labs),他们是在新墨西哥州180纳米晶圆厂实现了这个目标。从此之后,他们利用eFPGA制造了众多ASIC。

接下来,波音(Boeing)、美国空军研究实验室(AFRL)、微软(Microsoft)、BAE和其他许多政府机构与包商,也开始在美国制造的防卫系统中密集使用eFPGA。因此,对美国国防部和能源部来说,eFPGA现在已经是一种成熟技术。

中国厂商大唐电信旗下的芯片设计子公司宸芯科技(Morning Core)宣布将在车对车通信FinFET ASIC采用eFPGA。

Dialog (EETT编按:已被Renesas收购)在2021年11月发表ForgeFPGA系列eFPGA产品开始出货,以1K LUT起跳、单价低于50美分,功耗仅几毫瓦(milliwatt)。

Flex Logix在自家16纳米AI推论芯片上采用eFPGA,性能超越500MHz,且随着时间的变化和软件强化,性能可以提升至667MHz甚至800MHz。

Socionext正在与一家系统大厂合作开发7纳米SoC,利用eFPGA和100K LUT的可程序化逻辑电路,使得芯片在最差的情况下还能有超过500 MHz的表现。这是一个5G应用,也是首款整合了大量LUT的量产通信芯片。

除了以上事件,还有更多正在利用eFPGA的客户还未公开。随着人们对该技术的认知提升,客户采用eFPGA的步伐正在加速;利用eFPGA的领导厂商们,也正在所属的市场领域取得显著竞争优势。

FPGA具备显著的优势,但是它们并不容易编程;而且比起处理器的程序设计师,合格的FPGA程序设计师人数更少。为何FPGA编程如此困难?主要原因如下:

Verilog是比C++更像汇编语言(assembler)的一种低阶程序语言。

对传统的程序设计师来说,平行编程很难理解和学习。

FPGA是以一个巨大程序代码“区块”(blob)的形式被编程,而处理器则是包含子程序(subroutine)、主程序(main program)、链接程序(linker)和加载程序(loader)、分页(paging)等等;程序设计师将这些视为理所当然,但并不适用于FPGA。

FPGA可以在几秒内进行编程,永远存在于硬件,而且通常整个FPGA必须被重新编程;有一些可以部分编程,但是执行速度很慢,且所有运作会因此暂停。在处理器程序代码中,当主执行续运作时,分页则会一直被换进/换出快取。

eFPGA提供了重新思考这种编程策略的机会──利用稀有的Verilog编码器并且让C++编码器能对FPGA进行软件控制。以下是其中一种方法的基本概念。

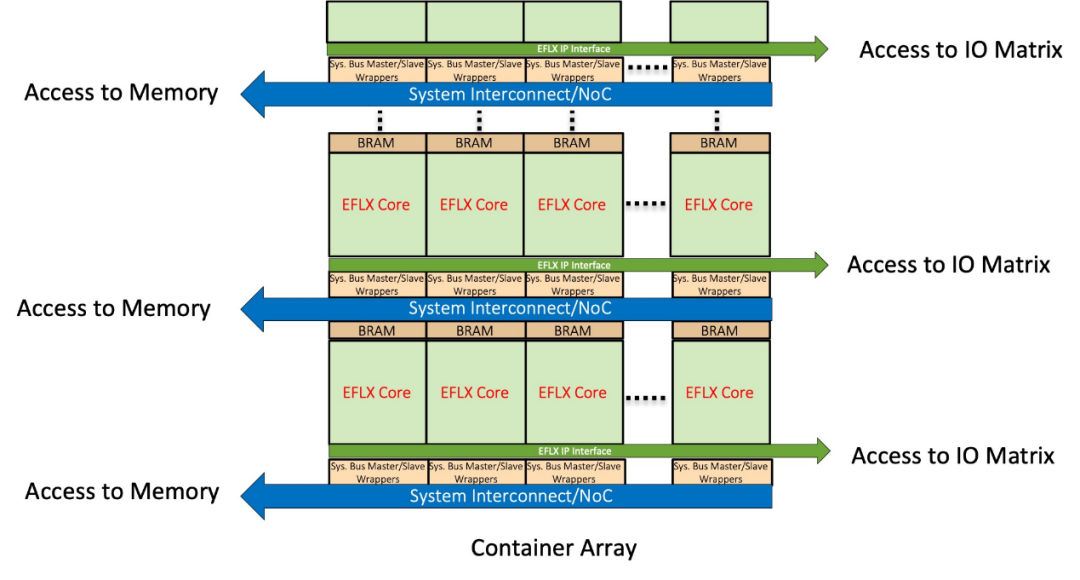

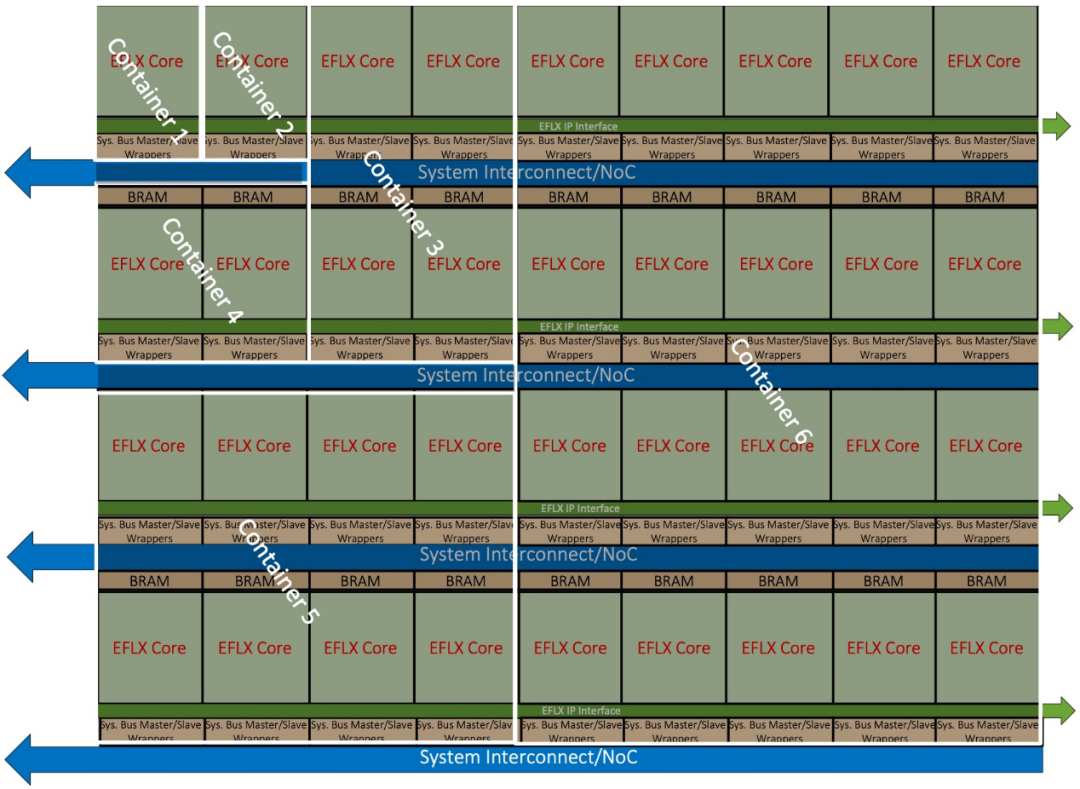

把一个FPGA区分成更小的模块或容器,并让它们直接存取到DRAM内存和处理器。eFPGA是以模块化方式建构,能根据需要以区块RAM (block RAM,BRAM)将行与行之间的砖(tile)式结构“扣”在一起。如此一来很容易增加一个系统的互连/芯片上网络(NoC)/AXI总线,并让每个FPGA模块/容器都能存取内存/处理器。

现在,将FPGA程序代码编写成能够像包含在一个容器里的子程序那样地运作,可以提供输入数据或指向系统内存的数据;然后让FPGA执行,接着传递结果视为输出数据,或是指向系统内存中的数据。利用稀有的Verilog编码器写入那些需要密集运算的“子程序”,然后让C++编码器在处理器上写入程序代码,在需要的时候呼叫那些子程序。

容器化的FPGA程序代码数组。

将FPGA切割成更小的模块或容器,能让它们直接存取DRAM内存和处理器。有些算法较简单且使用较少的LUT,有些则会用到更多的LUT。举例来说,利用Flex Logix的弹性互连结构,能让容器变成任何尺寸的长方形,直到整个数组的大小。

容器的尺寸大小可以改变。

FPGA总能从闪存在几秒内进行可程序化的动作──非常缓慢,且一般而言,并不是常常这么做:在开机时或需要升级动作时才需要如此,像是升级iPhone。

然而,eFPGA已经可以领先的AI推论处理器上,以一秒好几百万次速度被重新编程;这是必须的,因为推论加速器处理一个类神经网络层需要好几十亿次的运算,在小于 10 微秒(microsecond)的时间内重新配置,然后重新开始运算。

这个微秒级的重新配置能够运用在上述数组里的容器和模块。当一个容器被重新配置,剩余的容器会继续以全速运作。这使得eFPGA可以像处理器一样进行分页。

我们已经看着这个产业从简单的算术逻辑单元(ALU)开始、经历了处理器、微处理器、平行处理器,再到 SoC (包括处理器核心与加速器)的转变。而今天,我们拥有可重新配置的SoC,它们可以更充分地利用一个系统中具有大量核心的优势。

eFPGA将让数据中心和通信领域的客户能继续受益于FPGA的平行可编程特性,同时降低功耗、缩小尺寸并得以透过软件控制FPGA,以提高生产力、缩短上市时程。基于所有这些理由, eFPGA实现了运算架构的新典范转移,既透过整合来提高每个机架的运算密度,又能让更多的C++程序设计人员能够享受eFPGA的好处。

由于以上种种原因,eFPGA整合将加速并让更多LUT被整合在SoC里,超越近十年来已售出FPGA里的LUT数量。

作者:Geoff Tate,Flex Logix首席执行官

EET电子工程专辑原创

往期精选

FPGA技术江湖广发江湖帖

无广告纯净模式,给技术交流一片净土,从初学小白到行业精英业界大佬等,从军工领域到民用企业等,从通信、图像处理到人工智能等各个方向应有尽有,QQ微信双选,FPGA技术江湖打造最纯净最专业的技术交流学习平台。

FPGA技术江湖微信交流群

加群主微信,备注职业+方向+名字进群

FPGA技术江湖QQ交流群

备注地区+职业+方向+名字进群