Zynq UltraScale+ RFSoC 是业界首款单芯片自适应无线电平台,在一款芯片内集成射频直采数据转换器、单芯片软决策前向纠错核(SD-FEC)、FPGA逻辑、完整的ARM处理器子系统和高速收发器等。

第三代RFSoC器件与前几代产品相比,射频输入输出频率响应已扩展至全面支持6GHz以下频段,可帮助用户开发尖端RF设计,例如大规模MIMO无线电、5G基带、固定无线接入、测试测量与相控阵雷达等等。第三代器件14bit分辨率ADC最大采样速率增加到5.0GSPS,14bit分辨率DAC最大采样速率增加到10.0GSPS。用户可以参考XMP105详细了解Zynq RFSoC系列产品具体参数及选型指南。

本次将分上下篇介绍基于Xilinx Zynq UltraScale+ RFSoC ZCU216评估套件的详细内容:

1. 第三代RFSoC 器件时钟转发特性。

2. ZCU216时钟结构及可行的时钟设计方案。

3. 在Vivado中创建基于IP集成器(IP Integrator)的设计。

4. 在Vitis中创建基于ARM的BareMetal程序设计。

5. 代码简要分析。

6. 硬件环境及测试结果。

本文用于示例的软件工具、驱动版本、硬件版本及文档版本如下:

1. ZCU216 Rev-A02(Engineer Sample)

2. CLK104

3. Vivado 2021.2 + Vitis 2021.2

4. PG269 V2.6 October 27, 2021

5. Software Driver: rfdc v11.0

1. 第三代RFSoC 器件时钟转发特性:

RFSoC在芯片内集成了数据转换器,第三代RFSoC系列器件均包含4个ADC Tile和4个DAC Tile,每个ADC和DAC Tile内可能包含1个(ZU43DR)或2个(ZU47DR/48DR)或者4个(ZU49DR)Channel,这取决于芯片型号。以ZCU216开发板上的芯片为例,ZU49DR的每个ADC Tile内包含4路ADC,每个DAC Tile内包含4路DAC。

每个Tile都可以独立配置,工作在不同的采样时钟频率上,采样时钟可以来自于外部高频时钟输入,可以来自于每个Tile内部PLL倍频后的时钟,也可以来自于其他Tile分发的参考时钟。

第三代RFSoC器件相比之前几代产品引入了时钟转发特性,不再需要为每个Tile都提供独立的采样时钟,节省了引脚数量,降低了外围电路的复杂度。

时钟转发的方式共分为两种,一种是参考时钟转发,一种是采样时钟转发。

所谓参考时钟转发,是指外部时钟芯片提供低噪声低频时钟到一个ADC/DAC Tile的专用时钟管脚,该时钟将在Tile间转发,通过每个Tile内的PLL倍频出所需的采样时钟;

而采样时钟转发有两种途径,一是从外部时钟芯片直接提供低噪声高频的采样时钟到一个ADC/DAC Tile的专用时钟管脚,采样时钟将在Tile间分发,无需通过内部PLL倍频,直接提供给ADC/DAC Channel作为采样时钟;

时钟芯片提供低噪声低频时钟到一个ADC/DAC Tile的专用时钟管脚,该时钟在此Tile内通过PLL倍频到采样频率,随后将此采样时钟在Tile间分发。

以上仅为时钟分发方式的简化解释,会有一些使用的限制和建议,建议用户参考PG269 Chapter 4 Clocking-On-chip Clock Distribution章节阅读。

用户也可以打开Vivado,选择器件型号后在RF Data Converter IP内根据原理图和目标设计进行配置,如果时钟设计存在问题,工具会给予一定的报警和提示。

值得注意的是,RF Data Converter IP内的选项和上述的两种分发方式不是完全匹配的。当使用采样时钟分发方式时,在IP内需要勾选的是Input Refclk。ADC Tile 1(Tile 225)和DAC Tile 1(Tile 229)作为采样时钟输入源,其他的ADC和DAC Tile选择Tile 1作为时钟源。

2. ZCU216时钟结构及可行的时钟设计方案:

本节仅覆盖ZCU216开发板与RF数据转换器相关的时钟部分,这部分时钟均由扩展子卡CLK104提供。

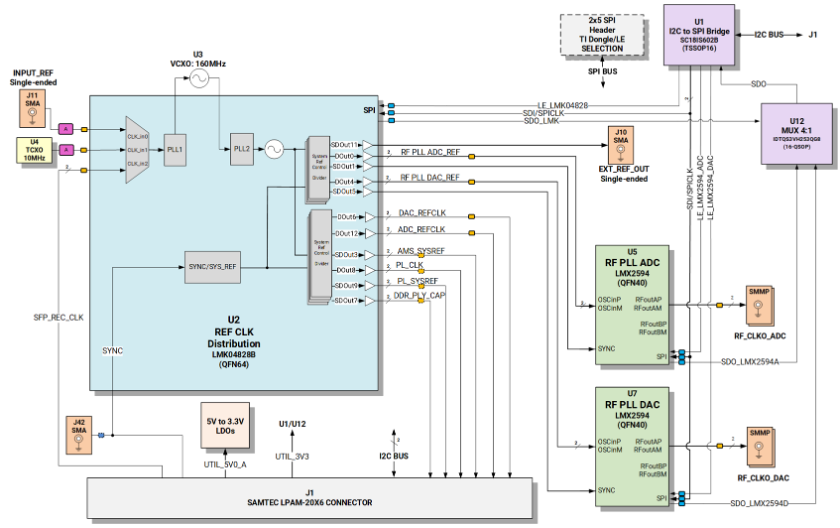

如下所示为CLK104板上的功能示意图:

通过一个时钟芯片为DAC提供接近10GSPS的低噪声采样时钟是很难实现的,CLK104板采用两级PLL方案。

第一级LMK04828B是一个双环路抖动清除器和时钟发生器,一级回路的参考输入可为板上的10MHz TCXO、外部参考时钟(比如从SMA100B输出低噪声时钟),或SFP恢复时钟。二级回路的参考输入为板上的160MHz VCXO,可输出低相噪的时钟、同步信号。其中DAC_REFCLK和ADC_REFCLK可作为ADC/DAC低频参考时钟输入;PL_CLK,AMS_SYSREF和PL_SYSREF均用作MTS(Multi-Tile Synchronization)应用,我们将在未来博客中详细描述MTS相关应用;

第二级LMX2594接收第一级输出时钟,将其倍频到采样频率,直接输出到ADC/DAC Tile。

这三颗时钟芯片均由SPI接口控制,板上有一颗IIC to SPI桥接芯片,FPGA通过IIC接口对此转换芯片进行控制,进而控制三颗时钟芯片。除此以外还有一种更为简单的方式,ZCU216板上带有一颗TI的MSP430 MCU,其IIC接口通过IIC Switch也可以连接到这几颗时钟IC上,用户可以参考XTP580,使用BoardUI实现对时钟的配置。

ZCU216上的芯片型号为ZU49DR,其4个ADC Tile和4个DAC Tile都有专用的模拟时钟输入管脚,但只有两个ADC Tile(Bank 225/226)和两个DAC Tile(Bank 229/230)的时钟管脚被引出。如下表所示为详细连接关系:

本文后续将会展示以下的时钟方案配置:

使用LMX2594输出高频采样时钟分发方式,从ADC Tile1和DAC Tile1输入。设定ADC 采样频率为2000MHz,DAC采样频率为6400MHz。

3. 在Vivado中创建基于IP集成器

(IP Integrator)的设计

本节需要读者对基于Vivado的IPI设计比较熟悉,将不会对较简单的操作步骤进行详述。如何使用此Blog提供的TCL文件重建Vivado工程请参考附录。

Ø 打开Vivado 2021.2,新建工程,名为rfsoc_zcu216_clocking。

Ø 选择板卡ZCU216 EVB或ZCU216 ES EVB,根据板卡型号决定,二者bitstream不兼容。

Ø 在工程界面内创建Block Design,默认名为design_1。

Ø添加Zynq UltraScale+ MPSoC IP,Run Block automation,使用板卡默认配置。

Ø 修改Zynq配置,PS-PL Configuration界面下将AXI HPM0/1 FPD接口关闭,勾选AXI HPM0 LPD,其他保持默认。

Ø 添加Zynq UltraScale+ RF Data Converter IP。

Ø 修改RF Data Converter配置。

1. 切换Converter Setup为Advanced模式。

2. 使能全部ADC和DAC的每个Channel,其他所有配置大多数都是可以通过API修改的,保持默认即可,后续将会介绍如何通过API修改。

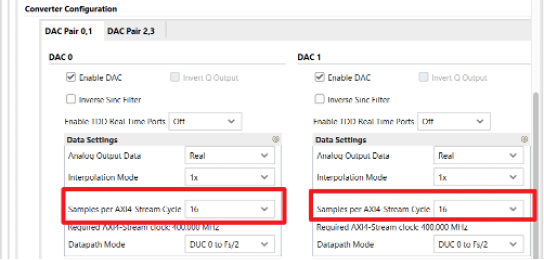

3. 修改全部ADC的Samples per AXI4-Stream Cycle为8,DAC为16,这是为了避免AXI-Stream接口时钟频率超出器件频率上限。

4.在System Clocking界面按下图配置,如上一节所示,我们将先按ADC 2GSPS,DAC 6.4GSPS进行配置,使用采样时钟分发方式。IP的输出时钟可以用于倍频产生AXI4-Stream数据接口的时钟,因此我们先保持和Fabric clock 频率8分频的关系进行配置。

5. Advanced界面保持默认,无需勾选。

Ø Run Block Automation,将RFDC IP AXI-Lite接口通过Interconnect连接到Zynq LPD接口实现地址映射。

Ø 为AXI4-Stream接口提供合适的时钟和复位。

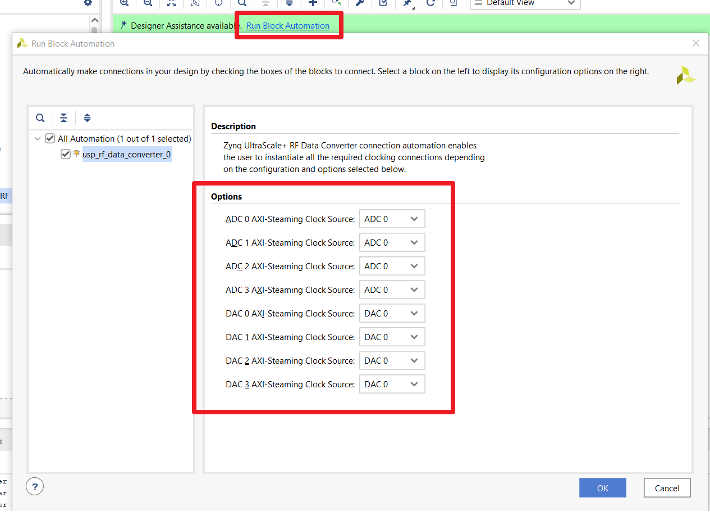

1. 点击BD界面上方Run Block Automation。

2. 由于所有ADC/DAC采样率是一致的,可以使用一个MMCM产生ADC/DAC所需的数字时钟。在弹出界面中勾选ADC 0-3的时钟源为ADC0,DAC0-3的时钟源为DAC0。

3. 工具将会自动例化两个Clocking Wizard IP,adc0_clk_wiz使用IP输出的31.25MHz的时钟作为输入,倍频输出200MHz时钟供给Master接口。Dac0_clk_wiz使用IP输出的50MHz时钟作为输入,倍频输出400MHz时钟供给给Slave接口。

4. 修改clocking wizard复位极性为低电平有效。

5.例化两个Processor System Reset IP,并连接peripheral_aresetn到RFDC IP的s/m_axis_aresetn管脚上。其中Slave AXI-Stream接口是DAC的数字接口,Master AXI-Stream是ADC的数字接口。

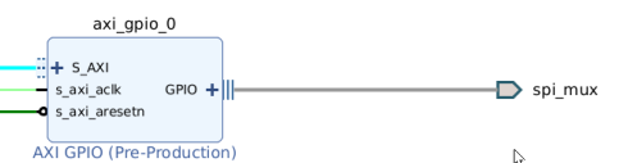

6. 例化一个AXI GPIO IP,用于控制时钟板CLK104上的SPI SDO选通。设定为输出,位宽为2,初始值设定为0x0。

7. 引出AXI GPIO IP,命名为spi_mux。

Ø 完整的Block Design大致如下:

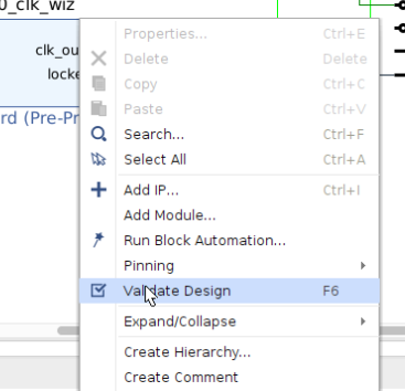

Ø 在BD中右键Validate design,确保没有报错。

Ø 创建顶层文件,右键BD,Create HDL Wrapper,选择Let Vivado manage wrapper and auto-update。

Ø 添加管脚约束,RFDC相关管脚为专有管脚,IP内包含管脚约束,用户无需为此添加。

Ø 生成bitstream,检查工程是否有时序违例。

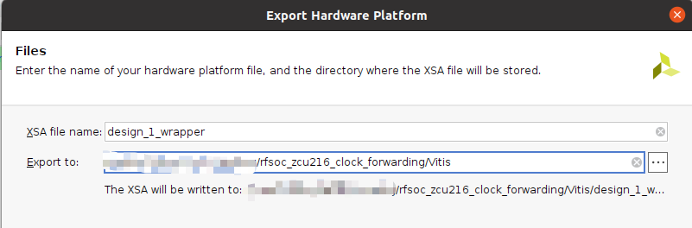

Ø 导出工程XSA文件,File-Export-Export Hardware,勾选Include Bitstream,选择导出目录。

更多文章详情请关注

第三代Zynq RFSoC器件射频数据转换器应用: 时钟设计-下