半导体行业已经花了十多年的时间来准备使用极紫外 (EUV) 光刻技术生产芯片所需的一切,目前看起来,要达到下一个高水平阶段——具有高数值孔径(NA)的 EUV 所需的时间要少得多。

需要更高的分辨率

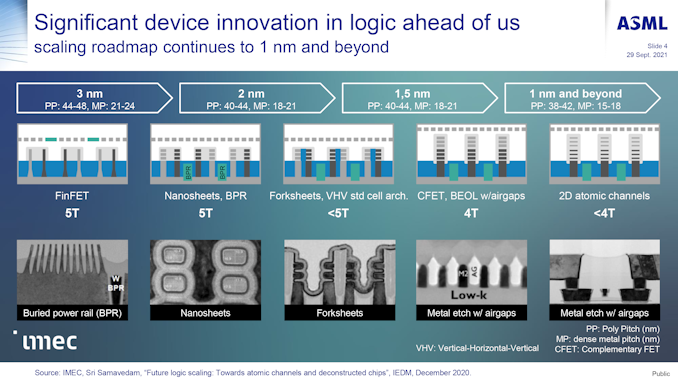

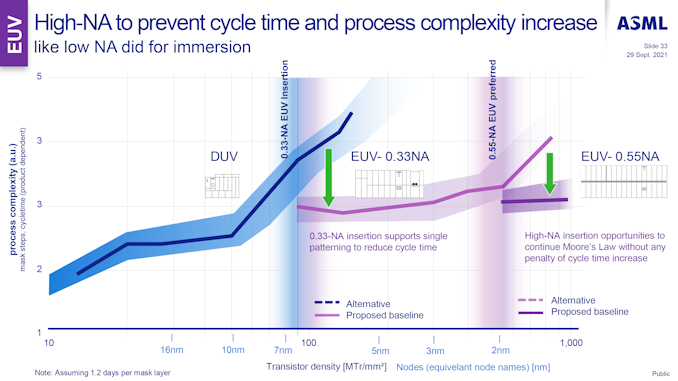

需要更高的分辨率如今,最先进的芯片采用 5/4nm级工艺制造,使用ASML的EUV光刻Twinscan NXE:3400C(或类似)系统,具有 0.33 数值孔径光学器件,可提供 13 nm 分辨率,该分辨率对于7/6 nm节点(间距为 36 nm ~ 38 nm)和 5nm节点(间距为 30 nm ~ 32 nm)的单模式方法来说已经足够好了。但随着间距低于 30 nm(超过 5 nm 节点),13 nm 分辨率可能需要双光刻曝光,这将在未来几年内使用。

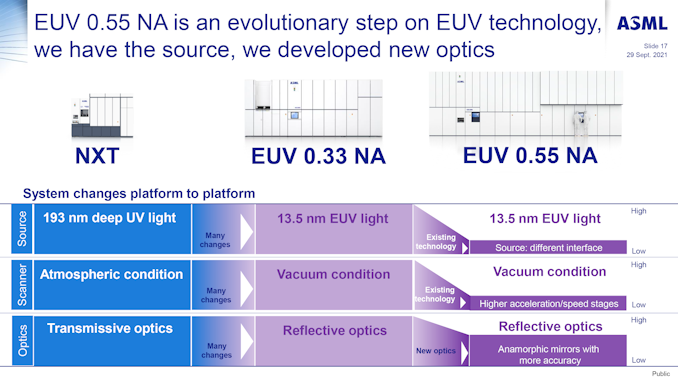

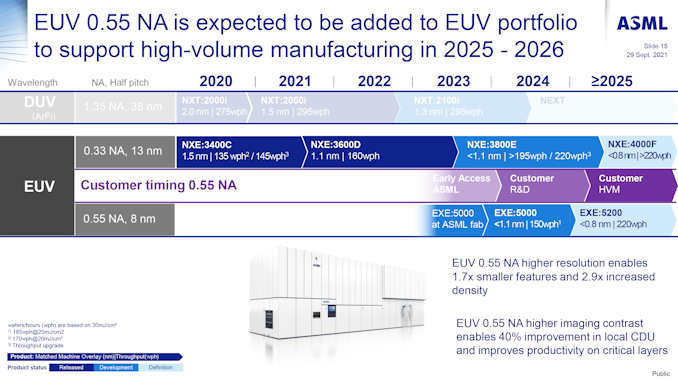

对于后 3nm 节点,ASML 及其合作伙伴正在开发一种全新的 EUV 工具——Twinscan EXE:5000 系列——具有 0.55 NA(高 NA)镜头,能够实现 8nm 分辨率。新的高 NA 扫描仪仍在开发中,预计它们将非常复杂、非常大且价格昂贵——每台的成本将超过 4 亿美元。高数值孔径不仅需要新的光学器件,还需要新的光源,甚至需要新的晶圆厂大楼来容纳更大的机器,这将需要大量投资。

但为了保持半导体的性能、功率、面积和成本 (PPAc),领先的逻辑芯片和存储设备制造商愿意采用新技术,而高 NA EUV 扫描仪对于后 3nm节点至关重要。因此,相关厂商对高 NA 工具的需求非常高。

将交付10至20个高NA系统

将交付10至20个高NA系统几周前,ASML 透露 该公司在2022年第一季度收到了多份来自逻辑芯片和 DRAM 客户的高 NA Twinscan EXE:5200 系统(EUV 0.55 NA)订单。据路透社报道,上周ASML澄清说,它有五份定于 2024 年交付的高 NA 扫描仪订单,以及从 2025 年开始交付的具有更高生产力的后续型号的“超过五份”订单 。

有趣的是,早在 2020 年到 2021 年,ASML 就表示已经收到了三个客户的高NA订单,总共多达 12 个系统。逻辑芯片制造商通常是最先采用尖端设备的,因此可以肯定的是,英特尔、三星和台积电承诺在 2020 至 2021 年获得预生产的高 NA 扫描仪。此外,ASML 已经开始构建第一个 高NA系统,该系统将于 2023 年完成,并将供 Imec 和 ASML 客户用于研发目的。

“在高 NA EUV 方面,我们正在取得良好进展,目前已经开始在我们位于 Veldhoven 的新洁净室中集成第一个高 NA 系统,”ASML首席执行官 Peter Wennink说。“我们在第一季度收到了多个 EXE:5200 系统订单。本月,也就是 4 月,我们还收到了额外的 EXE:5200 订单。通过这些预订,我们现在收到了来自三个逻辑芯片和两个存储器客户的高 NA 订单。EXE:5200是 ASML 的下一代高NA系统。”

ASML 的 Twinscan EXE:5200 比常规 Twinscan NXE:3400C复杂得多,因此构建这些设备需要更长的时间。该公司希望在未来中期能够交付多达 20 台高NA系统,这可能意味着其客户将不得不为这些设备展开竞争。

“我们还在与我们的供应链合作伙伴讨论,以确保在中期内拥有约 20 个 EUV 0.55NA 系统的产能,”Wennink 说。

英特尔率先采用预生产设备

英特尔率先采用预生产设备到目前为止,唯一确认使用ASML高NA设备的工艺技术是英特尔的18A制程节点,该节点曾计划在 2025 年进入量产,大约是 ASML 开始交付其生产的高NA EUV 系统的时间。但最近英特尔将 18A 生产的开始时间推迟到 2024 年下半年,并表示可以使用 ASML 的 Twinscan NXE:3600D 或 NXE:3800E 进行 18A 制造。

虽然英特尔的 18A 技术将极大地受益于高NA EUV设备,但看起来英特尔并不一定需要 Twinscan EXE:5200 机器用于该节点。对商业芯片使用多模式意味着更长的产品周期、更低的生产率、更高的风险和潜在的更低产量。然而,看起来英特尔希望其 18A 节点尽快推出,可能是因为它认为这是一个重要砝码,可以让它从台积电手中夺回制程技术的领先地位。因此,如果设备按时完成,英特尔现在的更新计划是在 18A 的生命周期内逐步采用高NA设备。

当然,将 0.33 NA EUV 扫描仪用于 18A 是否能为英特尔和英特尔代工服务的客户提供足够的生产力还有待观察。但是,至少在 2024 年,英特尔别无选择,只能使用它已有的设备。

其他领先的半导体制造商——台积电、三星、SK 海力士和美光——也将不可避免地采用高NA EUV进行芯片的大批量制造。唯一的问题是,这究竟什么时候发生?

*声明:本文系原作者创作。文章内容系其个人观点,我方转载仅为分享与讨论,不代表我方赞成或认同,如有异议,请联系后台。