在传统的计算机内存层次结构中,NAND闪存位于离CPU最远的位置,与静态随机存取存储器(SRAM)和动态随机存取存储器(DRAM)相比,它相对成本便宜、传输速度慢。

闪存领域的重要性体现在其在全球半导体资本支出中约占三分之一的可观份额。它的成功与其不断扩展存储密度和成本的能力有关,这也是NAND闪存技术发展的主要驱动力。大约每两年,NAND闪存行业就能够大幅提高位存储密度。

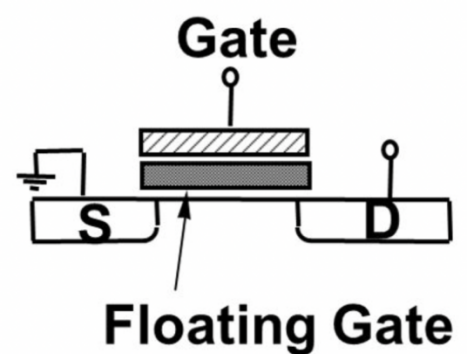

在此过程中,行业也已经引入了多项技术创新来保持这一趋势线。直到近期,NAND闪存单元都以平面配置排列,使用浮栅晶体管进行存储操作。浮栅晶体管由两个栅极组成:浮栅和控制栅。浮栅与晶体管结构的其余部分隔离,通常由多晶硅制成。控制门是普通晶体管门。

浮栅与晶体管结构的其余部分隔离

通过向控制栅极施加脉冲来完成存储单元的写入,该脉冲基于隧道机制迫使电子进入或离开浮栅。电荷的存在与否都会改变晶体管的阈值电压,这种变化称为内存窗口。因此,信息被编码在浮栅晶体管的阈值电压中,并通过测量漏极电流来完成读取。存储在隔离栅极中的电荷长时间保持不变,使存储器具有非易失性特性。

20多年来,浮栅一直是2D NAND的常用方法,尽管其结构相当复杂,但能提供可靠的运行。通过减小浮栅单元的尺寸,可以提高位存储密度。然而,2D NAND缩放在大约15nm 半间距处饱和,主要是因为阵列可靠性和静电干扰问题。

走向3D以降低每比特成本

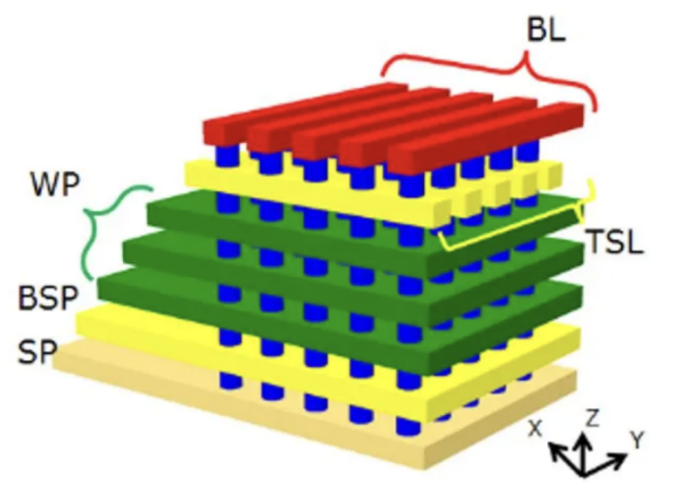

走向3D以降低每比特成本存储密度的进一步提高是通过向第三维的过渡实现的,而不是通过堆叠类似NAND的2D层,因为这样做所需的工艺步骤会大大增加成本。真正的3D NAND的基本思想是将单元堆叠成垂直的串,从而达到更高密度的单位面积。在这种配置中,单元格仍然通过水平字行来寻址。

最常见的制造方法是环栅(GAA)垂直沟道方法,从生长氧化物/氮化物层堆叠开始。接下来,使用先进的干法蚀刻工具通过堆叠向下钻取圆柱形孔。沿孔的侧壁沉积隧道和捕获层。为了完成这个冲孔和堵塞的过程,在孔内沉积一个薄的多晶硅通道,然后是一个核心填充物,形成一个类似通心粉的结构。

下一步,去除氮化物并用字线金属代替。在这些GAA结构中,圆柱形栅极环绕通道结构增强了载流子注入捕获层的能力,从而扩大了编程/擦除窗口。

在典型3D NAND闪存结构中,BL=位线,WP =字板,

BSP=底部选择板,SP=源极板和TSL=顶部选择线

通过增加更多的层而不是缩小特征尺寸,NAND闪存行业放弃了传统的缩放方式。第一个商业3D NAND产品于2013年推出,堆栈数为24字线层(128GB)。根据供应商的不同,结构存在变化,被称为V-NAND和BICS等不同名称。

因此,3D NAND是第一个也是唯一一个将真正的3D产品推向市场的技术。在接下来的几年里,为了保持比特密度的变化趋势,更多的层被叠加在一起。最近,一些主要公司推出了基于232层3D NAND的产品,预计这种增加层数的趋势将在未来几年持续下去。

从浮栅到电荷陷阱

从浮栅到电荷陷阱在研发过程中,为了促进具有挑战性的3D工艺或进一步增加位密度,还采用了其他创新措施。例如增加位密度:每个单元最多增加4位,这是NAND闪存技术的真正资产。以4位为例,足够大的存储窗口可以激活多级电池,支持每个晶体管中使用16个独立的电荷水平。

另一个创新是用电荷陷阱单元代替浮栅单元,这意味着更简化的工艺流程。两种电池的工作原理相对相似,但在电荷捕获电池中,捕获层是绝缘体,通常是氮化硅,它在相邻电池之间提供较少的静电干扰。这种电荷陷阱单元现在是大多数3D NAND结构的基础。

提高位存储密度

提高位存储密度为了维持NAND闪存路线图,一些主要厂商最近宣布将层数增加到至少500层。按照趋势线,这一数字将在十年内增加到1000人。增加层数会带来更高的处理复杂性,它挑战了沉积和蚀刻工艺,并导致应力在层内积聚。为了应对挑战,NAND闪存制造商最近开始将层数拆分为至少两层,并将单独处理的层堆叠在彼此之上。

然而,人们担心如果没有重大创新,这种演变将逐渐降低NAND闪存产品的成本效率。层数的增加需要投资高度先进的沉积和腐蚀工具。多层叠加的趋势将大大增加掩模的数量、处理步骤和时间。它还可能导致存储路线图的速度变慢,因为1000层的堆栈直到2030年都不可用。

随着层数的增加,由于图案化和应力原因导致缩小层厚度和控制堆叠高度的压力。这种Z间距缩放降低了堆叠中所有材料的高度,包括字线金属和氧化物。

Z间距缩放

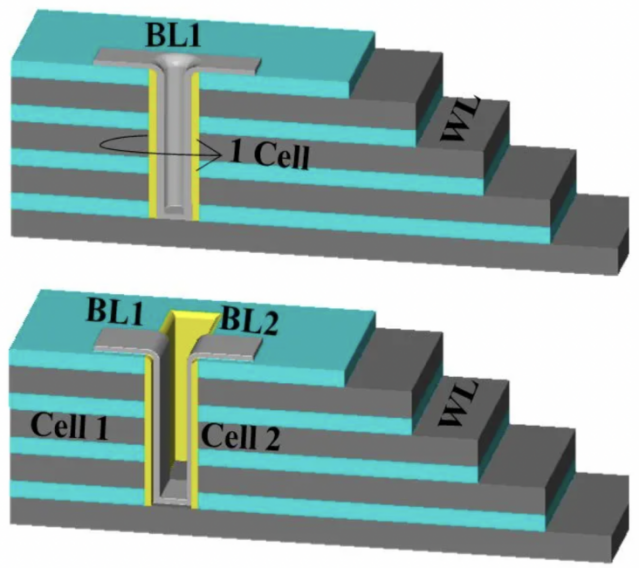

Z间距缩放Z间距的缩放可能会通过进一步减少x-y尺寸来补充。在3D NAND的发展过程中,需要在存储单元上进行重大创新,这一点一直没有改变。因此,正在探索新的材料和电池结构作为GAA NAND闪存电池的替代品。

在发展过程中,值得关注的是连接晶体管的沟槽状结构。在这种体系结构中,存储单元不再是循环的。它们是在沟槽的侧壁实现的,沟槽两端的两个晶体管增加了位密度。从操作的角度来看,与圆形GAA NAND闪存电池相比,沟槽电池类似于平面单元电池。

尽管它在电气特性上有一点缺陷(比如程序/擦除窗口),但沟槽状结构的单位电池面积在x-y方向上可以比“GAA”电池减少。因此,沟槽电池被提出作为下一代NAND闪存电池架构,有望将x-y间距从今天的140nm降低到约30nm。

环栅架构(顶部)与沟槽NAND闪存单元架构(底部)的比较

*声明:本文系原作者创作。文章内容系其个人观点,我方转载仅为分享与讨论,不代表我方赞成或认同,如有异议,请联系后台。