RISC-V,这一CPU界的名校生,自出世以来就备受关注,如今基于RISC-V的处理器于雨后春笋般被推出。为了更多人参与RISC-V的设计,RISC-V基金会每年都会举办面向全球工程师的Soft CPU设计比赛,去年美国加州圣地亚哥的华人工程师Changyi Gu荣获冠军!这是他前年参加比赛获得季军后再夺桂冠!Changyi 也是我们硬禾的老朋友,在苏老师的盛情邀请下,他开源的8051核 - FP51-T,以及去年RISC-V比赛的获奖作品 - Reindeer都完美移植到了小脚丫FPGA上。Reindeer RISC-V软核设计精巧,性能强劲,工具完善,代码和资料全开源,用户可以自由扩展外设,还可以使用开源硬件领域最火爆的Arduino IDE开发程序,对新手来说非常友好。

清华出版社还邀请顾先生出版了这本《基于FPGA与RISC-V的嵌入式系统设计》,本书详细介绍了RISC-V指令集和其背后的设计思想,并在此基础上引入了一种称为FARM的软硬件开发模式,将FPGA同RISC-V CPU软核相结合,并利用Arduino与Make作为软件快速开发工具,有效地提高了开发效率,使系统设计具有更好的通用性和可移植性。

本书内容既有深度,亦有广度,对各类从事软硬件开发的科技人员会有很大的参考价值。对高校相关专业的学生,本书也是一部很好的教学资料(了解详情扫描下面的二维码)。

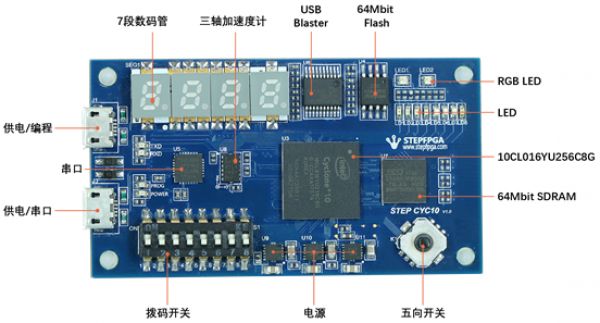

除了上述有关软、硬件的讨论之外,本书的作者还与硬禾的小脚丫FPGA的团队进行了合作,成功地将书中的大部分内容移植到了小脚丫FPGA旗下的STEP CYC10开发板上,并将相关的技术细节在书中做了详细陈述,以方便读者的动手实践。

RISC-V相关资源

小脚丫STEP-CYC10 是一款基于Intel Cyclone10设计的FPGA开发板。板卡尺寸只有72mm×40mm。核心FPGA芯片选用了Intel公司Cyclone 10 LP系列的10CL016YU256C8G,相比于前一代的Cyclone IV系列的FPGA,它的性能更强,功耗更低,板上的FPGA芯片资源达16000逻辑单元(LEs),同时该板卡最高支持10CL025YU256芯片。另外,板卡上集成了USB Blaster编程器、SDRAM、FLASH等多种外设。板上预留了PCIE子卡插座,你可以方便的进行扩展。除了大容量资源之外,板上集成了SDRAM,非常适合RISC-V软核处理器的移植学习。

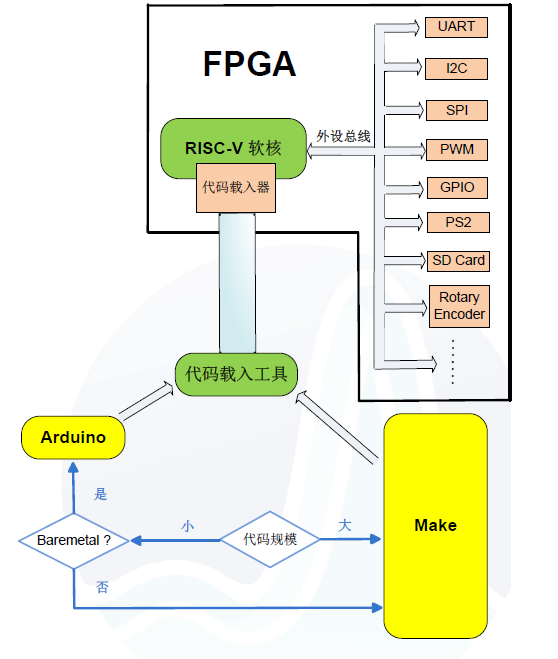

经过美国PulseRain Technology与小脚丫团队的不懈努力,在小脚丫Cyclone10开发板上成功移植了PulseRain Reindeer RISC-V 软核,并且开发了配套Arduino IDE的板子支持包,使得用户可以通过Arduino开发环境直接对嵌入到FPGA中的RISC-V软核进行编程。FPGA优秀的性价比和灵活性;开源硬件Arduino及其丰富的软件库;开源的编译器和工具链GNU;再加上如今热度空前的开源处理器RISC-V,形成了一种灵活快速的新型嵌入式开发方式FRAM: FPGA+Arduino+RISC-V+Make。 如上图所示,在FARM开发模式下,FPGA成为系统的核心芯片。在FPGA中会包含一个支持RISC-V的开源处理器软核 (RISC-V Soft CPU)。该处理器可以包含一个硬件逻辑实现的代码载入器 (Hardware Based Code Loader)。FPGA也会包含所有的(或大部分的)外部设备实现,这些外部设备和RISC-V通过总线相连。对于无法完全用FPGA实现的功能 (例如传感器),FPGA也会实现其控制部分或者数据的读写。

如上图所示,在FARM开发模式下,FPGA成为系统的核心芯片。在FPGA中会包含一个支持RISC-V的开源处理器软核 (RISC-V Soft CPU)。该处理器可以包含一个硬件逻辑实现的代码载入器 (Hardware Based Code Loader)。FPGA也会包含所有的(或大部分的)外部设备实现,这些外部设备和RISC-V通过总线相连。对于无法完全用FPGA实现的功能 (例如传感器),FPGA也会实现其控制部分或者数据的读写。

上图中RISC-V 软核的编程,可以通过两种方式。

对中小型的裸金属 (bare metal)系统,开发者可以直接在Arduino 集成开发环境下编程,并充分利用Arduino提供的软件支持库。编译结果也可以在集成环境下直接写入到FPGA上的RISC-V软核里。

当软件规模变大时,软件的配置和编译可以通过Make来实现,并执行和RISC-V软核配套的代码载入工具,下载编译结果。

方式一:使用Arduino IDE开发RISC-V处理器

方式二:使用make配置编译RISC-V应用程序

为此本书的作者 - 全球Soft CPU大奖赛冠军顾长怡专门录制了近一个小时的视频,详细介绍了在FPGA里移植RISC-V软核的方法。

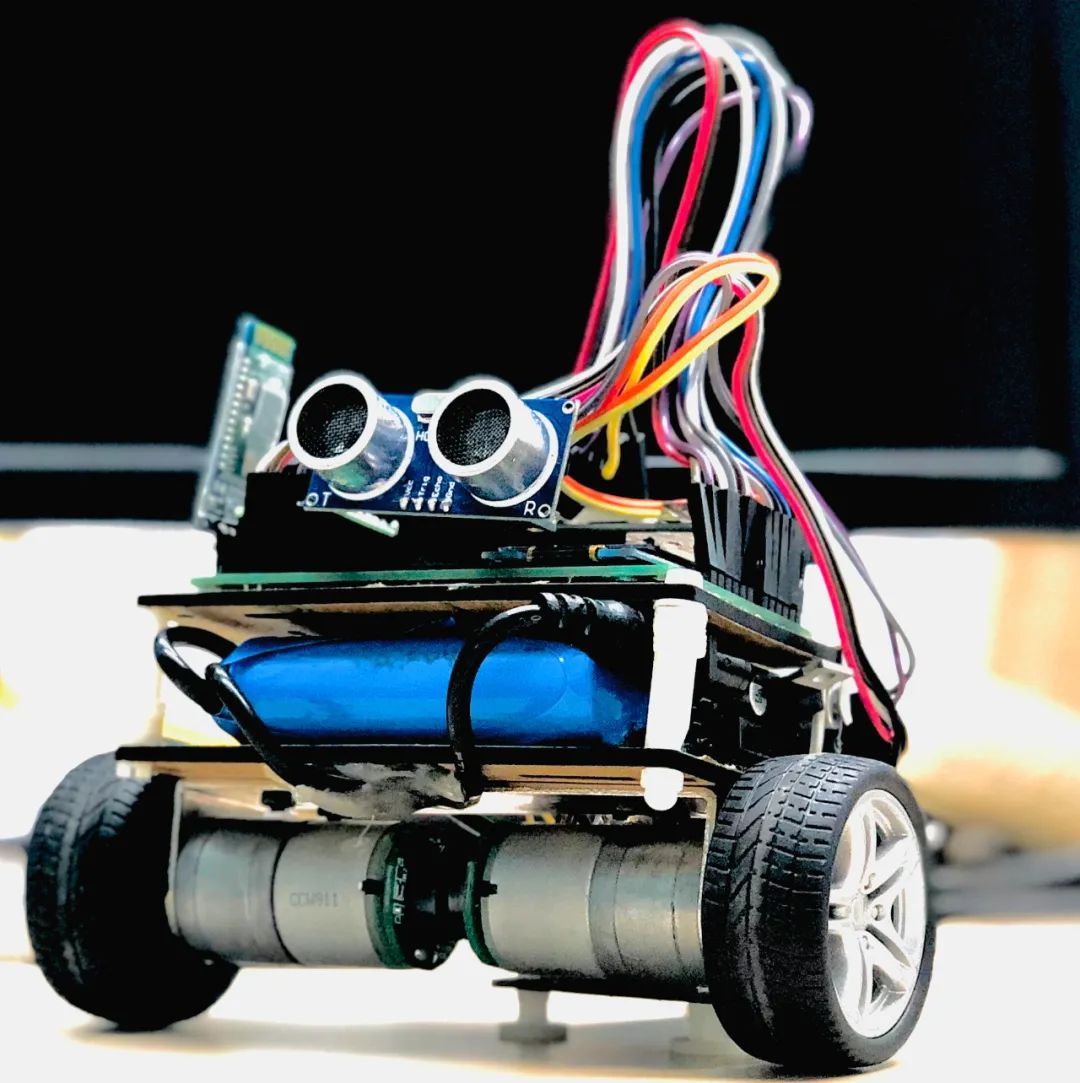

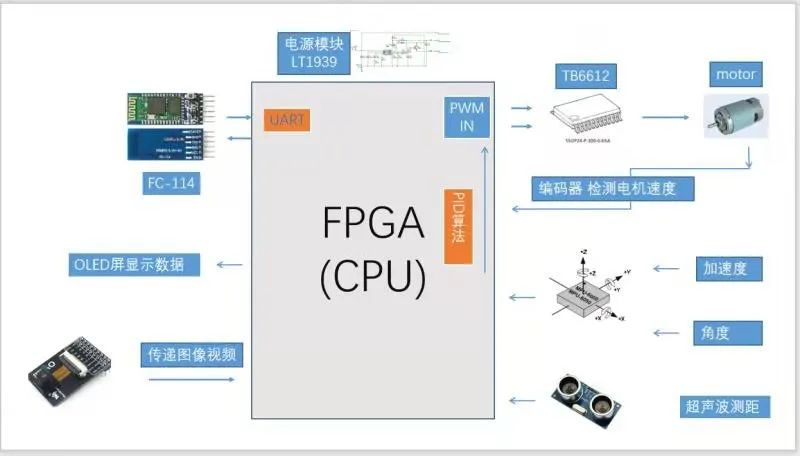

硬禾实战营的4位学员在2019年暑期历时一个月时间,从无到有打造了一款基于RISC-V(跑在我们的小脚丫FPGA上)的避障平衡车,如下图:

避障平衡车的实物图片

避障平衡车的功能构成

此项目所有的设计文档及相应的代码都公开在电子森林网站上

三场与RISC-V相关的直播课程:

1 全球Soft CPU大奖赛冠军顾长怡 - 讲述“基于RISC V和FPGA的嵌入式系统设计”

2 法国 GreenWaves Technologies 公司担任首席软件工程师,兼客户项目总监张垚 - 讲述“基于RISC-V的多核并行架构与边缘计算”

3 国内FPGA龙头企业上海安路信息科技的资深工程师吴文强 - 讲述“基于FPGA的RISC-V软核”

下面是RISC-V教程和配套FPGA学习平台的链接,限时优惠。