什么叫Dual-port测试方法?

Dual-Port在最新Gen5中被移除?

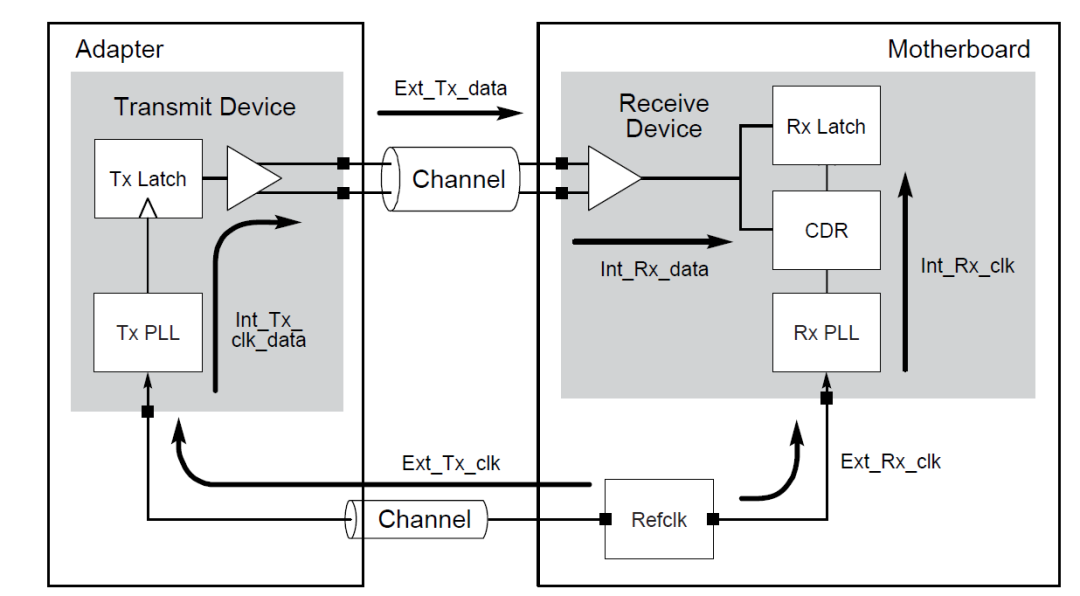

PCIe Gen2 CDR能力有限,对于33KHz-2MHz范围内的低频抖动 (典型例子就是SSC扩频时钟)的抑制能力很弱。对于带SSC的System待测物,需要将数据和时钟同时捕获、互相参考才能得到准确的测量结果。而到了Gen5,无论是Common Clock还是SRIS架构都可以很好的抑制低频抖动,不再需要参考System提供的100MHz时钟。

PCIe2 Gen2的时钟规范是很宽松的,其抖动有效值小于3.1ps即可。如果System提供的100MHz参考时钟较差,数据参考时钟后测出的眼图和抖动也会较差,因此在评估Data信号质量时同时采集并对齐100MHz参考时钟就很有必要。而到了Gen5,对Clock的品质要求大大提高,时钟抖动有效值要求低至0.15ps,近乎理想时钟。数据眼图和抖动测量时使用参考时钟或使用软件算法时钟已经没有什么区别了,只需对时钟进行单独的测量以确保其品质就可以了。

泰克PCIe物理层规范测试方案