上期话题

揭秘!百兆赫兹的电源去耦如何hold住Gbps的高速信号

(戳标题,即可查看上期文章回顾)

各位在PDN去耦设计过程中都遇到过什么样的“无理要求”?不妨分享。

本意是想借着问题让大家分享一些PDN去耦的设计经验,没料到留言栏变成了Layout攻城狮对硬件攻城狮的吐槽大会。

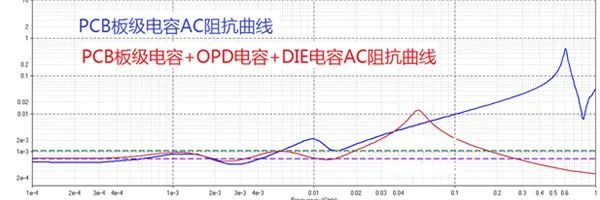

纵观大家的“血泪史”,似乎大部分槽点都集中在BGA区域的电容数量增加及该区域的较大封装电容强行布局给设计带来的难度上,不过也要体谅硬件攻城狮,他们的处境也很尴尬:板子跑起来了,自己没啥存在感;万一板子跑不起来,基本都是背锅侠了,所以恨不得照着DEMO板全盘拷贝,少加一个小电容内心都要斗争老半天,其实,完全没必要这么纠结,前提是对PDN去耦设计的原理要有足够的了解,还不太了解的可以戳这里《电源专题之AC阻抗》

另外还有些网友问到了信号完整性(SI)与电源完整性(PI)协同仿真的问题,作为近两年DesignCon论文的热点话题之一,高速先生对此也在持续关注中,如果遇到典型的案例,也一定会尽快与各位分享。

(以下内容选自部分网友答题)

1.要求吧0603 0805的电容放到主芯片bga下,一般都是只能放0402或者0201的

2.要求曲线看到每1MHz的变化,我太难了

@ moody

评分:3分

去耦电容的位置其实很有讲究的,一般要考虑去耦半径,容值越小越要靠近芯片管脚,不同容值电容均匀分布啊等等。容值数量和位置都是要经过仿真优化的,遇到老想随意加一个减一个随便挪位置的要求,其实里面有玄机,哪能随意!

@ 杆

评分:3分

有的画原理图的人喜欢把电阻或磁珠放在靠近电源芯片端,电阻的另外一端再放一堆电容。

@ 涌

评分:3分

无理的要求主要来源于硬件工程师的甩锅,比如:纹波大就无限加电容,不管有没有空间;一个负载芯片引脚要求放置很多个电容;bga芯片下方要求放大电容

@ 欧阳

评分:3分

1.硬件要求主芯片bga下方的电容跟demo一模一样,不多不少;

2.要求吧0603 0805的电容放到主芯片bga下

@ Ben

评分:3分

1.目前所接触的画图,客户要求PDN阻抗管控到20MHz,一般几颗1uF/0.1uF电容就能满足要求。不同的尺寸封装,摆放位置对PDN有一定影响。2.为了应对可能出现的信号干扰,客户会要求增加一些pF级的电容和小封装的磁珠。3,评估打样阶段,线路板的空间有限,有时按照1、2要求摆不下,问客户有没有可以删减的元件或过孔,得到的回复是每个都非常非常重要。只得要求结构再次增加尺寸。4.大尺寸的电容容量大,但高度也高。结构设计有困难,只能把大封装改为两个小封装,容量的和不变。这个文字上简单的描述,需要寻找之前量产产品上这样的设计,经过测试,结果良好,客户才同意拆分。

@ 山水江南

评分:3分

最近正好在做PDN,一些困惑解决了。曲线的开始,几Hz的阻抗很大,怎么设置VRM让它降下来?

@ SG

评分:3分

那仿真的时候如何加入PDN的影响呢?板级的不需要加,芯片级怎么加呢?Ibis模型中已经包含了吗?还是芯片厂提供片上Pdn信息仿真中高频部分就不需要加入板级PDN参数了吗?

@ 咚咚

评分:3分

2020积分排行榜,输入关键词:2020积分排行

2019年积分以及兑换礼品说明如下:

查看我的积分,回复关键词“2019积分”;

看看我能兑换什么礼物,回复关键词“积分商城”;

————你可能错过的往期干货————

揭秘!百兆赫兹的电源去耦如何hold住Gbps的高速信号

宝藏文,高速先生所有原创技术文章,戳戳戳!