FC技术发明并发展的过程中,陶瓷基板一直在其中扮演着重要角色。但是,陶瓷基板成本较高。为了降低成本,近年来人们致力于提高传统低成本层压有机封装基板的性能,使用的方法包括研发多层层压基板、消除基板核心等。在FC的三维封装发展中,还应用到硅基板。

1、陶瓷基板

陶瓷基板是指将Cu箔在高温下直接键合到陶瓷基片表面上的特殊工艺板,可像印制电路板(Printed Circuit Board,PCB)板一样能刻蚀出各种图形,而且所制成的超薄复合基板具有良好的电绝缘性能、高导热特性和高附着强度。

因此,陶瓷基板已成为大功率电子电路结构技术和互连技术的基础材料。Al2O3是最常用的陶瓷基板材料,具有优良的机械、热、电性能和化学稳定性,而且原料来源丰富,适用于各种各样的制造技术及不同的形状。

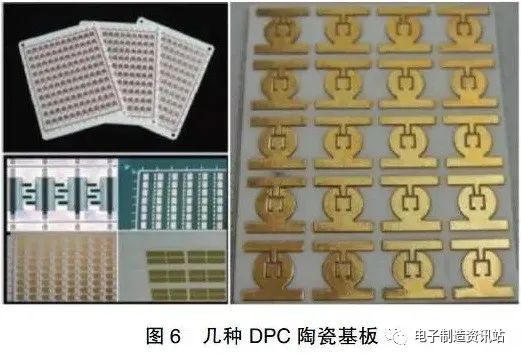

随着元器件尺寸的减小、产品精度要求的提高,直接镀铜陶瓷基板(Direct Plated Ceramic,DPC)成为陶瓷基板发展的一个主要方向。

DPC技术采用薄膜工艺,利用真空溅射、光刻等工艺在陶瓷基底上制作线路,使基板线路更加精确。DPC 制备工艺温度较低,一定程度上避免了高温对于材料所造成的破坏或尺寸变异等现象,也减小了基板的制备成本。

一般在金属线路深宽比为 1:1 的前提下,DPC金属线路的线径宽度能够达到10μm ~50μm。图6展示了几种DPC陶瓷基板。

2、有机基板

(1)表面层合电路

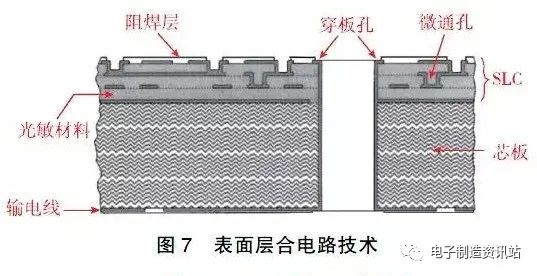

在IBM公司发明SLC技术之前,FC工艺带来的互连密度只有多层陶瓷基板才能提供。SLC基板不仅可以满足FC工艺的要求,而且成本比陶瓷基板便宜的多,还可以通过对Cu导体和低介电常数绝缘材料的使用来获得更好的电气性能。

SLC是当今非常流行的低成本有机封装基板的基础技术,如图7所示,基板上的叠层(Build-up Layer)通过微孔垂直连接以支持FC互连。

SLC技术有芯板和表面层合电路两个主要部分,芯板由普通环氧树脂玻璃板制成,而SLC层则是在芯板的外层逐次增加由光敏环氧树脂制成的介电层及镀Cu的导体层,采用叠层法制成,最终实现多层结构的功能。一般来说,具有12层(2个核心层和10个叠压层)和10μm线宽和间距的叠层基板足以支撑大多数芯片的要求。

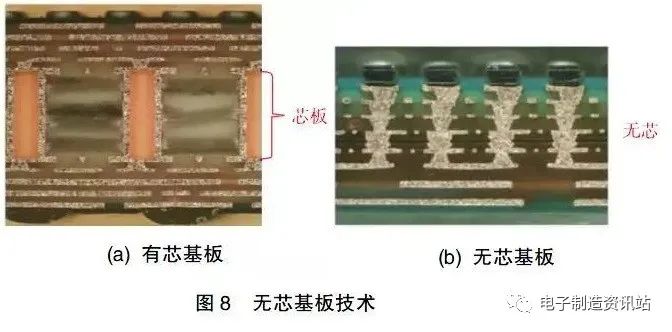

(2)无芯基板

无芯基板的概念最早由富士通于2006年提出,如图8所示。通过叠层层压有机封装基板(图8(a))和有机无芯封装基板(图8(b))之间的比较,可以看出无芯封装基板中没有芯板,基板中只存在堆积层。由于去除了芯板,无芯基板的成本更低、布线能力更高,具有更好的电气性能以及更小的外形尺寸。

但是同时,去除芯板后,无芯基板也面临着更易发生翘曲以及力学性能降低等问题。因此,尽管无芯基板有诸多优点,但是由于热膨胀系数(Coefficient of Thermal Expansion,CTE)不匹配带来的基板翘曲难以控制,无芯基板一直无法得到广泛应用。

3、硅基板

(1)硅通孔转接板

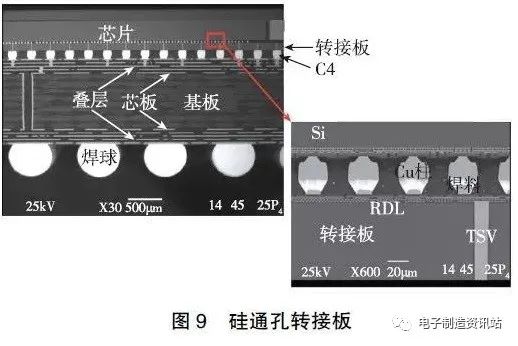

在过去的几年中,人们发现即使是12层的叠层基板也难以支持对于高密度、高I/O数和超细间距的要求。例如现场可编程门阵列(Field Programmable Gate Array,FPGA)芯片,这就需要TSV转接板来进行更精细的布线,满足芯片要求。

图9展示了Xilinx公司与TSMC公司共同研发的FPGA芯片,其中的TSV转接板(厚度100μm)有四层顶部RDL:三层Cu大马士革和一层Al。FPGA芯片之间的10000余个横向互连主要通过转接板上的0.4μm间距RDL进行连接,RDL和钝化层的最小厚度为1μm。每一个FPGA具有超过5万个节距为45μm的微凸点,对应的TSV转接板上有超过20万个微凸点。

TSV转接板的制造流程如下:

①将光刻胶涂覆到裸Si 晶圆上,利用掩膜板经过曝光后确定TSV 孔的位置,并对其进行显影工艺;

②采用激光或深反应离子刻蚀(Deep Reactive Ion Etching,DRIE)工艺刻蚀形成符合设计要求的TSV 孔;

③由于Si 是半导体材料,为了防止TSV 漏电以及TSV间的串扰,必须在TSV 孔壁上制作SiO2 绝缘层,因此需要采用等离子体增强化学气相沉积(Plasma Enhanced Chemical Vapor Deposition,PECVD)的方法将SiO2绝缘层沉积至TSV 孔内壁上;

④为了防止填充材料与SiO2 或Si 之间发生相互扩散,使用PVD方法进行阻挡层的制作,阻挡层的材料一般为Ti、TiN 或Ta;

⑤若在后续TSV 中导电材料填充的过程中使用电镀工艺,则需使用PVD 方法在阻挡层内壁上沉积一层Cu 种子层,这是由于电镀工艺进行的前提条件为结构导电,因此需要在阻挡层表面覆盖一层种子层作为导电层,而最常用的TSV 种子层材料为Cu;

⑥TSV 孔的填充方法不止一种,包括采用电镀方法填充Cu、Ti、Al 或焊料,采用溅射方法填充W,或者采用真空印刷方法填充聚合物等;

⑦在电镀完成后,必然会有多余的导电材料附着于晶圆表面,需要采用化学机械抛光(Chemical Mechanical Polishing,CMP)工艺去除覆盖层;

⑧为了使TSV 达到互连结构的作用,还需要对晶圆进行背面减薄,并采用湿法或干法的工艺将导电材料外露,以便后续结构或器件的连接。在TSV制造完成后,还需要采用电镀等方法在转接板上制作RDL以实现互连。通过以上工艺过程可以看出,TSV的制作流程复杂、工艺成本非常高。

(2)去TSV转接板

为了降低成本、提高电性能、进一步减小封装外形,产业界在近几年掀起了去TSV(TSV-less)的风潮。所谓去TSV转接板,即消除TSV,仅保留Si基板的RDL层以实现互连,这项技术可以帮助转接板减低厚度和工艺成本。

2012年8月,ITRI公司提出可以使用穿硅孔(Through Silicon Hole,TSH)转接板替换TSV转接板。所谓TSH转接板,如图10(a)所示,孔内没有金属化,消除了TSV转接板中的介电层、阻挡层和种子层,也省略了TSV转接板的导电材料填充、CMP以及导电材料外露等工艺过程。

与TSV转接板相比,TSH转接板只需在硅片上通过激光或DRIE刻蚀制造通孔,并在硅片上制作RDL层即可。TSH同样可以起到帮助芯片堆叠的目的,可以让底部芯片的信号通过Cu柱和焊料传输到顶部芯片(反之亦然),同一侧的芯片还可以与TSH转接板的RDL进行通信。所有芯片的底部都需要焊接到TSH转接板上,以保证结构抵抗热学和力学冲击的能力,TSH转接板的底面还具有可连接到封装基板的焊料凸点。

2012年9月,Intel公司提出了嵌入式多芯片连接桥(Embedded Multidie Interconnect Bridge,EMIB)取代TSV转接板的构想。芯片之间的横向通信将由嵌入硅的电桥实现,而电源、接地以及其他信号则通过PCB进行传输,如图10(b)所示。EMIB技术的应用需要克服两个困难,一个是EMIB的制造,另一个是带EMIB基板的制造。

EMIB的制造需要首先在晶圆上构建多层RDL(包括焊盘),然后将减薄晶圆至约60μm,将晶圆的非RDL侧粘接到薄膜上进行划片,划片后得到单独的EMIB结构。

带EMIB基板的制造首先将单独EMIB结构的非RDL侧向下放置在基板腔体中的Cu箔上;然后在整个有机封装基板上层压树脂膜;在环氧树脂表面向下钻孔至EMIC,并向孔内镀Cu以实现基板到EMIB的连接;继续镀Cu以实现基板的横向连接;还可以通过层压、钻孔、镀Cu的方式制作多层层压互连结构;在基板最上层制作焊盘和微凸点,将多个FC芯片倒装至基板,实现芯片之间的横向连接。

2014年,Xilinx公司与SPIL公司共同研发了一种采用了去TSV转接板的FPGA芯片,这种去TSV基板技术被命名为无硅互连技术(Silicon Less Interconnect Technology,SLIT),图10(c)展示了这种新型的封装结构。可以看出,TSV被消除,转接板仅保留了顶部的四层RDL用以实现FPGA芯片的横向通信,转接板厚度大大减低。

SLIT技术中的去TSV转接板基本制造流程如下:

①在裸硅片上通过电镀的方法制造多层RDL;

②将FC芯片对准到晶圆,采用回流焊或者热压键合的方法完成FC键合;

③滴涂底填胶并固化;

④采用EMC对晶圆进行一体成型;

⑤对重构晶圆的表面进行减薄,露出FC芯片背面;

⑥在重构晶圆的表面粘贴加固晶圆,然后对重构晶圆的背面进行减薄;

⑦减薄至最外一层RDL后,采用钝化、光刻、掩模、蚀刻、溅射等一系列工艺构建UBM的粘接层和阻挡层;

⑧电镀Cu润湿层和焊料,回流后形成C4凸点。

2016年,ASE公司提出使用FOWLP技术制造芯片的RDL,如图10(d)所示。扇出封装中FC芯片底部含RDL的转接板亦是一种去TSV转接板,这种方法也被称为扇出晶圆级基板上芯片(Fan Out Wafer-Level Chip-on-Substrate,FOCoS)技术。

|推荐阅读|

© 滤波器 微信公众号