来源 | 电子与信息学报

智库 | 云脑智库(CloudBrain-TT)

云圈 | 进“云脑智库微信群”,请加微信:15881101905,备注您的研究方向

声明 | 本号聚焦相关知识分享,内容观点不代表本号立场,可追溯内容均注明来源,若存在版权等问题,请联系(15881101905,微信同号)删除,谢谢

射频集成电路校准技术综述

李松亭 颜盾

①国防科技大学空天科学学院

②湖南大学信息科学与工程学院

摘要:射频集成电路(RFICs)对工艺偏差、器件失配、器件非线性等引入的静态非理想因素以及温度变化、增益改变、输入/输出频率变动等引入的动态非理想因素所表现出的鲁棒性较差。该文深入挖掘影响射频集成电路性能的关键因素,并对典型的校准算法进行归纳和总结,为高性能射频集成电路设计提供理论支撑。

关键词:射频集成电路;校准技术;射频收发链路;频率综合器;多片同步

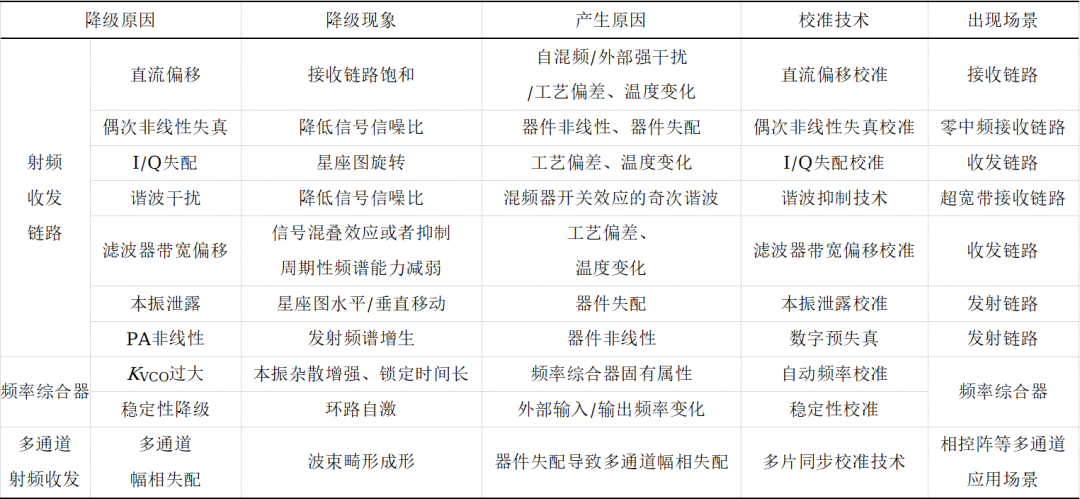

本文主要针对射频集成电路的性能降级机理进行分析,归纳总结能够提升射频集成电路鲁棒性的各类校准技术,为高性能射频集成电路的设计提供坚实的基础理论支撑。具体内容如表1所示。

表1 本文校准技术总结

2.1 直流偏移校准

直流偏移对于射频接收机的设计是一个极为严峻的挑战,直流偏移的产生主要来自于3个方面:

(1)混频器本身的自混频效应;

(2)外部的强干扰在混频器端产生的自混频效应;(3)工艺偏差、温度变化导致的直流偏移。

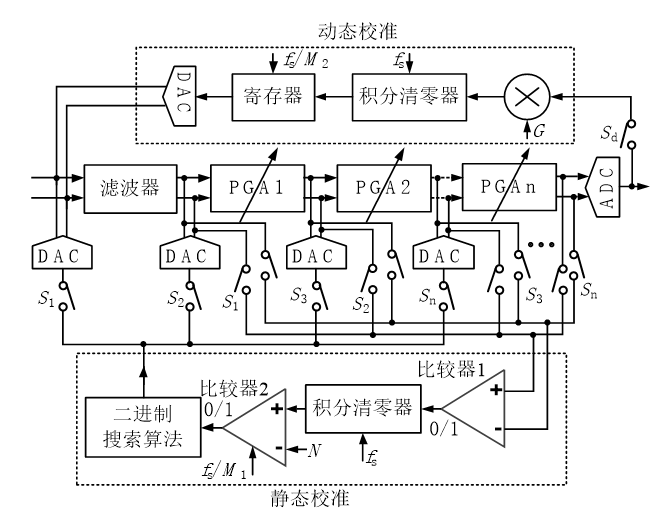

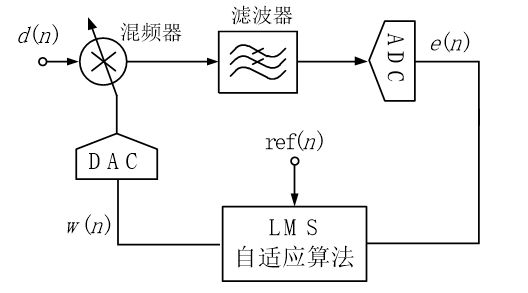

当基带电路增益较大时,直流偏移极易导致射频接收链路的饱和。适用于零中频接收机的DCOC电路如图1所示。

图1 适用于零中频接收机的数字辅助DCOC

2.2 偶次非线性失真校准

最小均方(Least Mean Squares, LMS)自适应校准算法是一种典型的用于补偿偶次非线性失真的自适应校准算法,如图2所示,其中d(n)为实际输入信号(输入有效信号和白噪声的叠加),e(n)为经过偶次非线性失真补偿后的实际输出信号,w(n)为用于校准补偿的1阶抽头系数,ref(n)是与偶次非线性失真严格相关的参考信号。

图2 基于LMS算法的自适应偶次非线性失真校准电路

2.3 I/Q失配校准

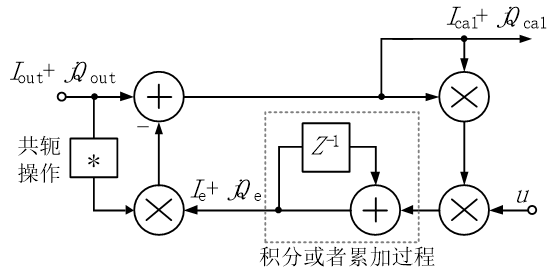

I/Q失配主要是指收发链路中I/Q两路的幅相失配以及正交本振(Local Oscillator, LO)信号的相位失配。低中频接收机中的I/Q失配校准模块通常位于下变频混频器和复数域镜像抑制滤波器之间用以提升滤波器的镜像抑制能力,采用数模混合设计的方法,具体的补偿电路结构如图3所示。

图3 适用于低中频接收机的正交失配校准电路

零中频接收机的I/Q失配校准通常在数字基带处理模块中进行补偿,典型校准电路结构如图4所示,其补偿原理与图3相似,只是采用LMS算法逐步将误差补偿电路中补偿参数的最优值估计出来。校准过程中的I/Q支路输入参数只要具有平稳随机特性,均适用于该校准机制。

图4 I/Q失配基带自适应LMS校准电路

2.4 谐波抑制技术

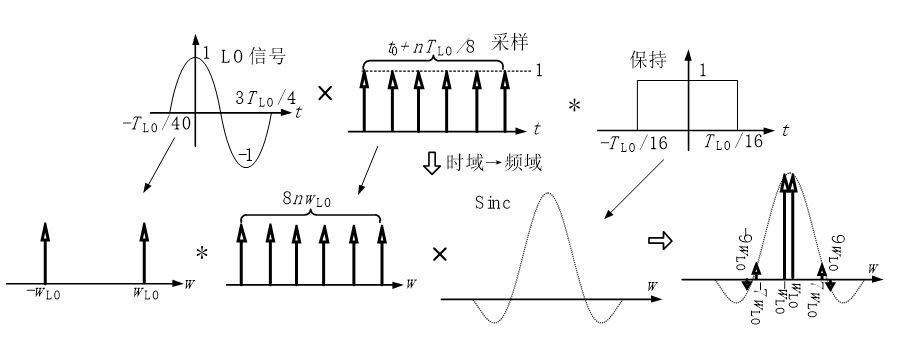

谐波抑制技术是软件定义无线电射频接收机中的一个关键指标,由于混频器LO开关引入的奇次谐波,接收机输入端在无声表面波(Surface Acoustic Wave, SAW)滤波器或者SAW滤波器带外抑制性能较差时,输入端存在的奇次谐波干扰会通过与LO信号的奇次谐波混频干扰有效频带内的信号。谐波抑制的典型电路结构是采用多相(>4)混频结构,以8相为例,相应的LO开关频谱如图5所示。

图5 八相混频器本振信号频域等效图

2.5 滤波器带宽校准

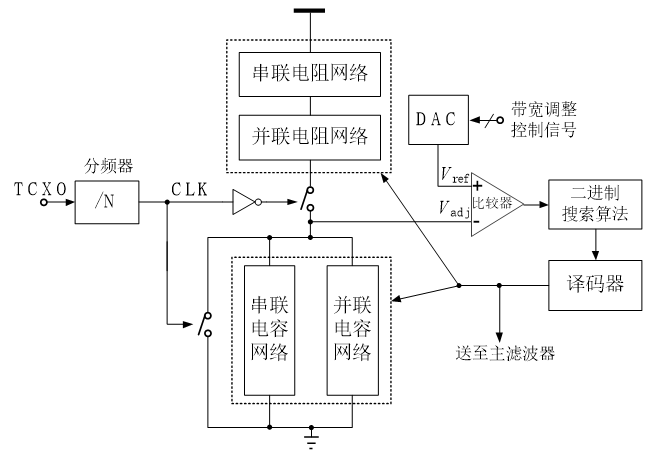

对于有源RC滤波器,典型的补偿算法通常采用基于RC时间常数的开关电容充放电机制对带宽偏差进行校准,但是由于校准自由度的限制,这种带宽校准电路并不适用于软件定义无线电射频收发机的设计中。通过RC振荡器与标准参考时钟的比较,实现了滤波器带宽的动态校准,避免了温度波动对滤波器带宽的影响,一种更简洁的宽带滤波器校准方案如图6所示,此时的电阻和电容既可以用来调节滤波器的带宽,同时也可以起到校准带宽精度的作用。

图6 宽带滤波器带宽校准电路

2.6 本振泄露校准

LO泄露同时存在于射频的收发链路中,主要是由I/Q支路中存在的直流偏移、混频器开关管以及驱动管的失配导致的。接收链路中的LO泄露向解调方向会导致直流偏移饱和接收机,向天线方向会导致直接泄露。直流偏移可以通过直流偏移校准有效抑制,向天线方向的直接泄露由于低噪放较高的反向隔离度也可以忽略不计。

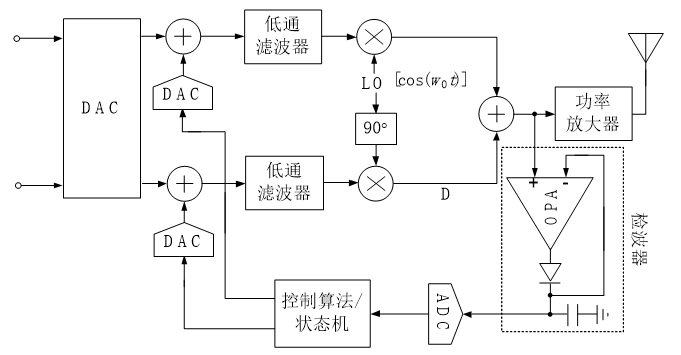

图7 发射端载波泄露校准电路

发射链路的LO泄露校准通常采用收发回环的校准方式,通过泄露幅值检测(图7),下变频至基带或者直流进行数字域功率检测等方式估计泄露LO信号的大小,并与预设功率值进行比较,产生的反馈信号通过DAC对I/Q两路的失配进行电压或者电流补偿以抑制LO泄露的大小。

2.7 数字预失真

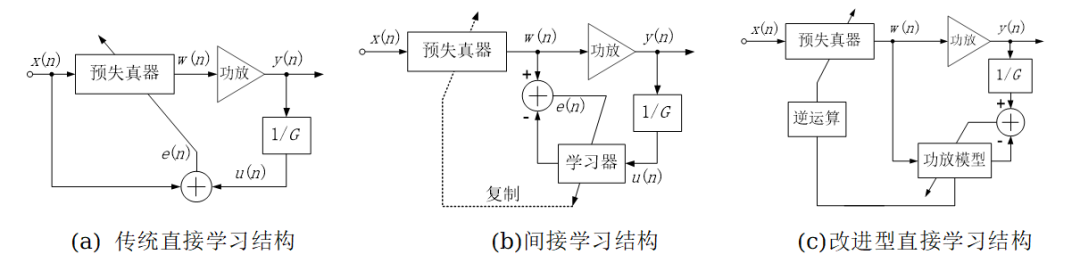

数字预失真(Digital Pre-Distortion, DPD)技术通过在PA前级基带电路中加入预失真模块补偿AM/AM以及AM/PM失真来有效提升PA的线性性能,在目前的高性能PA设计中得到了广泛的应用。

图8 DPD学习结构

DPD的学习结构包括直接学习结构、间接学习结构、改进型直接学习结构3种,如图8所示。

频率综合器的设计通常都是具有一定输出频率范围的宽带电路,对于软件定义无线电等宽带应用场景更是如此。

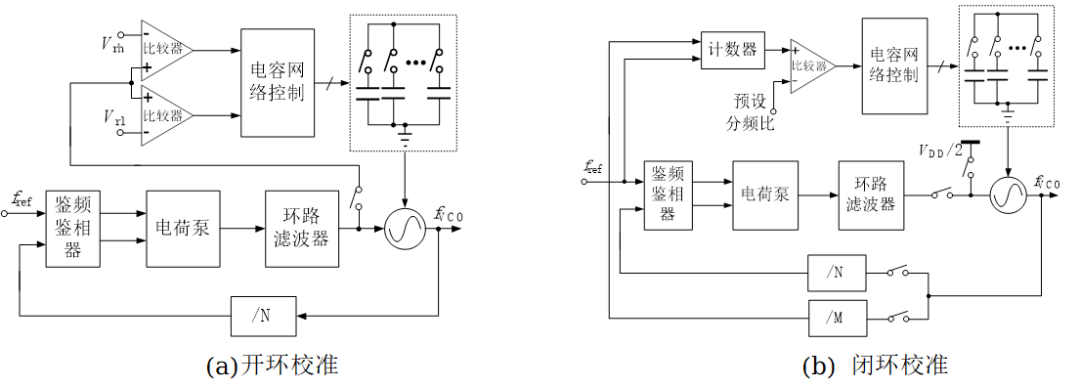

3.1 自动频率校准

AFC分为开环AFC和闭环AFC两种,如图9所示。开环AFC的锁定标记为VCO的控制电压位于两个参考电压Vrh和Vrl之间,其锁定速度较快,无需搜索完电容阵列的所有编码,仅以电压范围作为判决标准,但是开环结构容易受工艺及温度偏差的影响,不易锁定最优频率调谐线。

图9 AFC校准方法

对于包含多个VCO的频率综合器而言,在进行AFC锁定之前,首先需要确定选择哪一个合适的VCO,VCO的选择依赖于频率综合器输出频率的大小。

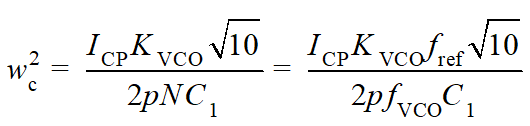

3.2稳定性校准

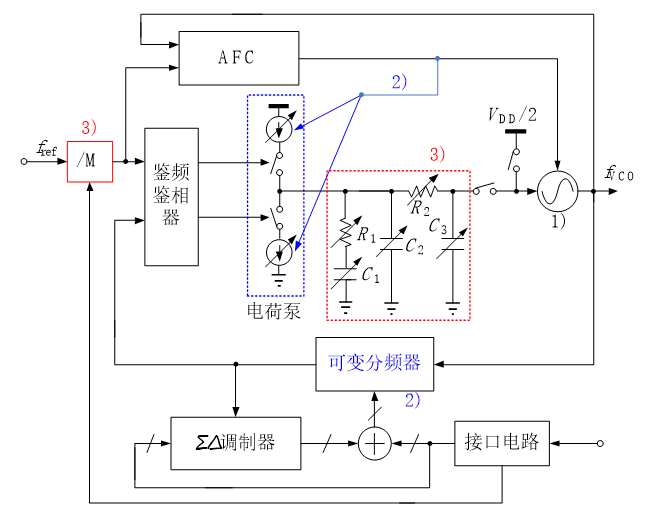

频率综合器环路稳定性的维持需要在完成稳定性预设计后保证环路带宽的恒定性,以4阶II型频率综合器为例,如图10所示,其环路带宽的表达式为

其中,ICP为电荷泵的充放电电流,N为频率综合器的分频比,C1为环路滤波器的第一级电容值。因此如何维持上述参数之间的平衡性是稳定性校准需要解决的问题。

图10 频率综合器稳定型校准示意图

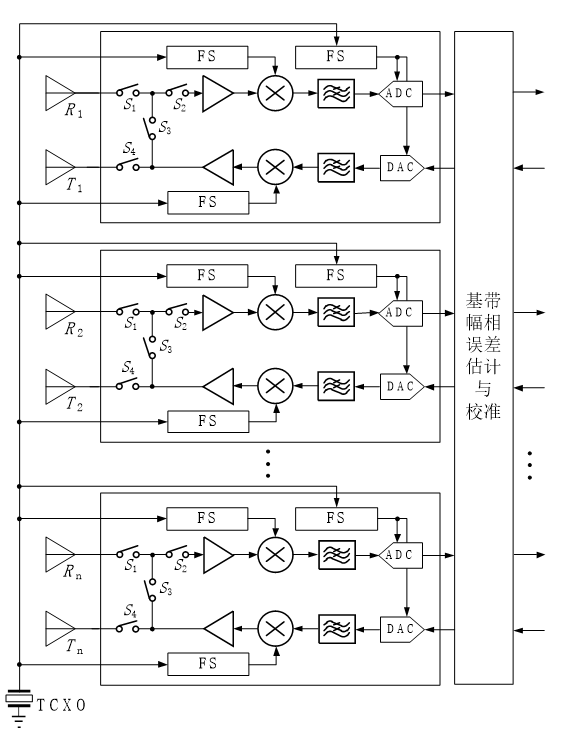

5G时代,相控阵、MIMO技术得到了大规模应用,致使多通道射频收发集成电路逐渐出现,最典型的为ADI公司的2´2多通道RFIC—AD9361/AD9371/AD9375系列芯片以及4´4多通道RFIC—AD9026芯片。上述应用场景除了多通道需求外,还要求多通道射频收发具备射频同步性、基带同步性以及多通道的幅相匹配性。

基带同步性主要是为了保证ADC和DAC的采样时钟是同步的,除了保证用于提供采样时钟的基带频率综合器的输出频率同步性以外(与射频同步相同),还必须在基带频率综合器完成同步后复位后续的外部分频器以保证采样频率的同步性,完成基带同步。

对于射频通道的幅相匹配性,校准过程如下:首先在外部放置一个单音发射源,同时闭合开关S1和S2,选取任意接收通道为参考通道,剩余接收通道的输出依次(或者同时)与该参考通道的输出进行比较(相除),并将比较结果依次作为各对应接收通道的幅相补偿值,具体工作原理如图11所示。完成接收通道的校准后,可以将对应的系数写入(上电置位)数字基带处理模块中,避免每次上电后均需要校准。发射通道的校准是在接收通道校准完成的基础上通过回环的方式完成的(闭合S2和S3,断开S1和S4),校准方式与接收通道类似,只是信号的输入需要通过发射链路从基带输入。为了避免温度变化对幅相失配的影响,通常还需要在不同的温度值下进行幅相失配校准并存储校准系数,然后根据温度传感器选择需要切换的补偿系数。

射频集成电路中的校准技术是高性能射频集成电路设计必须要克服的关键技术,这些校准技术种类繁多,实现复杂,且需要通过严格的状态控制逐一完成,是一项高难度的系统性工程。本文所述的校准技术是目前应用最广泛、效果最明显的10个核心校准技术,涉及射频收发链路、频率综合器、多片同步等三大方向,并且较全面的给出了目前各类典型的校准算法,为高性能射频集成电路的设计打下了良好的基础。

美 编:谢 军、陈 倩

校 对:余 蓉、马秀强

审 核:陈 倩

- The End -

版权声明:欢迎转发本号原创内容,转载和摘编需经本号授权并标注原作者和信息来源为云脑智库。本公众号目前所载内容为本公众号原创、网络转载或根据非密公开性信息资料编辑整理,相关内容仅供参考及学习交流使用。由于部分文字、图片等来源于互联网,无法核实真实出处,如涉及相关争议,请跟我们联系删除。我们致力于保护作者知识产权或作品版权,本公众号所载内容的知识产权或作品版权归原作者所有。本公众号拥有对此声明的最终解释权。

投稿/招聘/推广/合作/入群/赞助 请加微信:15881101905,备注关键词

“阅读是一种习惯,分享是一种美德,我们是一群专业、有态度的知识传播者

↓↓↓ 戳“阅读原文”,加入“知识星球”,发现更多精彩内容.

分享💬 点赞👍 在看❤️@以“三连”行动支持优质内容!