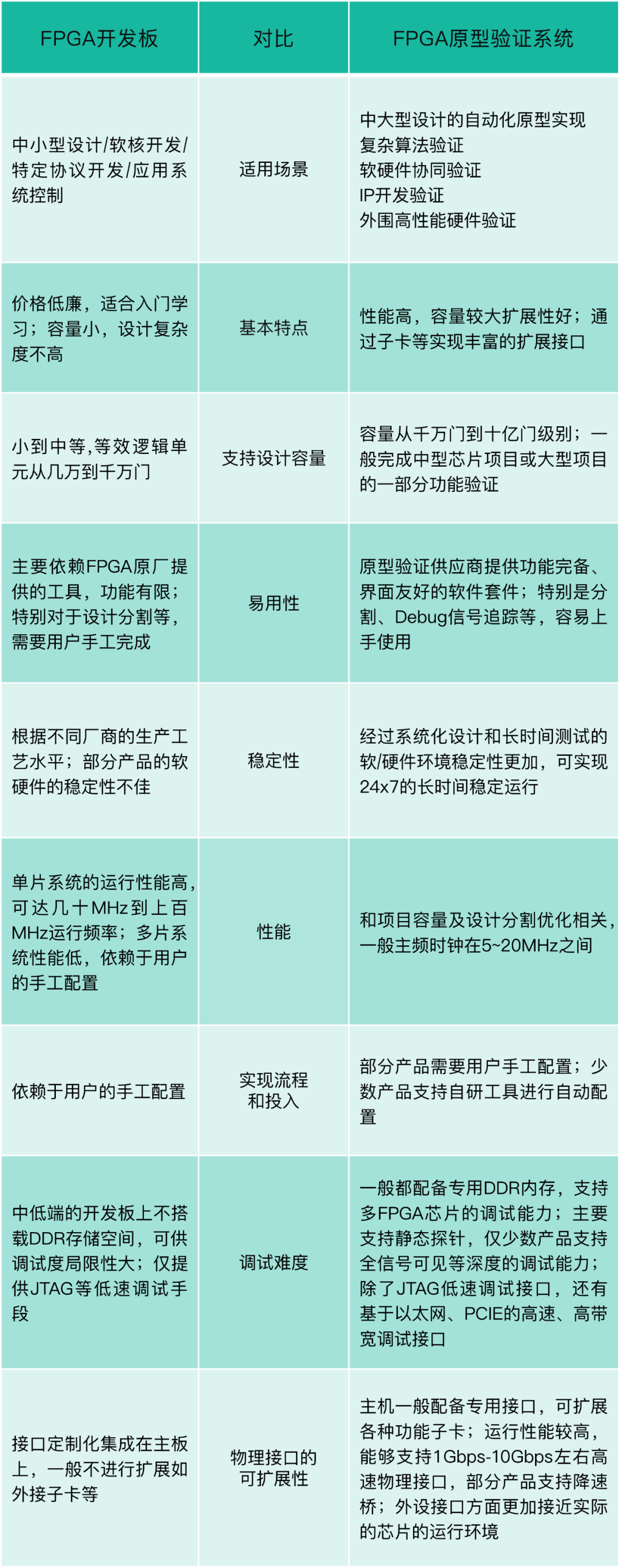

FPGA开发板:

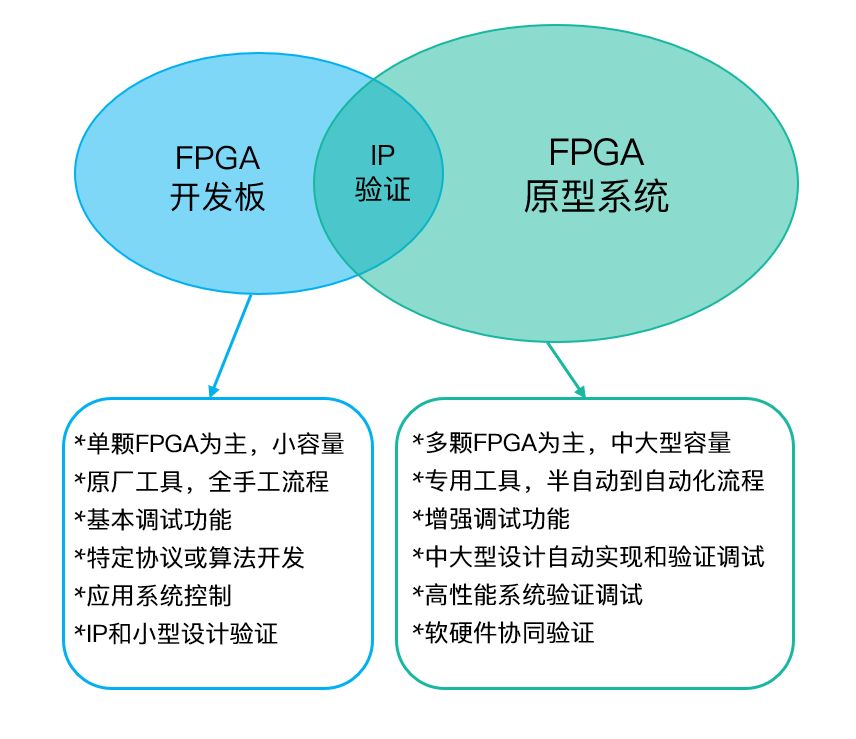

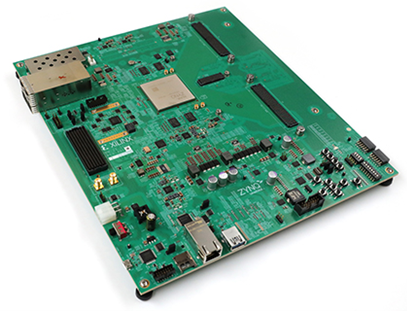

FPGA开发板的主要场景是“开发基于独立FPGA芯片的IP或应用系统”,其设计目标是精简化、高性能、低成本,并自带合适的外设接口,对调试功能的要求限于在单颗FPGA上用原厂软件调试。

因此其搭载的FPGA芯片通常的容量为小到中等规模,实际应用中,往往用于进行中小规模、特定协议功能芯片的开发,比如涉及以太网、MIPI、NVME/M.2 SSD控制、UART/I2C 控制、HDMI/DVI显示控制等。也有直接把一块FPGA开发板放在一个大型系统之中,起到控制板的作用,这样用户可以灵活地对控制信号做各种调整。也有一些应用场景计算算法用较大容量的FPGA实现,达到高性能和算法灵活性的应用目标。同时,由于中低端的开发板售价适中,FPGA开发板也适合初学者进行学习使用。

其次,部分FPGA开发板也被用在IP和小型芯片设计的开发验证场景。这部分开发板配备大容量的FPGA芯片,甚至是单板配备多片FPGA芯片来适应开发验证场景,一般由用户自己负责手工实现从设计到FPGA功能原型的流程。

FPGA原型验证系统:

FPGA原型验证系统的主要应用场景是“芯片设计过程中搭建软硬件一体的系统验证环境”:一是芯片流片回来前为软件团队提供调试驱动软件的平台,加速芯片上市时间;二是作为芯片仿真验证的一个补充,因为FPGA可以接真实的硬件子卡,跟仿真使用的软件模型有一定差别,有一定机会发现隐蔽的bug ;此外FPGA相对软件仿真以及Emulator速度快,比较适合一些耗时较多的大场景case。故在芯片设计越来越大的情况下,其设计目标是能使用多颗FPGA芯片快速实现高性能的全系统验证原型,并支持该场景下的调试需求。

首先,它搭载的往往是较大容量和多片的FPGA芯片,如Xilinx VU440/VU19P, Intel 的Stratix 10等,那么它就非常适合进行复杂算法、CPU/GPU类型芯片的验证和实现:比如人工智能,多核RISC-V处理器IP等开发环境;如果是SoC芯片或大型IP的开发,那么可以将FPGA系统经过互联扩展容量后,进行验证。

其次,FPGA原型验证系统更重要的目标,是从硬件和软件上支持大型芯片功能原型的各项要求。如低延迟并行IO接口、高带宽Serdes接口、自动化设计分割到多片FPGA并优化性能、多片FPGA的信号调试、原型系统规模的任意缩放、各种软硬件接口扩展方案,等等。这些目标决定了原型验证系统需要更专门的设计,特别是配套的自动化工具,因为对两三片FPGA以上的中大型设计,手工实现设计分割和优化的投入太大,设计团队更需要自动化工具。

FPGA开发板

FPGA原型平台

基于模块化的设计/可伸缩的验证平台规模

在保证一定的高速仿真性能的前提下提供验证完整性

提供从软件早期开发到系统级验证的解决方案

提供从综合、自动模块分割 、布局布线、FPGA bit产生、下载,以及在线/离线Debug的整套流程

提供丰富的调测手段,帮助用户快速定位问题,易于Bring Up

提供丰富的接口子板和外部真实设备相连

提供软件接口与外部软件通讯

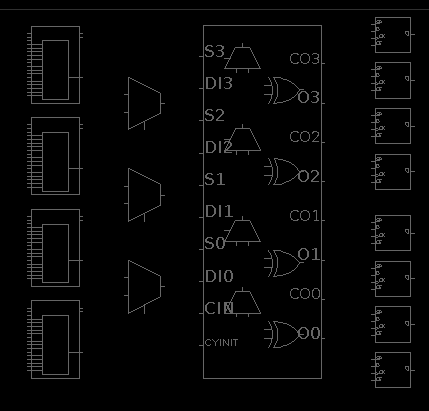

提供丰富的IO接口,以及高速Serdes接口用于partition互连以及外设子卡的互连

综合时进行专门的时序驱动优化

综合阶段充分利用并行化手段降低设计规模对综合时间造成的影响,尽量优化网表的时序和面积

算法优化、能够实现大数量的FPGA自动分割且配置简便综合工具与分割工具配合保留内部信号名称,并与综合工具配合映射信号名称,支持RTL源代码调试

自动产生时钟并处理时钟的分割,对于数片至数十片FPGA的大型设计实现很重要

最大程度保留原来代码设计层次,提高增量编译度和可调试性,分割前后功能保持一致

服务器软件时内存资源控制得当

保证分割结果正确的情况下,耗时短

总 结