限制VDMOS开关时间和截止频率的主要因素是器件本征电容和寄生电容的充放电过程,尤其是器件元胞P阱间的栅漏电容。

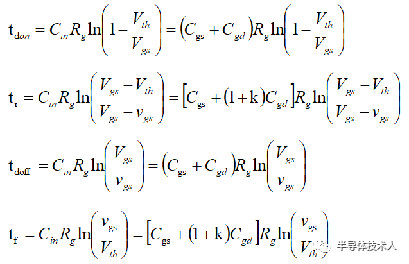

VDMOS的上升延迟时间tdon、上升时间tr、下降延迟时间tdoff、下降时间tf的关系可分别表示为:

式中Rg为器件外接电阻,Vth为阈值电压,Vgs是外加栅源电压,vgs是使器件漏源间电压下降到外加值10%时的栅源电压。Cin是器件的输入电容。Cgs是器件的栅源电容,Cgd是栅漏电容,k=-dVds/dVgs是器件电压放大系数。Cgd直接影响到器件的输入电容和开关时间,Cgd通过密勒效应使输入电容增大,甚至起主导作用,从而使器件的上升时间和下降时间变大。器件在开关转换过程中的功率损耗主要由开关时间决定。

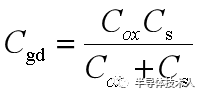

Cgd主要由器件元胞P阱间栅漏覆盖区的氧化层电容Cox和N-漏区表面的状态电容Cs串联构成,关系式为:

减小Cgd的主要措施是减小元胞P阱间的Cox和Cs。Cox与硅栅及源极在P阱间的覆盖面积和氧化层厚度有关。Cs是微分电容,既与P阱间N-漏区表面状态有关,由与硅栅和源电极的覆盖面积有关。

针对VDMOS交流特性及影响交流特性的结构参数进行了讲解。内容为:VDMOS寄生二极管的反向恢复特性;VDMOS寄生栅电阻、VDMOS电容特性(输入电容、输出电容、密勒电容),着重讲解了各个电容的组成部分及影响电容的结构参数;VDMOS单脉冲雪崩耐量的机理及改善方法。

本视频内容较基础,适合于半导体器件设计和制备从业者或微电子专业学生的入门级学习。

视频见以下百度网盘链接和提取码