这个案例是我们配合客户进行设计的一款PCIE连接器的高速定制夹具,我们负责设计和仿真,然后客户自己找工厂去加工板子和后面的焊接。由于速率比较高,因此高速先生也对板子进行了精准的仿真,保证同组连接器和PCIE连接器的阻抗优化。

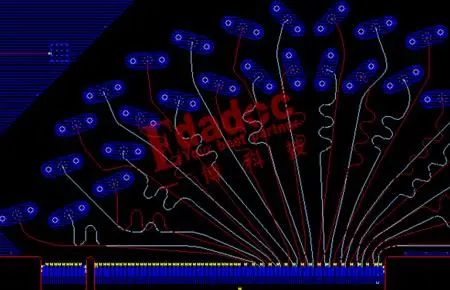

设计出来的板子就长下面这样。

过了一段时间后,那是一个非常炎热的下午,突然收到了这家客户发过来的邮件,说这款夹具加工出来阻抗非常的差。高速先生重新打开设计文件来看看,看到走线就是很简单的表底层的单线,也不存在共面参考和隔层参考这些看起来还稍微有点特殊的case,虽然不知道客户找了哪家的板厂来加工,但是高速先生认为即使是比较一般的板厂也应该没问题才对。

然而,当高速先生看到客户发过来的阻抗测试结果发现,原来真的有这么一家板厂能做的如此与众不同,因为它硬生生的把50欧姆的单端阻抗做到了只有38欧姆,我们让客户把板子寄过来自己测试下。恩,是的,的确只有38欧姆左右。在这个moment,还真的让高速先生惊讶到了!

当然,客户本身也具有一定的SI理论基础,明白这不是设计的问题,一定是加工方面的问题,因此客户知道我们有板厂之后。就希望让我们帮忙来进行下切片分析,看看到底存在了哪些加工的偏差能导致那么离谱的阻抗。

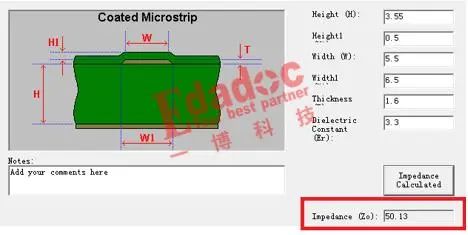

我们立马把这块板子拿到工厂去切片,让工厂通过切片后量出相关的传输线参数。在切片数据还没回来之前,高速先生又再次认真的对设计的线宽进行了阻抗计算,的确设计上没问题,就是50欧姆的传输线。设计线宽为6.5mil,线到参考平面的高度为3.55mil,采用M6级别的板材,外表层默认是0.5Oz的基铜然后进行电镀,如下所示:

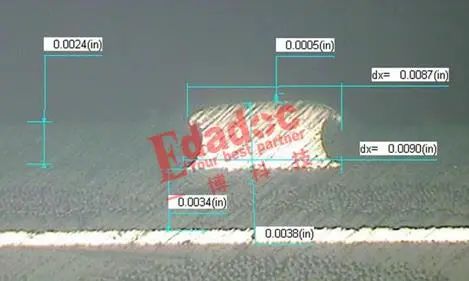

在我们已经确保设计上没有问题之后不久,我们的板厂就快速响应,已经把切片数据发回给我们高速先生了。当我们打开切片数据后,整个人都不好了,不知道大家看了之后好不好呢?

看看上面的切片数据,高速先生列举下加工出来的参数和设计参数存在的差别,如下所示:

1、设计线宽6.5mil,加工线宽为9mil

2、设计的表层铜厚为0.5Oz+电镀,大概在1.6mil左右,加工出来竟然达到3.8mil,看起来是用1Oz的基铜进行电镀的结果(可能还不止,已经无法确认了)

3、介质厚度由于流胶的影响也由3.55mil稍稍降到3.4mil

4、这个上下线宽也蚀刻得太不均匀了

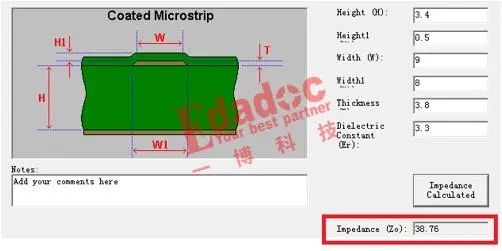

然后高速先生怀揣着忐忑的心情对这组加工后的数据进行阻抗计算。。。

当把参数都输进去之后,结果发现的确能算出来就是38欧姆左右的阻抗。

我们把这个切片数据给到我们的客户后,估计这家客户该去找他们板厂说理去了哈。

对此高速先生只能对他们找的这家板厂说一句。。。

— end —

本期提问:

大家有遇到过一些阻抗加工偏差的case吗,分享下你们的经历?

如果不想错过“高速先生”的精彩内容,请记得点击上方蓝字“高速先生”,右上角“...”点选“设为星标”。可第一时间看到高速先生的推文,感谢大家的关注和支持!

扫码关注

微信号|高速先生

觉得内容还不错的话,点个“在看”呗