文︱KATHERINE DERBYSHIRE

来源︱Semiconductor Engineering

编译︱编辑部

由分立式GaN器件组成的电路虽然能够实现特定功能,但由于GaN集成电路能够提供很多与硅集成电路相同的优势,因此GaN集成电路仍是未来发展的终极目标。

随着电路尺寸的调整,成本逐渐降低,同时寄生电阻和电容不断减小,互连通道缩短。此外,改进的器件性能使GaN逻辑能够处理更多的电路功能,从而在单个晶圆上集成完整的系统,并实现与其他半导体市场相类似的规模经济。

GaN具有3.4 eV的大带隙,使其具有比硅更高的击穿电压,开关和导通损耗较低。电动汽车等高功率应用需要复杂的电源管理电路,而这些电路尚未在GaN中实现。但这种材料也非常适合几种低功耗应用。GaN逐渐成为LED照明应用中的主流趋势,该材料具有更高的成本效益,且具备其他应用可以建立的制造基础。

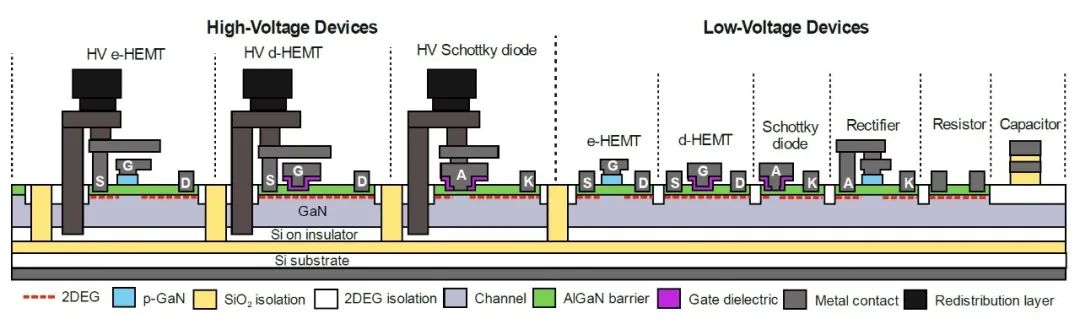

图1:SOI上的GaN平台支持利用深沟槽隔离、基板触点和RDL的单片集成器件(图源:Imec)

二维电子(和空穴)气体

GaN高电子迁移率晶体管(HEMT)与硅MOSFET相比有着多方面差异。虽然严格控制量的碳起到掺杂剂的作用,但电荷传输主要取决于二维“电子气体”(2DEG)的形成。AlGaN和GaN之间界面处的拉伸应变导致界面区域的自发极化,以及界面处能带结构的不连续性。电子迁移率很高(在极化区域内约为1,500 cm2 / V-s),但在该区域之外较低,有效地限制了界面附近的载流子。

然后,2DEG 形成设备通道。它位于电容器的两个板之间。在耗尽模式器件中,当顶板(栅极)为正极时,它会在相反的板上感应出正电荷。负载流子(电子)从通道中耗尽并在两个板上积聚,电导率下降。耗尽模式设备正常打开。当栅极电压小于阈值电压时,电流流动。

相反,对于增强模式器件,栅极上的正电荷将电子 从p掺杂的本体材料中拉入通道。增强模式设备通常处于关闭状态。当栅极电压小于阈值电压时,没有电流流动。特别是在功率器件中,在晶体管上使用正常值会带来安全风险,因为即使控制电路发生故障,电流也会继续流动。出于这个原因,增强模式设备更可取。

虽然正常开和常关器件的可用性允许实现逻辑门,但增强和耗尽模式器件都取决于电子的流动。事实上,虽然增强模式器件在栅极和AlGaN势垒之间放置了p-GaN层,但电流路径中没有p掺杂材料,GaN通道中没有pn结。目前也没有任何商业上可行的p沟道GaN晶体管。原因是GaN孔迁移率非常低,只有10到20 cm2 /V-s。在12月的IEEE电子设备会议上,加州大学圣巴巴拉分校(UCSB)的Aditya Raj解释说,一些研究人员已经使用基于AlInGaN的异质结证明了2D空穴气体。不幸的是,获得足够的电流需要更高的充电密度,在5 x 10^13/cm2的范围内。

没有p-GaN器件,CMOS逻辑是不可能的。相反,Imec的半导体工艺工程师Thibault Cosnier解释说,GaN电路依赖于电阻晶体管逻辑(RTL)和直接耦合FET逻辑(DCFL)。RTL需要在开关时间和静态功耗之间进行权衡,在DCFL设计中,通过用耗尽模式HEMT替换电阻器,可以在一定程度上缓解这种情况。Imec小组报告说,他们能够在高达200V的工作电压下产生具有低泄漏和良好稳定性的逻辑电路。

采用分立式GaN元件构建的电路目前表现良好,但完全集成的GaN电路将提供理想的成本和性能优势,如缩放硅CMOS IC。为此,制造商正在寻求硅晶圆上GaN集成电路的增长。

用于隔离的工程晶圆和晶圆上的堆叠通道

硅基GaN晶圆不仅有助于硅晶体管的集成,而且已经开始通过推动200mm工艺演进,来满足纯GaN电路的发展需求。

在Imec GaN技术项目总监Stefaan Decoutere看来,GaN具有与硅不同的晶格尺寸和热膨胀特性,这意味着将两者结合在同一片晶圆上,那么该晶圆在冷却时保持平坦则需要一系列工程缓冲层,厚度控制在纳米以内。由此产生的晶圆具有复杂且重叠的晶格应变场,这是GaN集成不可避免的特性。载流子陷阱、位错和其他缺陷可能会在生成结构中的许多内部接口处累积。

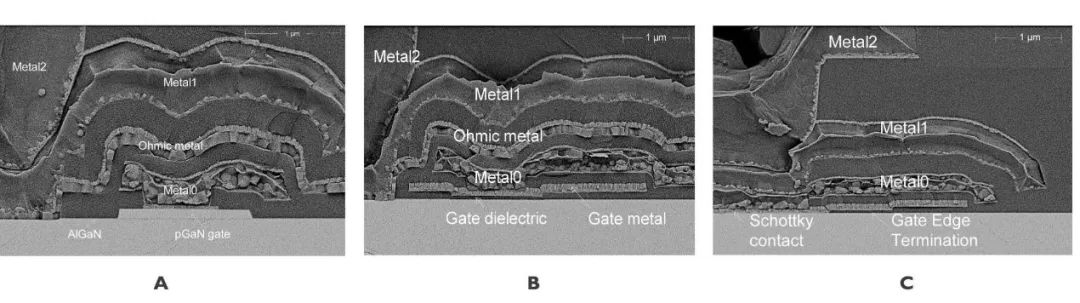

图2:高压元件的横截面显示了增强模式GaN HEMT(a),耗尽模式MIS HEMT(b)和肖特基势垒二极管(c)。稳定的器件可在高达 200 V 的电压下工作,并采用 200mm GaN-on-SOI 晶圆构建(图源:Imec)

一旦存在极其精确的GaN和相关化合物沉积工艺,工程超晶格就可以扩展潜在器件结构库。正如硅IC制造商正在研究堆叠纳米片设计以增加器件电流一样,堆叠通道设计可能有助于p-GaN器件实现足够的电流。UCSB小组报告了基于镁掺杂的GaN / AlGaN超晶格的具有七个并行通道的GaN PFET的预期结果。

虽然在单个晶圆上集成多个GaN器件会减少互连寄生效应,但重要的是要记住,硅尤其是导电基板。GaN集成增加了相邻设备之间交互和串扰的可能性。当在同一基板上制造高电流和低电流元件时,良好的电气隔离尤为重要。香港科技大学的Gang Lyu及其同事提出了一种工程衬底,其顶部是高掺杂的p+硅,然后是GaN缓冲结构。这种设计将p-n二极管放置在垂直于GaN器件层的位置,该层被深沟槽隔离区域分解成岛。p+岛允许每个GaN晶体管的本地源到硅连接,背面触点连接到总线电压,而p-n结则将晶体管与干扰隔离开来。

管理故障以实现可靠的未来

尽管GaN IC距离商业化还有很长的路要走,但影响电路性能和可靠性的问题越来越突显出来。正如德州仪器(TI)的GaN功率过程集成工程师Dong Seup Lee在IEDM上所解释的那样,较之逻辑器件,功率器件必须管理更大的电场,也更容易受到各种磁场引起的故障影响。由于缺乏高质量天然氧化物,GaN具有高密度的表面状态。他补充表示,栅极和其他金属接口附近的高电场可以驱动电子进入这些状态。从而导致GaN表面捕获的电子无法承载通道电流,耗尽宽度发生变化,电阻随之上升,最终可能导致器件故障。

此外,GaN本身也会发生故障。GaN是一种极性材料,高电场会引起晶格应变,最终导致缺陷形成和电流泄漏路径。Lee警告设备设计人员,由于栅极边缘和源极附近的电流浓度,GaN可能会发生击穿。在可能存在大电场但电流不通的关闭状态设备中,日本国家先进工业科学技术研究所的研究人员观察到类似于介电击穿的突发性和破坏性击穿事件。为了避免击穿事件,他们建议将SiC二极管集成到器件基板上,为多余的累积电荷创建替代电流路径。

总结

从分立GaN器件过渡到GaN集成电路,从实验室概念验证过渡到商业应用,不可避免地将可靠性和工作包络问题带到了最前沿。在电动汽车和功率器件市场的强劲驱动下,研究人员和工程师正在深入研究GaN特有难题,不断推出可制造的解决方案。