在之前的文章中,我们讨论了使用 Verilog语言元素对组合电路的描述。本文重点介绍同步时序电路。我们将首先查看同步电路的通用模型,然后以双向计数器的 Verilog 描述为例进行讨论。

在组合电路中,输出仅取决于输入的当前值。然而,时序电路的输出不仅取决于输入的电流值,还取决于电路的状态。电路的状态由输入的先前值决定。

因此,时序电路具有存储器,其输出取决于过去输入的顺序。这些电路使用诸如触发器 (FF) 之类的存储器元件来存储系统的当前状态。

在处理大型时序电路时,如果我们使用同步方法而不是异步方法,设计问题会变得更容易解决。在同步电路中,所有存储元件都由相同的时钟信号触发。这使我们能够更好地控制系统,因为在这种情况下,我们知道数据何时将被存储元件采样。

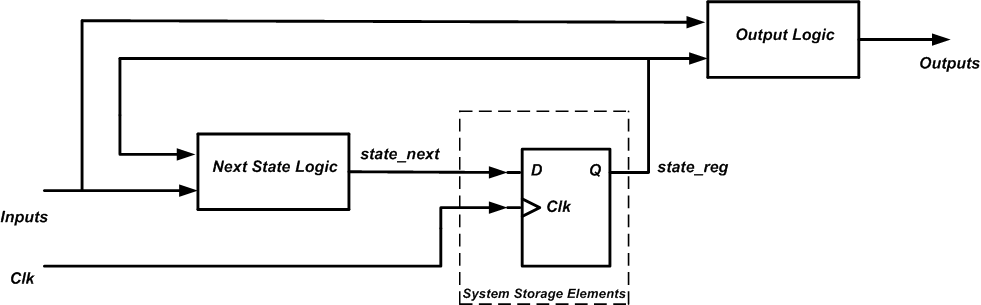

由于同步系统的所有存储元件都连接到同一个时钟,我们可以对系统进行建模,如图 1 所示。

在此模型中,虚线框代表系统的所有存储元件(本例中为 D 型 FF)。虚线框外的块是组合电路。

“下一个状态逻辑”处理“输入”和系统的当前状态,由“state_reg”表示,以确定系统的下一个状态(“state_next”)。随着即将到来的时钟上升沿,“state_next”将存储在 FF 上。“输出逻辑”块也是一个组合电路,它处理“输入”和“状态寄存器”以确定系统输出。

如图 1 所示,将同步系统与存储元件和一些组合电路分开有助于我们更容易地找到系统的 HDL 描述。我们只需要描述一些组合电路并将它们连接到存储元件。而组合电路的 HDL描述在前一篇文章中已经讨论过,对于存储元件,我们通常使用一些众所周知的 HDL 模板。

我们将查看通用计数器的 Verilog 代码以阐明这些概念,但在此之前,我们需要查看D 型触发器(也称为 DFF)的 HDL 描述。

(有关触发器双稳态单比特存储器设备的更多信息,请查看我们关于将 D 触发器转换为 SR、JK 和 T 触发器的文章。)

通常,可以使用基本逻辑门来实现 DFF。但是,在使用 HDL 在 FPGA 中实现 DFF 时,完全不建议这样做。安全有效的方法是使用一些众所周知的 HDL 模板来描述 FF,如下节所述。事实上,综合工具将此类模板识别为 FF,并使用一些优化的结构来实现它们。

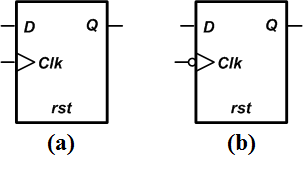

下面的图 2 显示了上升沿(图 2-a)和下降沿(图 2-b)DFF 的符号。在时钟边沿,对 DFF 的输入 (D) 进行采样并传递到输出 (Q)。对于上升沿 DFF,采样沿是时钟上升沿(图 2-a),而下降沿 DFF 对时钟的下降沿敏感。FF 通常具有可用于将系统初始化为已知状态的重置 (rst)。

下面给出了上升沿 DFF 的 Verilog 代码:

1 module D_FF

2 (

3 input wire clk, reset,

4 input wire d,

5 output reg q

6 );

7 always @(posedge clk, posedge reset)

8 if (reset)

9 q <= 1'b0;

10 else

11 q <= d;

12 endmodule此代码的第 7 行在“always”块的敏感度列表中的“clk”和“reset”输入之前使用了“posedge”关键字。“Posedge”代表上升沿,告诉综合工具“always”模块应该在“clk”和“reset”信号的上升沿被激活。

请注意,“clk”和“reset”的上升沿都在灵敏度列表中。因此,无论“clk”信号条件如何,“reset”的上升沿都会激活“always”块。换句话说,这个 DFF 的“重置”是异步的。

第 8 到 11 行使用了我们在上一篇文章中讨论过的 Verilog“if”语句。当“always”块被激活时,“reset”被选中。如果它为逻辑高电平,则 DFF 输出被复位 (q <= 1'b0)。如果“reset”不是逻辑高电平,那么是“clk”信号经历了上升沿,DFF 输出应该得到输入值(q <= d)。

请注意,我们在推断触发器时使用非阻塞赋值 (<=)。正如另一篇文章中所讨论的,不正确地使用阻塞 (=) 和非阻塞 (<=) 赋值可能会导致不想要的功能。然而,为了这篇介绍性文章的目的,我们可以简单地将系统的组合部分与其内存元素分开,并遵循以下两条准则:

使用阻塞分配来描述组合电路。

使用非阻塞赋值来推断 FF。

现在,让我们看一下双向计数器的 Verilog 代码,以进一步阐明我们的讨论。

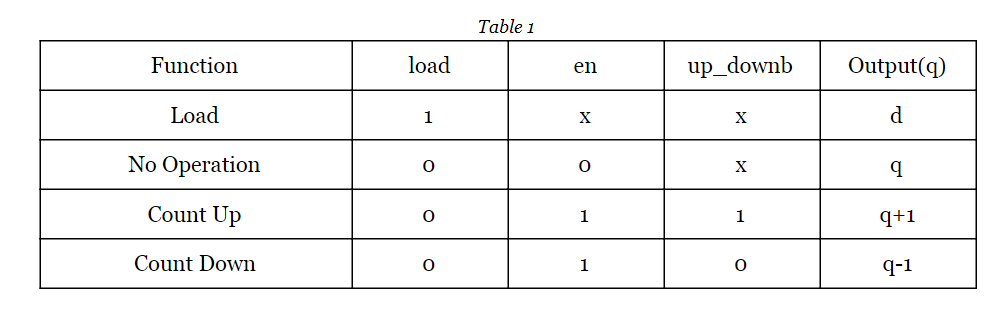

我们将为一个双向计数器编写代码,该计数器可以执行下表中列出的四个函数:

当“加载”输入被断言时,输入数据 (d) 被加载到计数器 (q=d)。当“load”和“en”都为逻辑低时,计数器保持其当前值。对于“load”=0 和“en”=1,计数器可以根据“up_downb”输入的值向上或向下计数。

八位双向计数器的 Verilog 代码如下所示:

1 module bidirect_cnt8

2 (

3 input wire clk, reset,

4 input wire en, load, up_downb,

5 input wire [7:0] d,

6 output reg [7:0] q

7 );

8 reg [7:0] q_next;

9 // The storage elements

10 always @(posedge clk, posedge reset)

11 if (reset)

12 q <= 8'h00;

13 else

14 q <= q_next;

15 //The next state logic

16 always @*

17 if(load)

18 q_next = d;

19 else if (~en)

20 q_next = q;

21 else if (up_downb)

22 q_next = q + 8'h01;

23 else

24 q_next = q - 8'h01;

25 endmodule第 10 到 14 行使用上一节中讨论的模板代码将 8 个 DFF 添加到设计中。这些是上升沿 DFF,具有异步复位。

当“reset”为逻辑高时,值 8'h00 被分配给“q”。术语 8'h00 表示十六进制基数 (8'h) 中的八位数字。这个数字的值由字母“h”后面的两个十六进制数字给出。因此,当“reset”为逻辑高时,“q”的八位都设置为逻辑低。

当“reset”为逻辑低时,“q_next”被分配给“q”。“q_next”表示图 1 通用模型中“下一个状态逻辑”的输出,并确定在即将到来的时钟上升沿应分配给“q”的值。

除了描述计数器存储元件的第 10 到 14 行之外,代码的其他行描述了组合电路。将存储元件与组合电路分开不是强制性的,但它可以帮助我们更轻松地描述系统。我们只需要为即将到来的时钟边沿确定合适的“q_next”值。第 16 到 24 行实现了这部分设计的组合逻辑,即图 1 中模型的“Next State Logic”块。它使用嵌套的“if”语句来描述表 1 的不同功能:

当“load”输入为逻辑高时,输入数据(d)被分配给“q_next”。当“load”为逻辑低且计数器未启用(“en”=0)时,计数器应保持其当前值(“q_next”应等于“q”)。对于“load”=0 和“en”=1,计数器可以根据“up_downb”输入的值向上或向下计数。

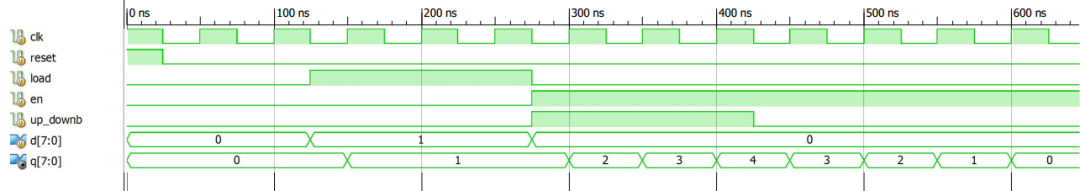

图 3 显示了代码的 ISE 仿真。

如上所述,我们不必总是将同步系统分成存储元件和组合电路,如图 1 所示。但是,我相信这种设计实践有助于我们在设计数字系统时采用更系统的方法。通过这种方式,我们可以更轻松地将设计的框图可视化并找到其 HDL 描述。

在本文中,我们首先讨论了同步电路的通用模型,其中系统分为两部分:存储元件和组合电路。然后,我们用这个模型找到了双向计数器的 Verilog 描述。这不是描述同步系统的唯一方法;然而,所讨论的方法可以简化设计过程。

今天小编带来了:ISSCC2022套餐,里面有文章、PPT、Tutorial等,同学可以拿回去自己学习研究。

1、深入理解SerDes(Serializer-Deserializer)之一

2、深入理解SerDes(Serializer-Deserializer)之二

3、科普:深入理解SerDes(Serializer-Deserializer)之三

4、资深工程师的ESD设计经验分享

5、干货分享,ESD防护方法及设计要点!

6、科普来了,一篇看懂ESD(静电保护)原理和设计!

7、锁相环(PLL)基本原理 及常见构建模块

8、当锁相环无法锁定时,该怎么处理的呢?

9、高性能FPGA中的高速SERDES接口

10、什么是毫米波技术?它与其他低频技术相比有何特点?

11、如何根据数据表规格算出锁相环(PLL)中的相位噪声

12、了解模数转换器(ADC):解密分辨率和采样率

13、究竟什么是锁相环(PLL)

14、如何模拟一个锁相环

15、了解锁相环(PLL)瞬态响应

16、如何优化锁相环(PLL)的瞬态响应

17、如何设计和仿真一个优化的锁相环

18、锁相环(PLL) 倍频:瞬态响应和频率合成

19、了解SAR ADC

20、了解 Delta-Sigma ADC

21、什么是数字 IC 设计?

22、什么是模拟 IC 设计?

23、什么是射频集成电路设计?

24、学习射频设计:选择合适的射频收发器 IC

25、连续时间 Sigma-Delta ADC:“无混叠”ADC

26、了解电压基准 IC 的噪声性能

27、数字还是模拟?I和Q的合并和分离应该怎么做?

28、良好通信链路性能的要求:IQ 调制和解调

29、如何为系统仿真建模数据转换器?

30、干货!CMOS射频集成电路设计经典讲义(Prof. Thomas Lee)

31、使用有效位数 (ENOB) 对 ADC 进行建模

32、以太网供电 (PoE) 的保护建议

33、保护高速接口的设计技巧

34、保护低速接口和电源电路设计技巧

35、使用互调多项式和有效位数对 ADC 进行建模

36、向 ADC 模型和 DAC 建模添加低通滤波器

37、揭秘芯片的内部设计原理和结构

38、Delta-Sigma ADCs中的噪声简介(一)

39、Delta-Sigma ADCs中的噪声简介(二)

40、Delta-Sigma ADCs 中的噪声简介(三)

41、了解Delta-Sigma ADCs 中的有效噪声带宽(一)

42、了解Delta-Sigma ADCs 中的有效噪声带宽(二)

43、放大器噪声对 Delta-Sigma ADCs 的影响(一)

44、放大器噪声对 Delta-Sigma ADCs 的影响(二)

45、参考电压噪声如何影响 Delta Sigma ADCs

46、如何在高分辨率Delta-Sigma ADCs电路中降低参考噪声

47、时钟信号如何影响精密ADC

48、了解电源噪声如何影响 Delta-Sigma ADCs

49、运算放大器简介和特性

50、使用 Delta-Sigma ADCs 降低电源噪声的影响

51、如何设计带有运算放大器的精密电流泵

52、锁定放大器的基本原理

53、了解锁定放大器的类型和相关的噪声源

54、用于降低差分 ADC 驱动器谐波失真的 PCB 布局技术

55、干货!《实用的RFIC技术》课程讲义

56、如何在您的下一个 PCB 设计中消除反射噪声

57、硅谷“八叛徒”与仙童半导体(Fairchild)的故事!

1、免费公开课:ISCAS 2015 :The Future of Radios_ Behzad Razavi

2、免费公开课:从 5 微米到 5 纳米的模拟 CMOS(Willy Sansen)

3、免费公开课:变革性射频毫米波电路(Harish Krishnaswamy)

4、免费公开课:ESSCIRC2019-讲座-Low-Power SAR ADCs

5、免费公开课:ESSCIRC2019-讲座-超低功耗接收器(Ultra-Low-Power Receivers)

6、免费公开课:CICC2019-基于 ADC 的有线收发器(Yohan Frans Xilinx)

7、免费公开课:ESSCIRC 2019-有线与数据转换器应用中的抖动

8、免费公开课:ISSCC2021 -锁相环简介-Behzad Razavi

9、免费公开课:ISSCC2020-DC-DC 转换器的模拟构建块

10、免费公开课:ISSCC2020-小数N分频数字锁相环设计

11、免费公开课:ISSCC2020-无线收发器电路和架构的基础知识(从 2G 到 5G)

12、免费公开课:ISSCC2020-从原理到应用的集成变压器基础

13、免费公开课:ISSCC2021-射频和毫米波功率放大器设计的基础

摩尔学堂(www.moorext.com)--摩尔学堂专注于半导体人才培训,在线学习服务平台!