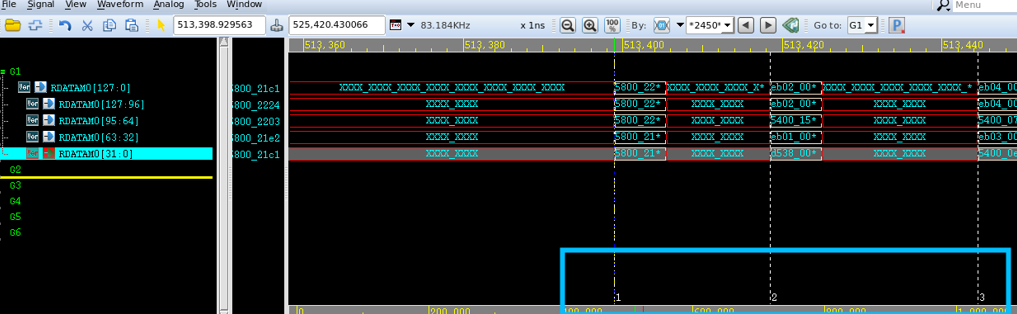

一个多比特的bus拆分成几个位宽较小的bus:

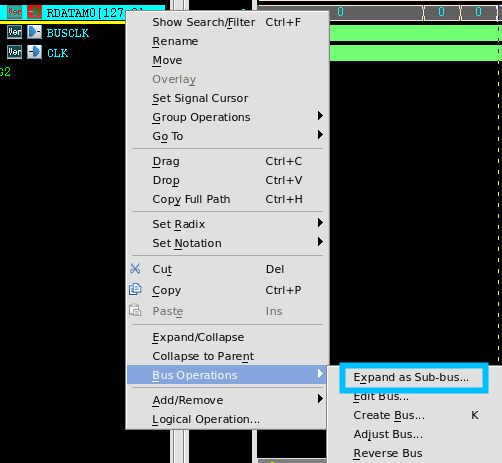

Signal -> Bus Operations -> Expand as Sub-bus

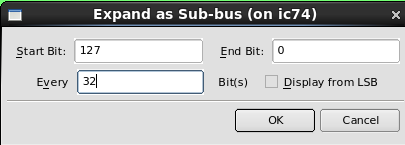

例如将128bit分成32bit:

结果:

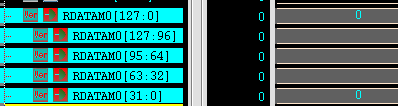

可以通过对现有信号执行的逻辑操作创建新信号,或者搜索信号值。

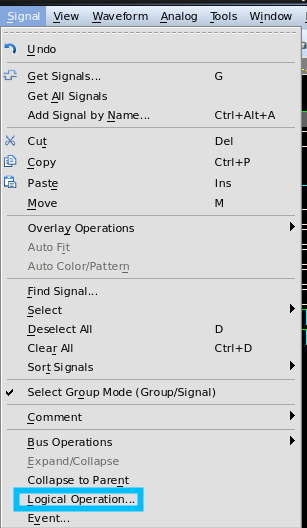

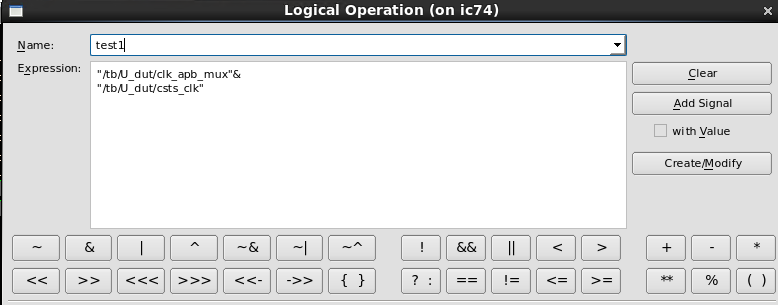

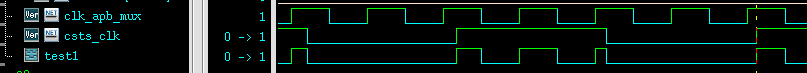

Signal -> Logical Operation

两信号进行与运算,也可以进行其他运算:

相与之后得出新信号:

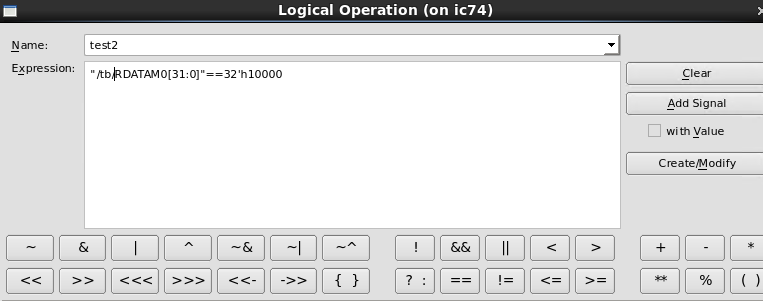

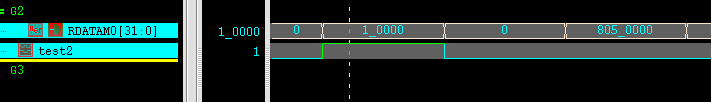

输入搜索的值,点击create,该值位置会拉高.

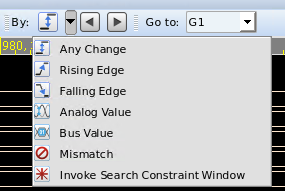

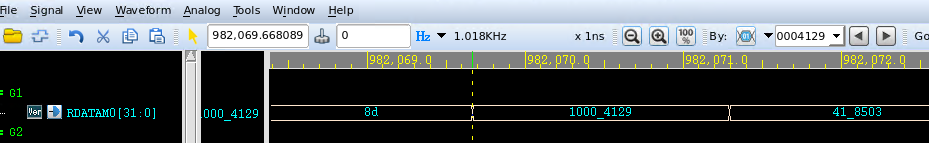

进行数值搜索、上升沿和下降沿搜索

选中信号,按n向后搜索,N向前搜索;

数值搜索:

上下沿搜索:

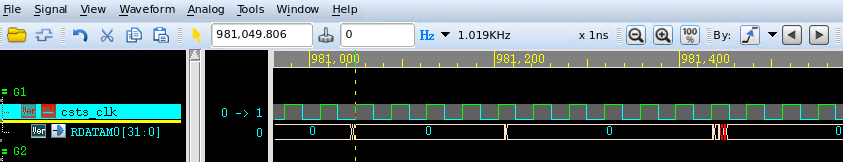

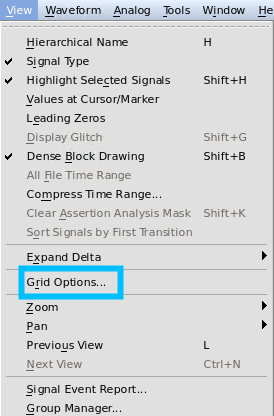

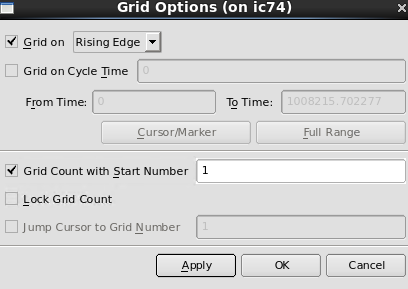

可以指定在波形窗中绘制网格线。选项包括Rising Edge, Falling Edge和 Both Edges。

View -> Grid Options

选中grid和grid counter with start number:

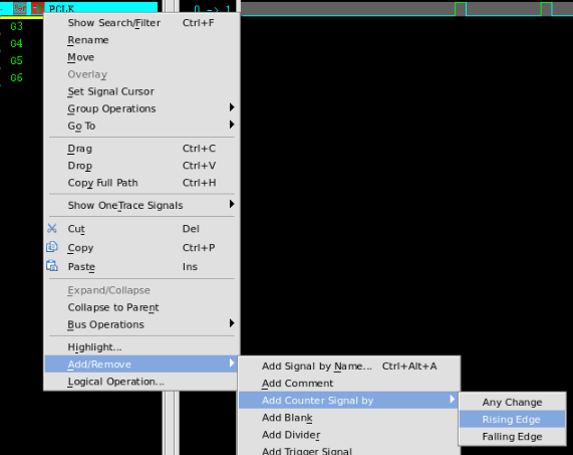

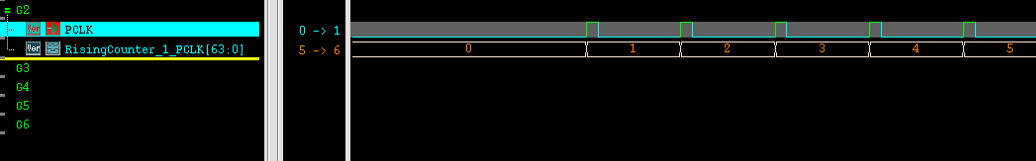

如图:信号下方出现了数字,可以用于计数。

右击PCLK信号,选择Add Counter Signal by,选择上升沿、下降沿、任意沿中的一个。

统计出某个信号在特定时间段内的跳变的次数。

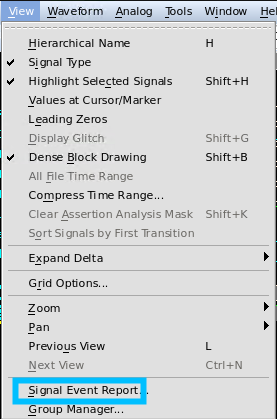

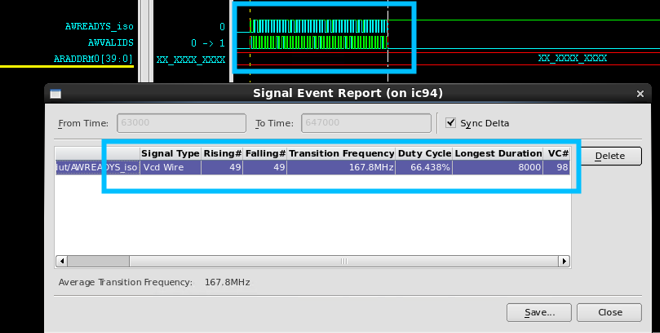

View -> Signal Event Report

Rising:指的是指定Marker时间段内上升沿数;

Falling:指的是指定Marker时间段内下降沿数;

备注:利用Logical Operation和Signal Event Report可以统计非连续有效信号

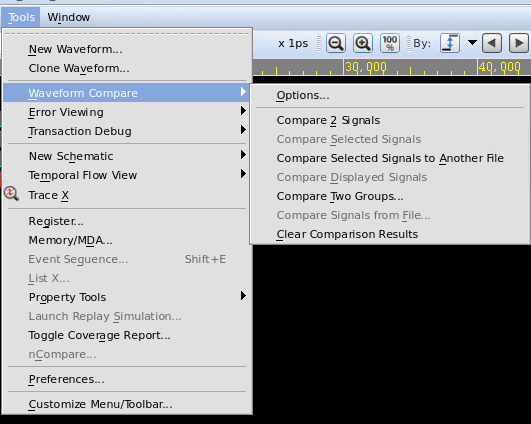

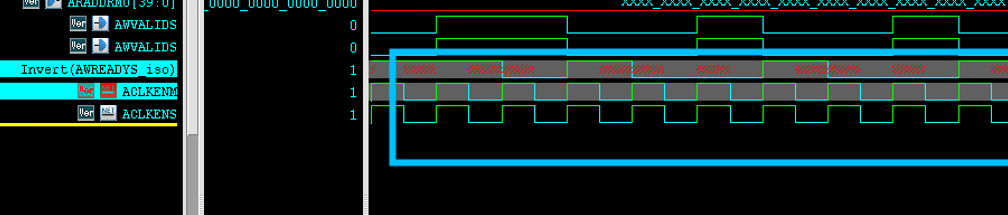

nWave提供了一种综合比较自动比较不同结果的能力。在比较完成后,nWave以图形方式显示波形窗格中的任何不匹配,然后可以通过每个不匹配来分析差异。

Tools -> Waveform Compare

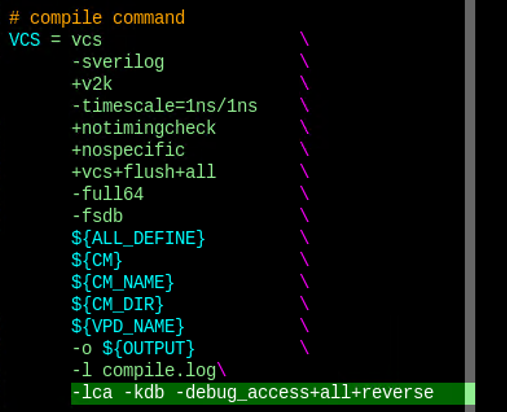

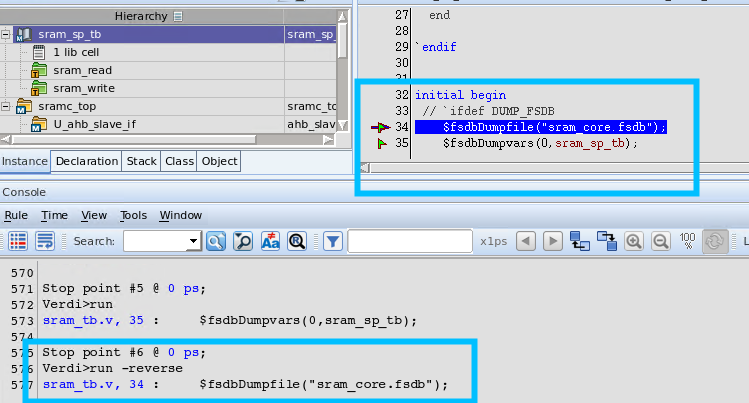

makefile中加上 -lca -kdb -debug_access+all+reverse

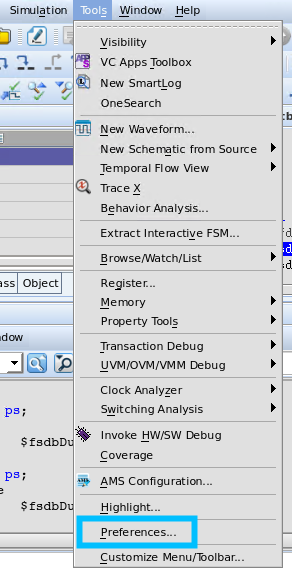

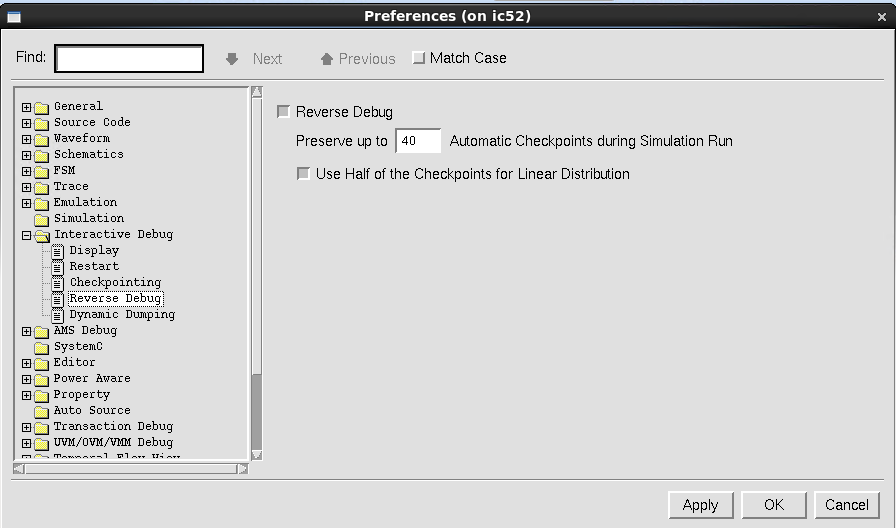

运行 ./simv –verdi &启动verdi之后,需要打开verdi的回退仿真功能:

tools->Preferences中设置

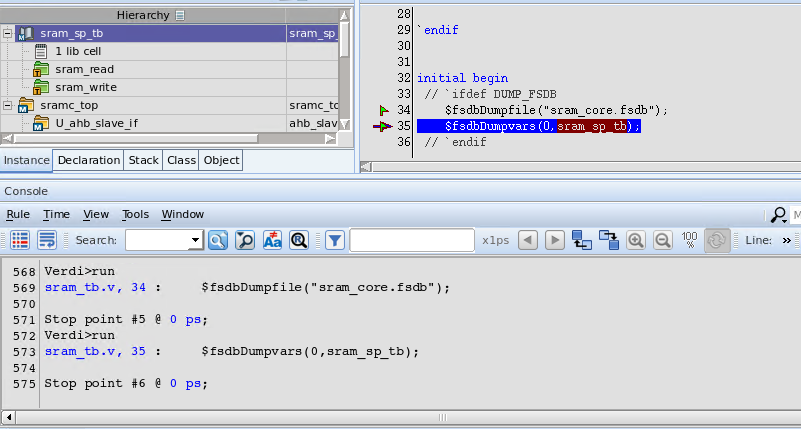

设置几个断点;在verdi的console中,输入run,启动仿真;

点击run/continue reverse回退仿真

此时,执行的光标,回到了断点代码的前一行。此时仿真的状态就回到了执行上一条指令的状态。

因此可以利用reverse功能,实现回退式仿真。这样当仿真不小心过了我们的设定点,可以使用reverse功能,回退到这个点。从而避免重新启动仿真。