▲ 更多精彩内容 请点击上方蓝字关注我们吧!

三星电子半导体业务曾因芯片良率“造假”引发外界关注。据韩国媒体报道,2月末,三星高管可能在试产阶段捏造了其5nm以下工艺的芯片良率,以抬高三星代工业务的竞争力。随后,三星启动了对原本计划扩大产能和保证良率的资金下落的调查,进一步了解半导体代工厂产量和良率情况。

据当时一位熟悉三星电子内部情况的官员对外透露,“由于晶圆代工厂交付的数量难以满足代工订单需求,公司对非内存工艺的良率表示怀疑,事实上基于该良率是可以满足订单交付的。”另有业内人士透露,在三星为高通生产的骁龙4nm制程芯片中,良品率仅为35%,并且三星自研的4nm制程SoC猎户座2200的良率更低。以致于高通这样的VIP客户都要出走,重新使用台积电生产骁龙8处理器。

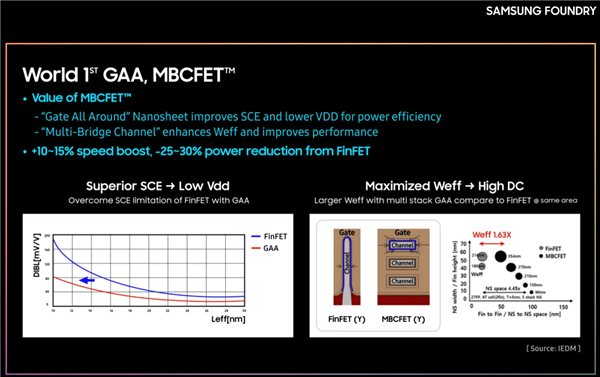

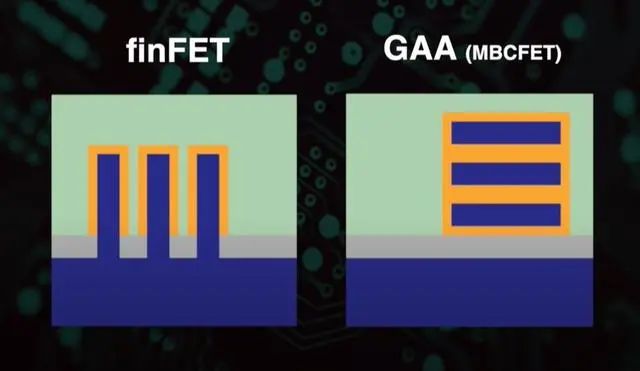

不过从技术上来说,三星现在依然是唯一能紧追台积电的晶圆代工厂,虽然在7nm、5nm及4nm节点上落后了一些,但在接下来的3nm节点三星更激进,要全球首发GAA晶体管工艺(Gate-all-around),放弃FinFET晶体管技术,而台积电的3nm工艺依然会基于FinFET工艺。

三星之前表示,GAA是一种新型的环绕栅极晶体管,通过使用纳米片设备制造出了MBCFET(Multi-Bridge-Channel FET,多桥-通道场效应管),该技术可以显著增强晶体管性能,主要取代FinFET晶体管技术。

根据三星的说法,与7nm制造工艺相比,3nm GAA技术的逻辑面积效率提高了45%以上,功耗降低了50%,性能提高了约35%,纸面参数上来说却是要优于台积电3nm FinFET工艺。

当然,这些还是纸面上的,三星的3nm工艺挑战也不少,光是量产就是个问题,之前三星宣传2021年就量产,实际上并没有,最快也是今年,而且首发的是3GAE

据韩国媒体报道,三星已经准备在韩国平泽市的P3工厂开工建设3nm晶圆厂了,6、7月份动工,并及时导入设备。

按照这个进度,今年的3GAE工艺应该也只会是小规模试产,大规模量产也要到明年了,跟台积电的3nm工艺差不多,两家都因为种种问题延期量产3nm工艺了。

那么,究竟什么是 GAA 呢?下面就和大家一起了解一下。

晶体管技术的迭代历史

我们可以将晶体管理解为一种类似于“水龙头”的电子器件,主要用于控制电流(水流)的大小以及开关。由于晶体管对电流的控制是通过对栅极施加一个电压,从而在通道内部产生一个电场,用来调节源极和漏记之间电流的大小,所以它的全称是“场效应晶体管”(即FET,Field Effect Transistor)。

判定一个水龙头优劣的重要指标就是对水流的管控能力,决定FET场效应晶体管(下文简称晶体管)效率的重要因素同样是栅极对通道的控制能力。

平面型晶体管的物理瓶颈

在过去的很长一段时间里都是平面型晶体管的天下,它在通电后,电流会从Source(源极)流入Drain(漏级),而Gate(栅极)就相当于闸门,主要负责控制两端源极和漏级的通与断。在电流通过栅极时会出现耗损,表现形式为更高的发热和功耗,而耗损的程度则取决于栅极的宽度,栅极越窄,功耗越低,栅极越宽功耗越高。

一般来说,晶体管栅极的最小宽度(栅长),就是我们念叨的XX nm工艺中的数值。比如28nm,就代表管的栅长就是28,每一次制程工艺的迭代,本质上就是不断降低晶体管栅极宽度的过程。

问题来了,平面型晶体管受制于物理结构,它只能在闸门的一侧控制电流的接通与断开,而且它的栅极宽度不可能无限制的缩窄,当宽度接近20nm时,栅极对电流的控制能力将出现断崖式下降,业内将其称为“沟道长度变短导致的所谓短沟道效应”,从而出现严重的电流泄露(漏电)现象,最终让芯片的发热和耗电失控。

鳍式场效应晶体管参与救场

为了解决平面型晶体管栅极宽度的物理瓶颈,一种名为FinFET(Fin Field-Effect Transistor)的鳍式场效应晶体管技术参与救场。

顾名思义,FinFET最大的特色就是将晶体管的结构从平面变立体,对栅极形状进行改制,闸门被设计成类似鱼鳍的叉状3D架构,位于电路的两侧控制电流的接通与断开,大幅度提升了源极和栅极的接触面积,减少栅极宽度的同时降低漏电率,让晶体管空间利用率大大增加。

同时,由于FinFET的源极和漏极是在栅极做好之后直接在鳍上外延生长(Source-Drain Epitaxy),在栅极的阻断下不会出现扩散层,因此不会再出现平面型晶体管要命的短沟效应问题。

英特尔最早将FinFET技术应用到了自家的22nm制程工艺上,台积电和三星陆续跟进,并从16nm/14nm FinFET一直沿用到现在最新的5nm FinFET。

问题又来了,当制程工艺跨过5nm门槛后将会出现一系列新的问题。比如,随着栅极宽度的进一步缩小,很难再像过去那样在一个单元内填充多个鳍线,而鳍式场效应晶体管的静电问题也会严重制约晶体管性能的进一步提升。换句话说,FinFET在5nm时代就已逼近极限,想生产更具能效比的3nm和2nm工艺,需要下一代晶体管技术救场。

环绕栅极晶体管迎战未来

GAA 全称 Gate-All-Around ,是一种环绕式栅极技术晶体管,也叫做 GAAFET。它的概念的提出也很早,比利时 IMEC Cor Claeys 博士及其研究团队于 1990 年发表文章中提出。

其实 GAAFET 相当于 3D FinFET 的改良版,这项技术下的晶体管结构又变了,栅极和漏极不再是鳍片的样子,而是变成了一根根 “小棍子”,垂直穿过栅极,这样,栅极就能实现对源极、漏极的四面包裹。

看起来,好像原来源极漏极半导体是鳍片,而现在栅极变成了鳍片。所以 GAAFET 和 3D FinFET 在实现原理和思路上有很多相似的地方。

不管怎么说,从三接触面到四接触面,并且还被拆分成好几个四接触面,显然,这次栅极对电流的控制力又进一步提高了。

此外,GAA 的这种设计也可以解决原来鳍片间距缩小的问题,并且在很大程度上解决栅极间距缩小后带来问题,例如电容效应等。

更复杂的制造难度

虽然GAA FET取代FinFET已成业内共识,但现阶段影响其量产普及的因素还有不少,其中最关键的就是更复杂的制造流程,良品率和成本难以控制。在晶圆的生产过程中,蚀刻垂直侧壁上的器件最是困难,需要引入更新的半导体材料,使用EUV进行多次蚀刻,还需解决可能出现的隐藏缺陷,比如纳米片之间的残留物、纳米片的损坏或纳米片本身相邻的源→漏极区的选择性损坏、沟道释放需要单独控制片材高度、拐角侵蚀和沟道弯曲等。

纳米片结构的GAA FET工艺流程

GAA 技术的推进,在很大程度上推进半导体工艺特别是先进制程上的发展。但随着制程技术越来越接近物理极限,想要把芯片继续做薄做小,先进制程也并不是唯一的道路,材料、封装等也都可以称为突破的道路。

来源:Cfan、IT之家等网络内容综合

推荐阅读

添加微信回复“进群”

拉你进技术交流群!

国产芯|汽车电子|物联网|新能源|电源|工业|嵌入式…..

在公众号内回复您想搜索的任意内容,如问题关键字、技术名词、bug代码等,就能轻松获得与之相关的专业技术内容反馈。快去试试吧!

如果您想经常看到我们的文章,可以进入我们的主页,点击屏幕右上角「三个小点」,点击「设为星标」。