在本文中,我们将研究 Verilog 模块的基本结构,查看一些使用 Verilog “wire”数据类型及其向量形式的示例,并简要介绍 VHDL 和 Verilog 之间的一些区别。

Verilog和VHDL是常用来描述数字电路的两种语言。在前一篇文章中我们讨论VHDL 的基本概念。本文是我们关于 Verilog 的系列文章的起点。

在开始讨论之前,让我们先解决一个显而易见的问题:我们真的需要同时了解这两种语言吗?

Verilog 和 VHDL 都是强大的工具,可用于设计复杂的数字电路。尽管这两种 HDL 之间存在一些差异,但您可以自由选择其中一种来掌握和使用。但是,我相信在某些时候,您将受益于至少对这两种语言有基本的了解。有时作为设计师,我们需要一个示例代码段来了解如何编写项目。我们在网上冲浪了几个小时,终于找到了我们需要的东西,但这对我们来说毫无意义——它是用我们完全不熟悉的 HDL 编写的。如果没有对语言的基本了解,我们可能无法完全理解这些技术。

Verilog 由 Gateway Design Automation 于 1984 年初设计(大约在美国国防部发起 VHDL 三年后)。在 DoD 的支持下,VHDL 于 1987 年成为 IEEE 标准。Verilog 直到 1995 年才进入现场。今天,VHDL 和 Verilog 都是流行的 HDL,FPGA 设计工具通常支持这两种语言。

“Verilog”这个词是“验证”和“逻辑”这两个词的组合,因为该语言最初被建议作为一种模拟和验证工具。让我们开始了解 Verilog 的概念和语法。

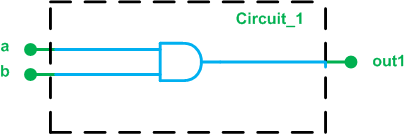

作为第一个示例,让我们为图 1 所示的电路编写 Verilog 代码。

有两个输入和一个输出。端口都有一点宽。该电路的功能是对两个输入进行“与”运算并将结果放在 out1 端口上。

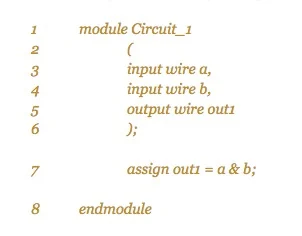

Circuit_1 模块的一种可能的 Verilog 描述是:

这两行使用关键字“module”和“endmodule”来指定中间的行(第 2 到 7 行)都描述了一个名为“Circuit_1”的电路。这个名字是任意的,允许我们稍后引用这个电路。

这些行指定“Circuit_1”与其周围环境的接口。输入和输出端口使用关键字“输入”和“输出”来描述。这些关键字之后是另一个关键字“wire”,然后是端口名称(参见图 1)。关键字“wire”指定了什么?“连线”是一种 Verilog 数据类型,表示设计中的物理连线。我们将在以后的文章中更详细地讨论 Verilog 数据类型,但现在,我们知道在我们的模块中将有称为 a、b 和 out1 的三根线,并且由于它们在端口声明中指定,它们对应于模块接口。

该行使用按位与运算符,即 &,来描述电路的功能。关键字“assign”将 a&b 放在输出端口 out1 上。这种类型的分配称为连续分配。之所以这样调用,是因为每当右侧的操作数发生变化时,赋值始终处于活动状态,a&b 被评估并分配给 out1。我们可以将连续分配设想为一个组合电路,其输出根据其输入而不断更新。在我们的例子中,这个组合电路是一个简单的与门。Verilog HDL 中还有一些程序分配,将在以后的文章中讨论。

现在,我们可以使用 Xilinx ISE 等软件包来验证上述代码。您可以在此处找到该软件的基于 Verilog 的教程 (PDF)。

下面的图 2 显示了 Circuit_1 模块的 Verilog 和 VHDL 描述。

如您所见,在使用 VHDL 编码时,我们必须包含一些库。这些库给出了数据类型和运算符的定义。考虑到这些库的添加和 VHDL 的一般格式,我们观察到 VHDL 代码更加冗长。然而,这种冗长并非没有优点。例如,VHDL 的库管理功能在对更高级别的系统进行建模时会很有帮助。在以后的文章中,我们偶尔会讨论这两种 HDL 的优缺点。

大多数 Verilog 数据类型使用四个基本值。清单 1 中定义的连线可以采用以下值之一:

0:逻辑低或假条件

1:逻辑高或真条件

z:为高阻态(可用于描述一个三态缓冲器的输出)

x:对于无关值或未知值(当输入未初始化或两个或多个冲突输出连接在一起时)。

VHDL std_logic 数据类型可以采用九个不同的值,但其常用值是“0”、“1”、“Z”和“-”(“-”表示不关心)。

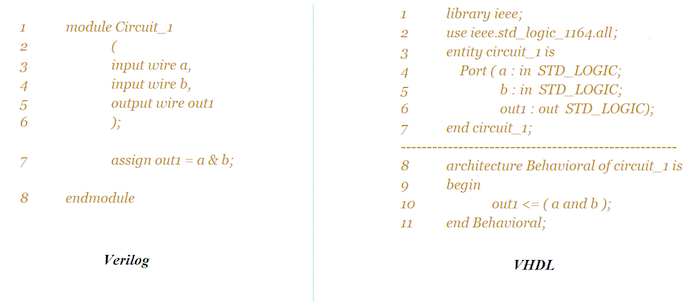

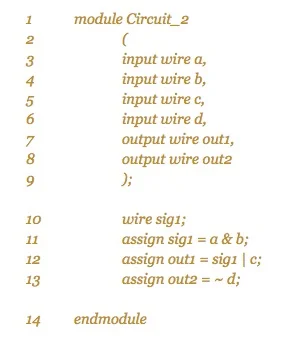

作为另一个例子,让我们为图 3 所示的电路(我们将标记为 Circuit_2)编写 Verilog 代码。

下面的 Verilog 代码描述了这个电路:

上述代码中使用的元素与示例 1 中的元素类似,只是在代码的第 10 行中定义了一个内部信号。关键字“wire”用于指定此连接的数据类型。如上所述,“线”数据类型将转换为设计中的物理线。

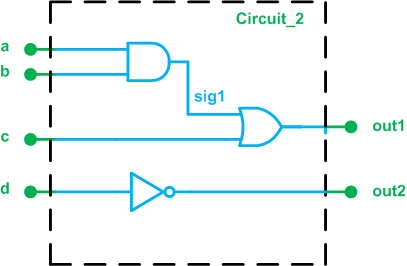

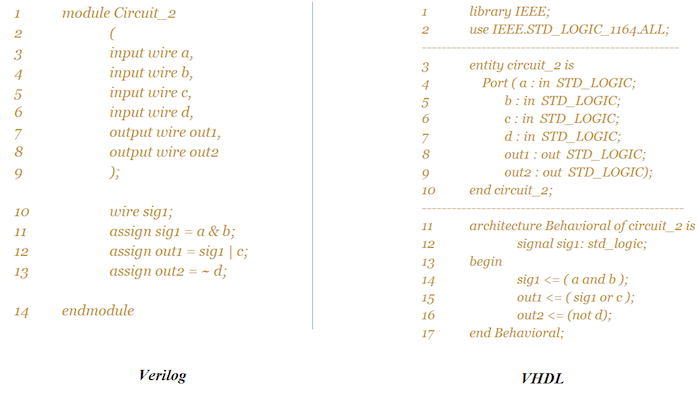

上面的代码还使用了一些新的 Verilog 位运算符:~ 表示 NOT 和 | 用于 OR 操作。另一个有用的按位运算符是 XOR 运算的 ^。图 4 显示了 Circuit_2 模块的 Verilog 和 VHDL 描述。这样的比较可以帮助您了解这两种语言之间的差异和相似之处。

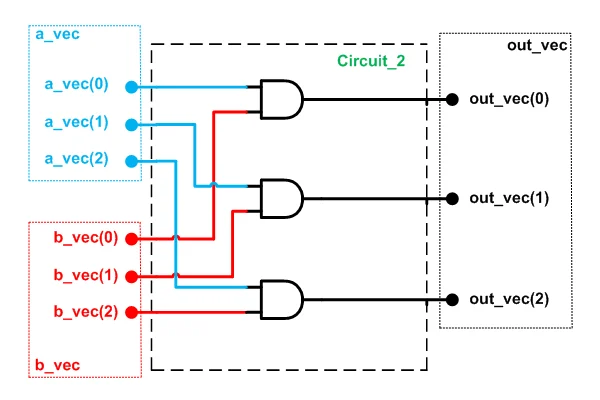

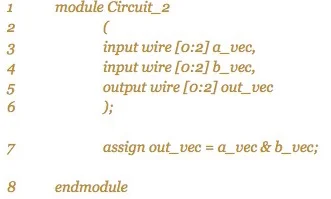

对于我们的第三个也是最后一个示例,我们将为图 5 所示的原理图提供 Verilog 代码。

如您所见,蓝色输入端口和红色输入端口之间存在一定的关系:对应的输入与 AND 运算符组合。结果分配给输出端口。在这种情况下,我们可以将信号分组并将它们视为向量。这使得代码紧凑且可读。

使用 Verilog 中的向量概念,我们可以轻松地扩展清单 1 中的代码来描述上述电路(参见下面清单 3 中的代码)。

请注意,向量的索引范围可以是升序(如上使用的 [0:2])或降序([2:0])。尽管上面使用了升序格式,但使用降序格式通常不太容易出错。这是因为降序样式符合我们的看法,即二进制数的最左边位置具有最高索引。请注意,向量也在 VHDL 中使用。

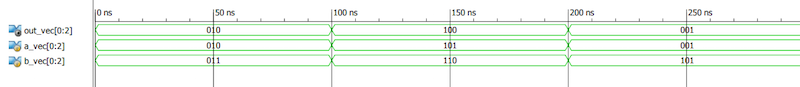

下面的图 6 显示了清单 3 中代码的 ISE 模拟。

在本文中,我们讨论了同时学习 VHDL 和 Verilog 是一个好主意,我们研究了 Verilog 模块的基本结构,并且我们熟悉了 Verilog “wire”数据类型及其向量形式。我们还简要介绍了 VHDL 和 Verilog 之间的一些区别。Verilog 系列的下一篇文章将讨论在 Verilog 中设计组合电路。

今天小编带来了:ISSCC2022套餐,里面有文章、PPT、Tutorial等,同学可以拿回去自己学习研究。

1、深入理解SerDes(Serializer-Deserializer)之一

2、深入理解SerDes(Serializer-Deserializer)之二

3、科普:深入理解SerDes(Serializer-Deserializer)之三

4、资深工程师的ESD设计经验分享

5、干货分享,ESD防护方法及设计要点!

6、科普来了,一篇看懂ESD(静电保护)原理和设计!

7、锁相环(PLL)基本原理 及常见构建模块

8、当锁相环无法锁定时,该怎么处理的呢?

9、高性能FPGA中的高速SERDES接口

10、什么是毫米波技术?它与其他低频技术相比有何特点?

11、如何根据数据表规格算出锁相环(PLL)中的相位噪声

12、了解模数转换器(ADC):解密分辨率和采样率

13、究竟什么是锁相环(PLL)

14、如何模拟一个锁相环

15、了解锁相环(PLL)瞬态响应

16、如何优化锁相环(PLL)的瞬态响应

17、如何设计和仿真一个优化的锁相环

18、锁相环(PLL) 倍频:瞬态响应和频率合成

19、了解SAR ADC

20、了解 Delta-Sigma ADC

21、什么是数字 IC 设计?

22、什么是模拟 IC 设计?

23、什么是射频集成电路设计?

24、学习射频设计:选择合适的射频收发器 IC

25、连续时间 Sigma-Delta ADC:“无混叠”ADC

26、了解电压基准 IC 的噪声性能

27、数字还是模拟?I和Q的合并和分离应该怎么做?

28、良好通信链路性能的要求:IQ 调制和解调

29、如何为系统仿真建模数据转换器?

30、干货!CMOS射频集成电路设计经典讲义(Prof. Thomas Lee)

31、使用有效位数 (ENOB) 对 ADC 进行建模

32、以太网供电 (PoE) 的保护建议

33、保护高速接口的设计技巧

34、保护低速接口和电源电路设计技巧

35、使用互调多项式和有效位数对 ADC 进行建模

36、向 ADC 模型和 DAC 建模添加低通滤波器

37、揭秘芯片的内部设计原理和结构

38、Delta-Sigma ADCs中的噪声简介(一)

39、Delta-Sigma ADCs中的噪声简介(二)

40、Delta-Sigma ADCs 中的噪声简介(三)

41、了解Delta-Sigma ADCs 中的有效噪声带宽(一)

42、了解Delta-Sigma ADCs 中的有效噪声带宽(二)

43、放大器噪声对 Delta-Sigma ADCs 的影响(一)

44、放大器噪声对 Delta-Sigma ADCs 的影响(二)

45、参考电压噪声如何影响 Delta Sigma ADCs

46、如何在高分辨率Delta-Sigma ADCs电路中降低参考噪声

47、时钟信号如何影响精密ADC

48、了解电源噪声如何影响 Delta-Sigma ADCs

49、运算放大器简介和特性

50、使用 Delta-Sigma ADCs 降低电源噪声的影响

51、如何设计带有运算放大器的精密电流泵

52、锁定放大器的基本原理

53、了解锁定放大器的类型和相关的噪声源

54、用于降低差分 ADC 驱动器谐波失真的 PCB 布局技术

55、干货!《实用的RFIC技术》课程讲义

56、如何在您的下一个 PCB 设计中消除反射噪声

57、硅谷“八叛徒”与仙童半导体(Fairchild)的故事!

1、免费公开课:ISCAS 2015 :The Future of Radios_ Behzad Razavi

2、免费公开课:从 5 微米到 5 纳米的模拟 CMOS(Willy Sansen)

3、免费公开课:变革性射频毫米波电路(Harish Krishnaswamy)

4、免费公开课:ESSCIRC2019-讲座-Low-Power SAR ADCs

5、免费公开课:ESSCIRC2019-讲座-超低功耗接收器(Ultra-Low-Power Receivers)

6、免费公开课:CICC2019-基于 ADC 的有线收发器(Yohan Frans Xilinx)

7、免费公开课:ESSCIRC 2019-有线与数据转换器应用中的抖动

8、免费公开课:ISSCC2021 -锁相环简介-Behzad Razavi

9、免费公开课:ISSCC2020-DC-DC 转换器的模拟构建块

10、免费公开课:ISSCC2020-小数N分频数字锁相环设计

11、免费公开课:ISSCC2020-无线收发器电路和架构的基础知识(从 2G 到 5G)

12、免费公开课:ISSCC2020-从原理到应用的集成变压器基础

13、免费公开课:ISSCC2021-射频和毫米波功率放大器设计的基础

摩尔学堂(www.moorext.com)--摩尔学堂专注于半导体人才培训,在线学习服务平台!