点击上方蓝字

关注我们!

在 TI 上一代 Jacinto 6 汽车处理器中,例如 DRA7x/TDA2x,为了实现性能与功能安全的综合考虑,提供了名为 DVFS (Dynamic Voltage Frequency Scaling) 的机制,使能系统能够实时获取芯片 thermal 状态,并动态反馈调节系统电压与运行频率,使得系统运行在安全温度范围内,实现性能最大化。

在 TI 最新一代 Jacinto™ 7 处理器中,例如 DRA8x/TDA4x,目前外部 PMIC 输出电压 NVM 固定,故推荐使用 DFS 来实现在固定电压下的频率调节,从而实现对整芯片热状态的检测以及控制。

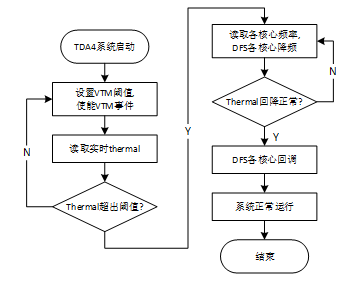

图 1:TDA4 动态热检测与控制流程图

在得到温度报警事件后,通过对 TDA4 内部各核心运行状态以及运行频率的读取,能够在系统正常运行范围内,动态调整各核心的运行频率,从而降低系统功耗,实现对系统热状态的控制。

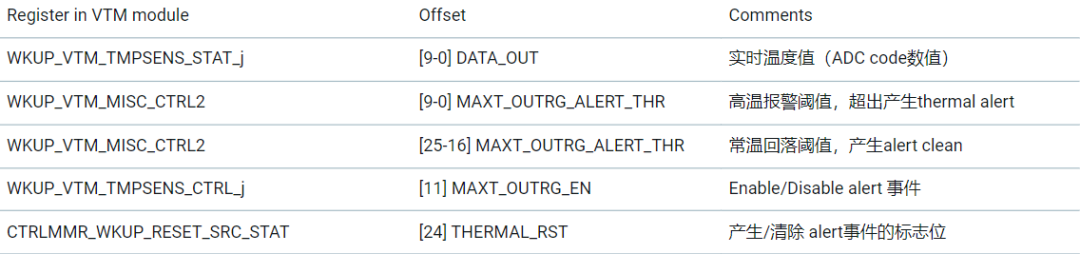

首先需要动态读取 SOC thermal 温度值,VTM 可以用来读取温度值以及设置温度报警阈值等,其详细介绍参照 TDA4 TRM 手册。其核心寄存器配置如表 1 所示:

表 1:VTM 寄存器设置

读出来的 DATA_OUT 值为内部 ADC 数值,需要进行转换才能成为摄制温度值,其转换方式如图 2 所示:

图 2:VTM ADC code 与温度值计算关系表

Patch 能够实现在 Linux 端对内部核心的 thermal 温度值读取。步骤如下:

a. 下载 Linux SDK8.0 并参照 guide 制作 SD 启动卡,并下载对应 thermal patch。

b. 参照下述流程安装到原生 SDK 中。

cd $PSDK_PATH/board-support/linux-*

git am 0001-display-temperature-as-mili-celsius.patch

cd ../..

make linux

c. 参照下述流程将编译后的文件更新至 SD 卡系统中。

Edit the file $PSDK_PATH/Rules.make

Set DESTDIR=/media/$USER/rootfs

cd $PSDK_PATH

sudo make linux_install

d. 参照下述流程进行验证

cat /sys/class/thermal/thermal_zone*/temp

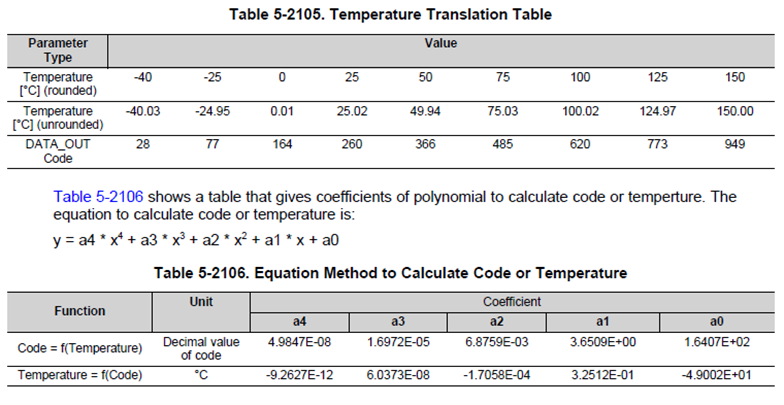

其中 patch 一共添加了五个域中 kernel 的温度值,其打印如图 3 所示:

图 3:thermal 温度值读取

其中对应了五个 Linux 中的设备节点,所输出的值单位为毫摄氏度,例如图 3 中所示结果以及硬件对应关系为:

thermal_zone0 -> WKUP domain DMSC core -> 67.640℃

thermal_zone1 -> MAIN domain MPU A72 core -> 68.074℃

thermal_zone2 -> MAIN domain C7x core -> 68.507℃

thermal_zone3 -> MAIN domain GPU core -> 69.371℃

thermal_zone4 -> MAIN domain R5F core -> 68.074℃

获取到 TDA4 内部各个核心实时的 thermal 值后,可以通过上层逻辑对读取到的温度值与预设的报警阈值进行逻辑比较,然后采取对应的措施进行核心频率调整。

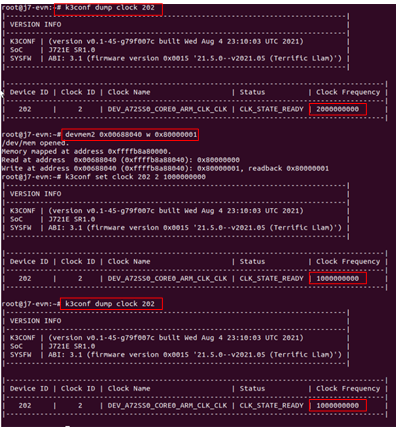

在 TDA4 默认文件系统中,提供 k3conf 通过指定的 device ID 以及 clock ID 来实现对各个核心频率的读取以及控制。

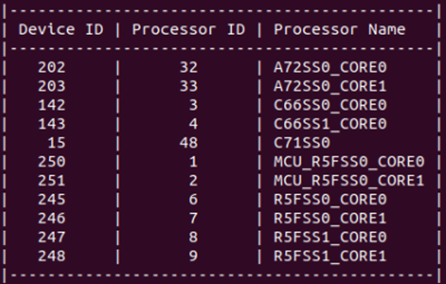

Device ID的获取

扫描下方二维码,可通过 TISCI 手册 J721E 部分对各个模块的 device ID 进行查询。

图 4 中列出了常用几个核心的 device ID。

图 4:processor device ID

Clock ID的获取

为了标识在一个核心中多个不同模块的频率设置,引入了 clock ID 对其进行区分。扫描下方二维码,可在 TISCI J721E 部分对 clock ID 进行查询。

对应核心运行频率检测

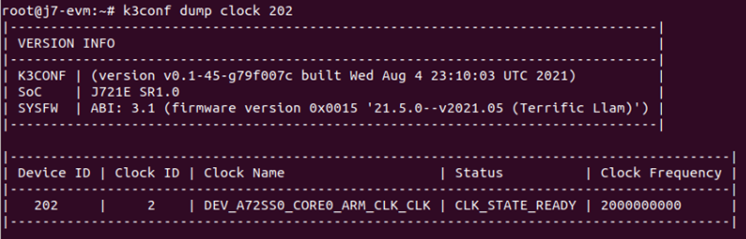

获取到对应核心 device ID 后,可通过下述指令打印出当前对应核心的运行频率。

k3conf dump clock DEVICE_ID

以 A72_CORE0 为例,可以得到其当前运行频率为 2GHz 如图 5 所示。

图 5:A72 CORE0 运行频率

设置对应核心运行频率

若按照第三章中的流程计算,当前运行频率需要进行调整,可使用下述指令对当前指定 device ID 以及 clock ID 的模块进行频率控制。在对其核心频率进行修改之前,需要首先对其对应的锁相环进行修改,以 A72_CORE0 核心为例:

devmem2 0x00688040 w 0x80000001

k3conf set clock 202 2 1000000000

其修改过程如图 6 所示:

图 6:A72 CORE0 频率修改流程

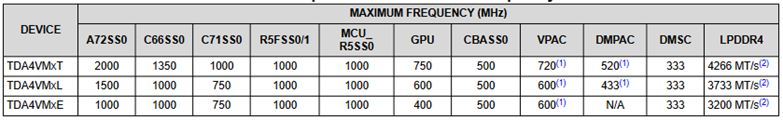

其中每个 TDA4 内部核心所支持的最大频率受硬件限制,以 TDA4VM 为例,如图 7 所示为不同 PN 中各核心所支持的最大频率。

图 7:TDA4VM 中各核心所支持最大频率

同样的,在最大频率之下,各核心的频率设置并非随机设置,其必须满足内部分频器等硬件时钟要求。

如需获取更多在线技术支持,请访问 TI E2E™ 中文支持论坛 (e2echina.ti.com)。

点击“阅读原文”,进入 TI E2E™ 中文支持论坛阅读更多技术文章!