N分频就是把频率变为1/N。周期变为N倍。

石英晶体加电后产生压电反应,在固定频率振动,产生出电压按照固定周期变化的脉冲信号。高频率信号通向分频器frequency divider,转换为低频信号。

N倍频就是把频率变为N倍。周期变为1/N倍。

在现代通信中,人们需要更高更稳定的输出频率。尽管LC振荡器可以工作到较高的频率,但是稳定度不高,而晶体振荡器有较高的稳定度和准确度,只是基频较低。

在现代无线通信中,频率合成技术(例如锁相技术PLL)可以从低频的晶体振荡器中获得高稳定的高频信号。

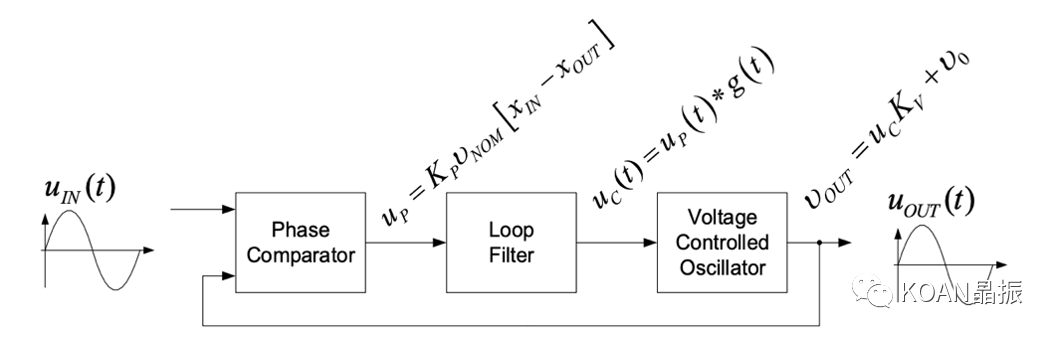

锁相环电路是闭环的反馈控制系统。PLL由以下几部分组成:

Phase Comparator鉴相器/相位比较器:对输入的基准信号和反馈回路的信号进行频率比较。

Loop Filter回路滤波器:由分频器实现,将VCO的输出降低到和基准信号相同的级别频率

VCO压控振荡器:根据输入电压,输出对应频率的周期信号

Feedback Loop反馈回路

通过PLL,如何把4MHz的基准频率倍频到40MHz?

假设VCO先产生一个大概35MHz的频率,经过10倍分频后得到3.5MHz。VCO的输出通过反馈回路输入到相位比较器。比较得知3.5MHz小于4MHz,相位比较器输出一个电压(误差电压)。在经过滤波后,得到VCO的控制电压。

锁相环提高到38MHz。经过对比后,依然不足4M(>3.8MHz)。再不断通过负反馈处理,最终得到稳定的精度的时钟频率。

如果同时需要50M和100M,系统时钟选择50M还是100M?

采用100MHz晶振。

因为分频的时钟比倍频的时钟质量好,稳定性高。分频的电路比较简单。相比之下,倍频电路比较复杂,需要相位比较器,回路滤波器,压控振荡器,分频器等。