作者 | Stuart Cording(Elektor)

译者 | 禾沐

整个电子行业似乎都被RISC-V冲昏了头脑,这是为什么? RISC-V是什么? 如何能参与其中? 只要稍加了解,你就会知道大众所说的RISC-V 是一种新的处理器核,而且已经有一些采用RISC-V 处理器技术的芯片上市了。你也许还会知道RISC-V 是 “免费和开放”的,这正是RISC-V有庞大“粉丝群”的主要原因。在本文中我们将从技术角度来认识RISC-V。

首先,RISC-V 是一个指令集体系架构(Instruction SetArchitecture,ISA),并不是一个处理器。RISC-V 社区发布处理器的设计蓝图,帮助用户设计自己的处理器,在这里“设计”意味着将寄存器、累加器、数学运算器、内存总线和所有其他的部分组合在一起。ISA 文档记载支持的操作、内存寻址、栈、中断等技术细节,比如指令的位宽和操作数(operand)的位宽。

业界如此关注RISC-V的主要原因是RISC-V的免费和开放。开放意味着任何人都可以在项目中做出贡献;免费并不意味着设计处理器时不需要在硬件上投入成本,就像Arduino一样,Arduino开发板设计的开放和免费不意味着开发板本身是免费的。

RISC-V在和谁竞争?

每一个处理器都有一个ISA,绝大多数ISA都是私有的,个别是可授权的。Microchip公司生产的8/16位PIC处理器上有微芯专有的ISA,只能通过购买Microchip的微控制器取得这些处理器核。如果你想要搭建自己的微控制器,Arm 和MIPS是更现实的选择,这些核能够以知识产权(IntellectualProperty,IP)的形式授权。知识产权的拥有者在ISA 的基础上设计处理器,开发支持处理器的工具,并创建相关的基础设施,最终向你征收使用它们的费用。当这些选项不能满足你的需求时,事情就变得比较麻烦。

你的应用也许需要以最低的功耗快速完成一种任务(比如加密),一个可授权的IP也许能在100个指令之内完成这一任务,不过,为了降低功耗,需要找到一家专注于低功耗的半导体制造工厂,但这要比一般的制造过程昂贵得多,从而导致过高的产品定价。

你的手下也许有聪明的工程师能够创建新的指令、优化代码的执行时间,但如果ISA 是专有的就无法进行修改了。其结果就是你需要通过制造工艺解决处理器的性能问题,我们在后面会继续讨论这一话题。

“原厂”的RISC-V能够做些什么?

简单的回答是:足够用,但不是很多。首先,选择你需要的体系结构,目前仅有32位和64位供选择,128位的ISA还在研发之中。最基础的ISA 定义是RV32I和RV64I,字母“I”代表着整数(Integer)。RV32I中定义了49个指令,包括基础整数和逻辑运算(ADD、SUB、AND、OR、XOR)指令、位移、比较、跳跃、链接和一些系统指令。

如果需要代码压缩支持,那么还需要“C”选项,其中包括16位指令编码(同Arm 的Thumb模式类似)。其他可选的支持包括乘法和除法(M)、原子操作(A)和浮点数(F、D和Q)。

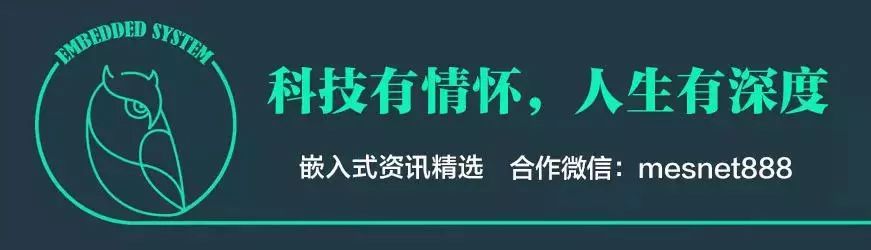

下一步是基于选项的技术规范、用硬件描述语言(HDL)设计你的处理器核,比如VHDL或者Verilog。设计处理器并不简单,社区中有许多个人和企业能够提供现成的设计。如果你想要走真正“免费”的路径,可以访问苏黎世理工和博洛尼亚大学合作的PULP 平台,它们的CV32E40P RV32IM[F]C 实现可以在GitHub上获得。如果你想要了解设计实现的过程,加州大学伯克利分校的BOOM 项目可供参考,它是一个为了体系结构研究而开发的高性能、可参数化的处理器核(见图1)。

图1 BOOM 项目的RISC-V处理器流水线实现及其版本演进

(来源:贝克利架构研究中心)

如果你想要快速设计自己的处理器核,并且需要技术支持,那么可能需要花一些钱从SiFive这样的公司授权取得它们的实现,SiFive提供许多可自定义的32/64 位RISC-V 处理器核设计。

如何试用RISC-V?

虽然RISC-V已经存在一段时间,但可供测试的处理器芯片并不是很多,RISC-V 对于业界而言依然很新。如果你对微控制器有所了解,就会知道整个行业基本上从专有核转移到了Arm,这是一项战略性长期投资。如果现在就转移到RISC-V,虽然企业可以节省支付Arm的版税,但用户得不到更多的好处。转移到RISC-V需要企业先培训开发团队,然后将现有IP(例如模拟电路设备、定时器、总线、界面和存储器)与RISC-V处理器核进行整合,并更新开发IDE、编译器、调试器等。

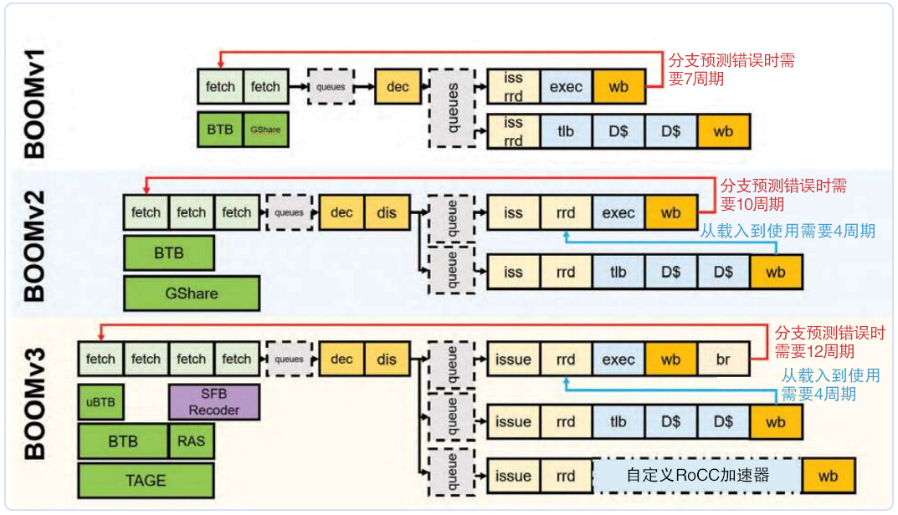

如果拥有希捷或者西部数据的硬盘,那么可能你已经在使用RISC-V处理器了。不过,你多半想要在RISC-V的处理器上运行代码,而不只是拥有内含RISC-V 的产品,能够达到这一目的的最快方式是通过ESEO 开发的emulsiV 这样的模拟器。模拟器使用名为“Virgule”的RISC-V内核实现(见图2),除了处理器外,模拟器还提供文本I/O、位图输出和一些通用I/O(GPIO)的支持。配套的样例包括加法、输出ASCII文字、控制GPIO、位图输出等,此外,模拟器还提供了“动画”选项(选项框在画面上方)来显示代码运行时数据的移动。你可以将“代码1”中的代码另存为program.hex,上传到模拟器上运行。

图2 emulsiV 模拟器让任何人都可以在浏览器内试用RISC-V

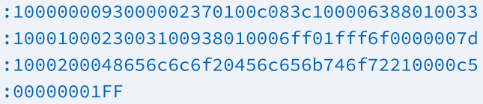

代码1 : 用来上传到emulsiV模拟器中的十六进制代码。

如果想要在Arduino 上体验RISC-V,可以从CrowdSupply上购买HiFive1 Rev B 开发板,其上搭载SiFive FE310 G002微控制器,提供一些基本数字外设(I2C、UART、SPI、PWM 和GPIO),包括了一些SRAM 和需要依靠芯片外的QSPI FLASH 的存储器。此外,开发板还包括Wi Fi和蓝牙模块,以及用于USB调试的SeggerJ Link接口。

在高性能处理器方面,现在有Microchip的PolarFireSoC,其上搭载4个64位RISC-V核和FPGA资源,从而提供了一个高度可定制的、能够在运行Linux的同时支持硬实时应用的平台。

如何定制RISC-V?

如前所述,RISC-V 的优点之一是可以针对应用需求对指令集进行微调,假设一个处理器能够满足95%的需求,你可以增加新的功能实现余下的5%。在下面的例子中,我们假设你的应用大量使用ChaCha流加密,参考Imperas(一家提供RISC-V 验证、分析和剖析工具的公司)的一个应用样例。

假设在一个RISC-V核上运行了ChaCha实现,然后发现用于计算的处理器时间很长,你既想要改善执行时间,也想通过减少运算时间来降低能耗。

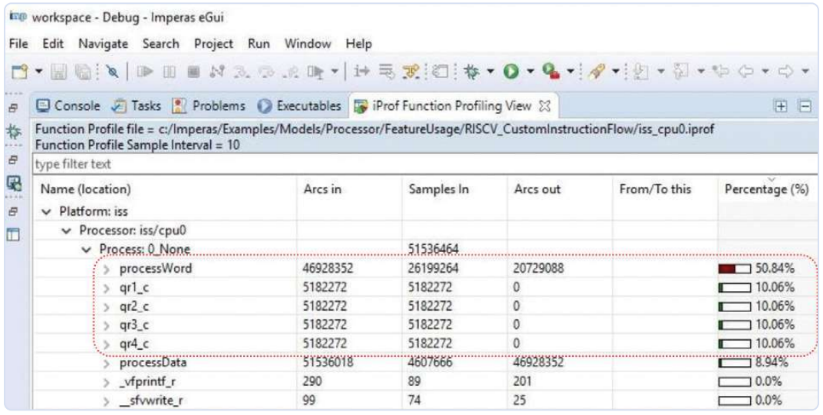

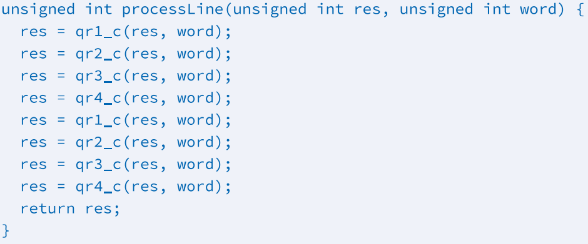

“代码2”在“quarterrounds”步骤中运用了XOR和位轮转,你可以看到4个qrX_c()函数调用。processLine()函数调用它们来完成加密。从分析可以看出,处理器花了大约55%的时间执行这一任务,这其中的大约32%是在4个qrX_c()“quarterround”函数中(见图3)。

图3 ChaCha流加密过程的C代码实现占用接近55%的处理器时间

(来源:ImperasSoftware Limited)

代码2 : 实现ChaCha流加密的C代码。

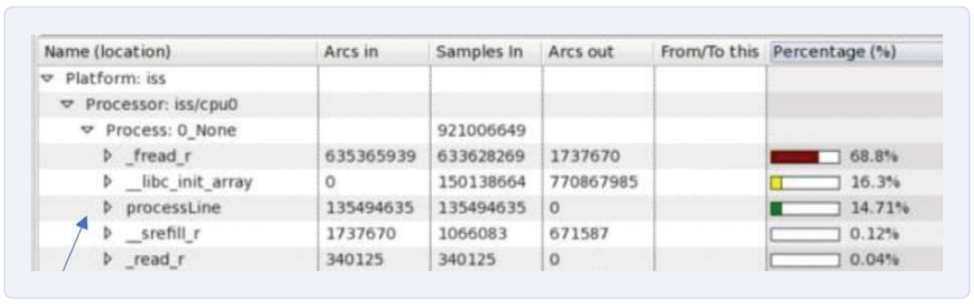

使用RISC-V技术,我们可以使用一条指令实现4个“quarter round”指令,每个指令只需要一个周期,而不用依赖于C编译器产生的代码。这是因为RISC-V ISA 中有一个为自定义指令预留的部分,刚开始我们在RISC-V设计中用C语言实现指令,从而允许我们模拟指令的功能并验证性能的优化效果。4个 “quarter round”指令帮助将processLine()的运算需求降低到处理器时间的15%(见图4)。如果符合需求,开发团队可以开始在Verilog中编写指令的硬件实现。

图4 通过新开发的专用指令,ChaCha流加密过程的处理器使用率降低到15%以下(来源:ImperasSoftware Limited)

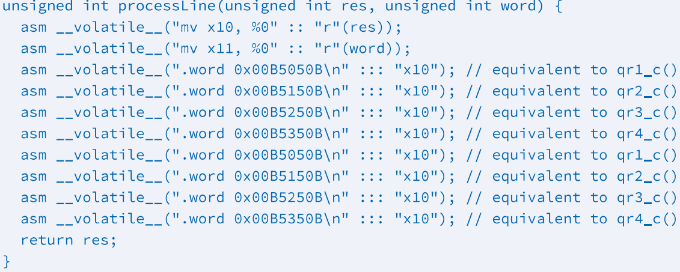

使用新的指令并不像重新编译C代码那样简单(见代码3),让RISC- V编译器能够使用新的指令是一项很大的工程。由内联汇编器调用的十六进制编码的指令,如同手工优化的代码一样好。

代码3 : 使用新的RISC-V指令需要内联汇编器,由于汇编器并不认识新指令的名称,因此指令用十六进制进行编码。

如何在RISC-V社区中做出贡献?

如果想要对RISC-V的开发有所贡献,可以有很多途径。RISC-V国际基金会(见图5)是维护和推广RISC-V的组织,个人可以作为社区成员,或者通过企业/大学成员加入社区。

图5 RISC-V国际的官方标志,该组织推广和支持RISC-V ISA的开发

如果想要看到很多使用RISC-V 的微控制器在市场上销售,现实恐怕会让你感到失望。兆易创新有一些芯片产品,一家来自俄罗斯的供应商有一些针对智能电表的方案。大的厂商对Arm的依赖根深蒂固,即使不需要支付处理器的版税,创业公司也很难在已经饱和的市场中竞争。

在专门的领域中,可定制的处理器核会有更大的用武之地,RISC-V产品化的可能性会更高,比如超低功耗应用。在中国,因为技术授权的限制,RISC-V 有着很高的人气,这样可以避免从美国引入知识产权。阿里巴巴宣布了12 nm 工艺的16核、64位、2 GHz RISC-V处理器,计划将它们用于服务器这样的基础设施中。欧洲处理器新方案正在研究Arm 和RISC-V(或者其他处理器核)结合的异构体系结构,目标是利用不同处理器核的优势完成不同的多核计算任务。

RISC-V并不是第一个免费、开放的处理器IP,但它无疑是有史以来最成功的。RISC-V 的历史、灵活性、开放的哲学、广泛的产业支持和学术界对其浓厚的兴趣,意味着它至少将会影响整个一代工程师的职业生涯。

相关链接

[1]https://www.geeksforgeeks.org/microarchitectureand-instruction-set-architecture/.

[2]https://en.wikipedia.org/wiki/RISC-V.

[3] RISC-VReference.https://raw.githubusercontent.com/jameslzhu/riscv-card/master/riscv-card.pdf.

[4] https://en.wikipedia.org/wiki/Hardware_description_language.

[5]https://pulp-platform.org/.

[6]https://github.com/openhwgroup/cv32e40p.

[7] 基于SystemVerilog的CV32E40P指令解码器实现.https://github.com/openhwgroup/cv32e40p/blob/master/rtl/cv32e40p_id_stage.sv.

[8]https://github.com/riscv-boom/riscv-boom.

[9]https://www.sifive.com/.

[10]https://scs.sifive.com/core-designer/.

[11]https://www.seagate.com/innovation/risc-v/.

[12]https://www.westerndigital.com/company/innovations/risc-v.

[13]http://tice.sea.eseo.fr/riscv/.

[14]https://www.crowdsupply.com/sifive/hifive1-rev-b.

[15]https://sifive.cdn.prismic.io/sifive%2F59a1f74ed918-41c5-b837-fe01ba7eaa1 _fe310-g002-manualv19p05.pdf.

[16]https://www.microsemi.com/product-directory/soc-fpgas/5498-polarfire-soc-fpga.

[17] ChaCha算法:https://en.wikipedia.org/wiki/Salsa20#ChaCha_variant.

[18]https://en.wikipedia.org/wiki/Stream_cipher.

[19]https://www.imperas.com/sites/default/files/documents/Imperas_RISCV_Custom_Instruction_Flow_Application_Note.pdf.

[20]https://riscv.org/about/.

[21]https://riscv.org/membership/.

[22]https://riscv.org/members/.

[23] 兆易创新GD32 RISC-V 微控制器.https://www.gigadevice.com/products/microcontrollers/gd32/risc-v/.

[24] 来自俄罗斯、基于RISC-V 的针对智能电表的K1986BK025微控制器:https://habr.com/en/company/milandr/blog/533322/.

[25]http://micromagic.com/.

[26] 关于阿里巴巴XT910 64位RISC-V核的更多信息.https://www.european-processor-initiative.eu/.

本文授权来自本刊的合作伙伴Elektor媒体集团,如果希望免费订阅Elektor 的英文在线内容,请访问https://www.elektormagazine.com/。

1.嵌入式行业那些坑与出路

2.一文搞懂 | Linux 驱动的来龙去脉

3.英伟达并购Arm要失败!老黄还要给孙正义12.5亿美元分手费

4.Intel加入RISC-V国际基金会~

5.这才是像样的C语言编程规范~~

6.为什么招聘单片机工程师的时候要求精通C/C++?