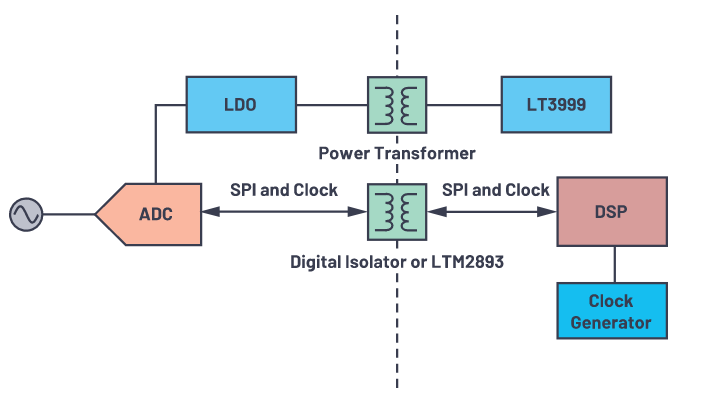

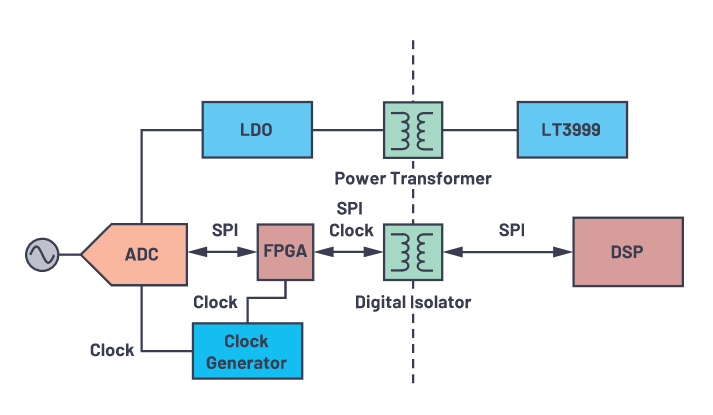

对于隔离式高性能ADC,一方面要注意隔离时钟,另一方面要注意隔离电源。SAR ADC传统上被用于较低采样速率和较低分辨率的应用。如今已有1 MSPS采样速率的快速、高精度、20位SAR ADC,例如 LTC2378-20 ,以及具有32位分辨率的过采样SAR ADC,例如 LTC2500-32 。将ADC用于高性能设计时,整个信号链都需要非常低的噪声。当信号链需要额外的隔离时,性能会受到影响。

关于隔离,有三方面需要考虑:

确保热端有电的隔离电源

确保数据路径得到隔离的隔离数据

ADC(采样时钟或转换信号)的时钟隔离,以防热端不产生时钟

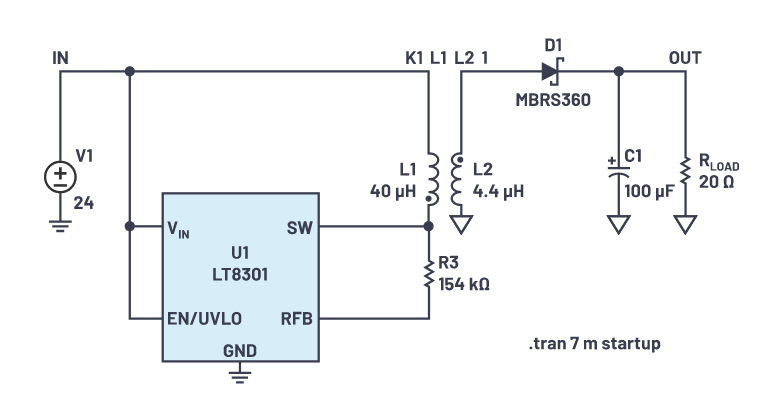

图1.典型的反激式转换器拓扑。

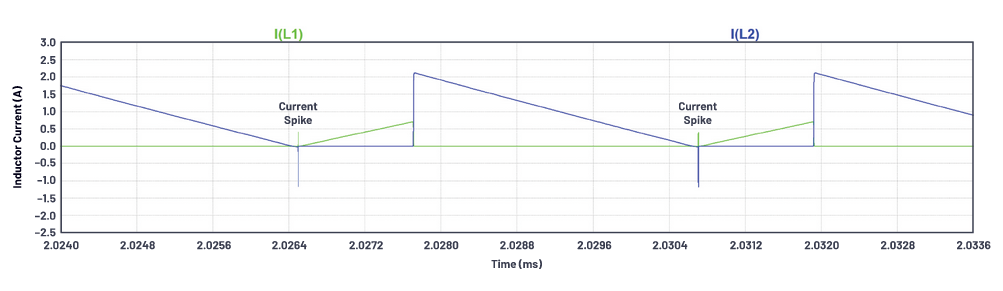

图2.LT8301在变压器绕组中切换电流。

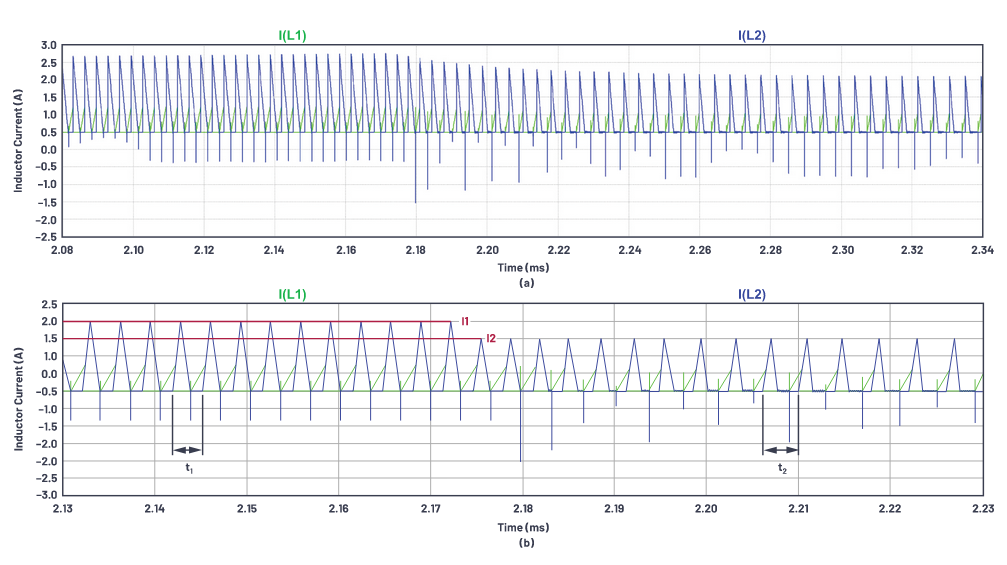

图3.(a) LT8301频率变化,(b)从2.13 ms到2.23 ms的频率变化的特写。

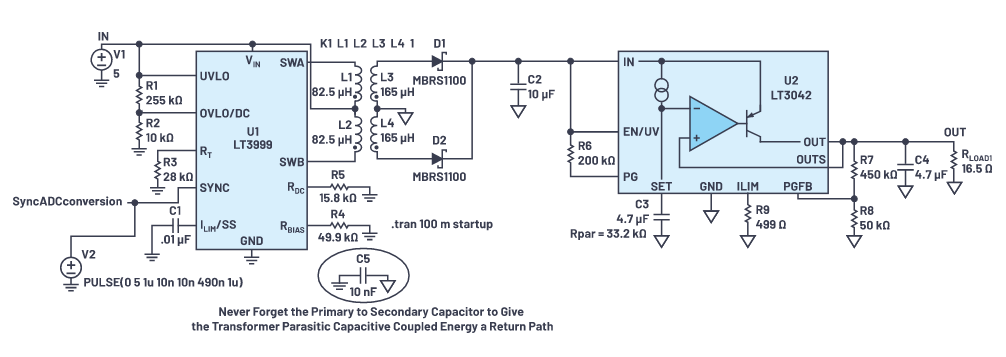

图4.具有超低噪声后置稳压器的LT3999。

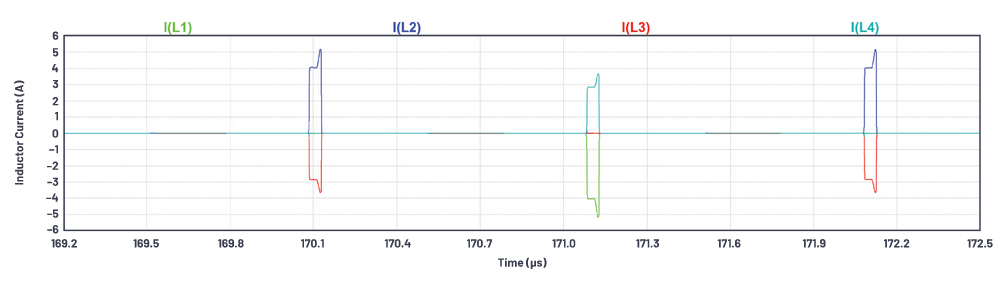

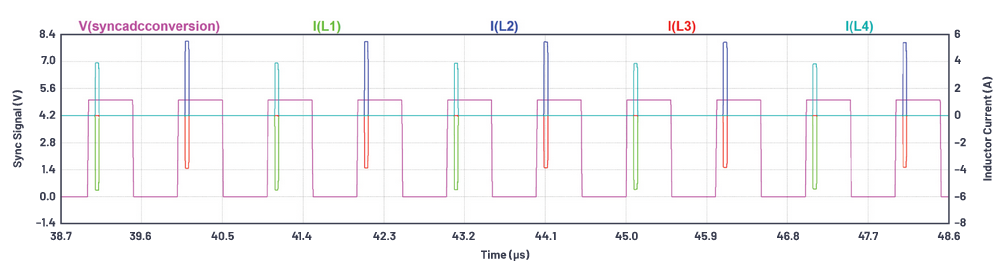

图5.LT3999电流波形。

图6.LT3999及其与同步引脚的切换关系。

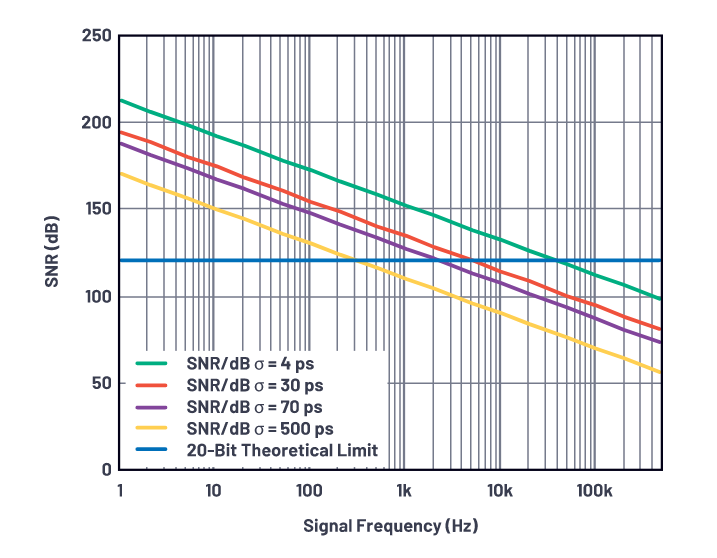

图7.时钟抖动与ADC性能的关系。

图8.使用标准隔离器实现时钟隔离。

像 ADuM250N 这样良好的标准数字隔离器的抖动为70 ps rms。对于100 dB SNR目标,由于时钟抖动,信号采样速率限制为20 kHz。

像 LTM2893 这样优化的时钟隔离器提供30 ps rms的低抖动。对于100 dB SNR目标,现在的信号采样速率为50 kHz,在全部SNR性能下可提供更多带宽。

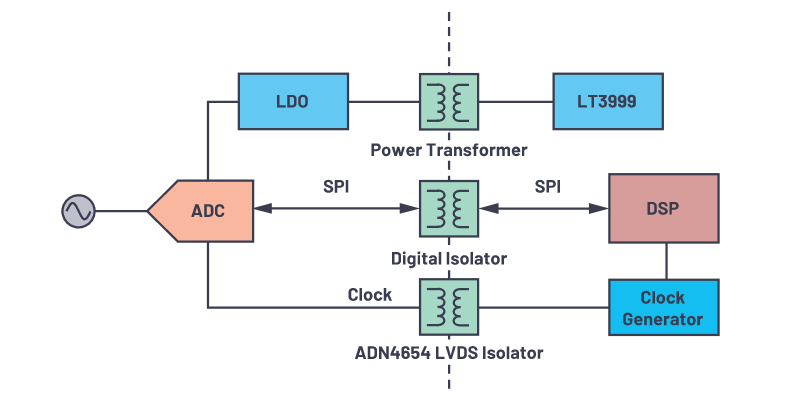

图9.使用LVDS时钟隔离器实现时钟隔离。

图9:对于更高的输入频率,应使用LVDS隔离器。ADN4654 提供2.6 ps抖动,接近ADC的最佳性能。在100 kHz输入时,时钟抖动导致的SNR限值将是110 dB。

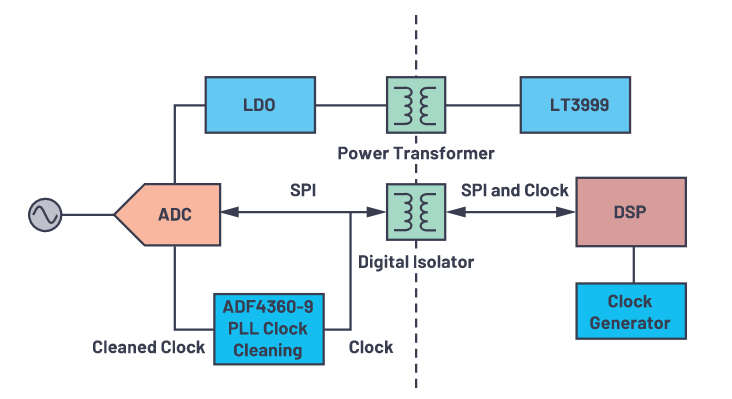

图10.使用额外PLL净化时钟抖动的时钟隔离。

图10:使用PLL净化时钟。ADF4360-9 可以帮助减少时钟抖动。

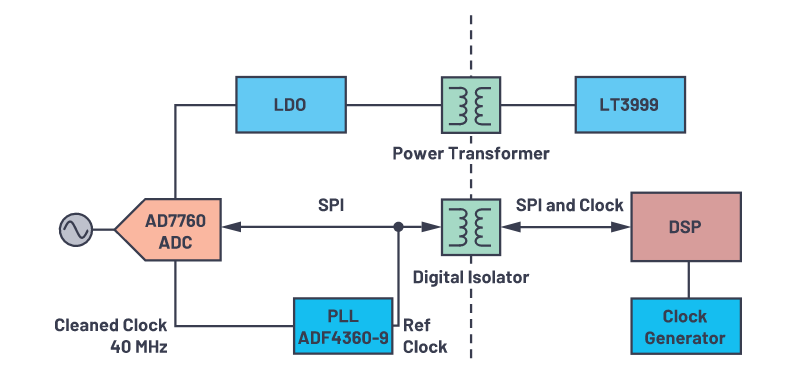

图11.ADF4360-9用作时钟净化器。

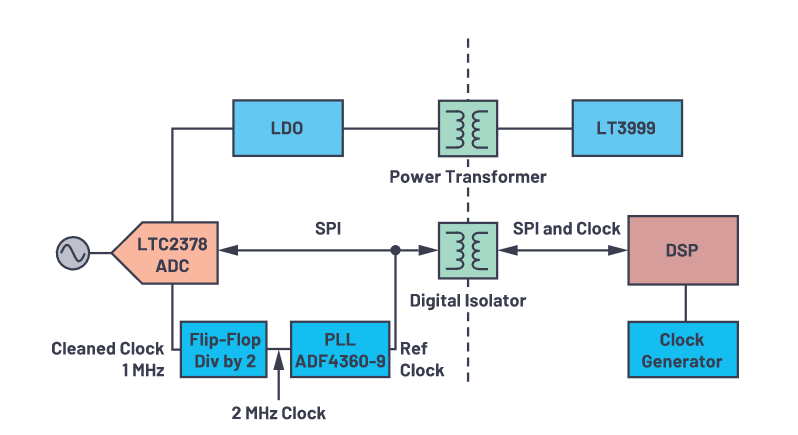

图12.触发器用于降低时钟以用于LTC2378。

图13.隔离(热)侧的时钟产生。

图13:本地产生时钟是获得具有所需抖动性能的时钟的另一个方案。本地时钟生成会使时钟架构更加复杂,因为它将异步时钟域引入系统。例如,若要使用两个单独的隔离ADC,则时钟的绝对频率将会不同,必须增加采样速率转换以重新匹配时钟。有关采样速率转换的一些细节,请参阅工程师对话笔记EE-268。

声明:

投稿/招聘/推广/宣传 请加微信:15989459034