来源 | 数字ICer

智库 | 云脑智库(CloudBrain-TT)

云圈 | 进“云脑智库微信群”,请加微信:15881101905,备注您的研究方向

声明 | 本号聚焦相关知识分享,内容观点不代表本号立场,可追溯内容均注明来源,若存在版权等问题,请联系(15881101905,微信同号)删除,谢谢。

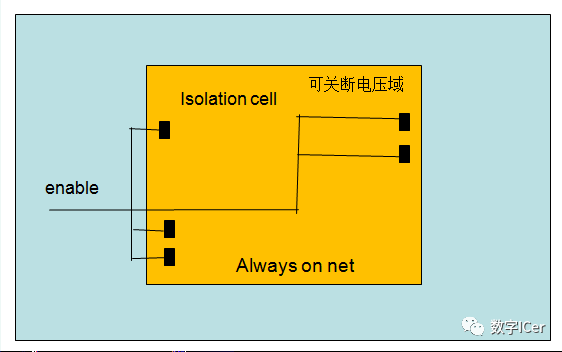

有些逻辑需要在关机期间保持活动状态,如Power Switch Cell、Retention Register Cells、Isolation Cells,他们就被称为Always-On Logic Cells。它可以不管voltage area的关断与否,一直保持常开的状态。

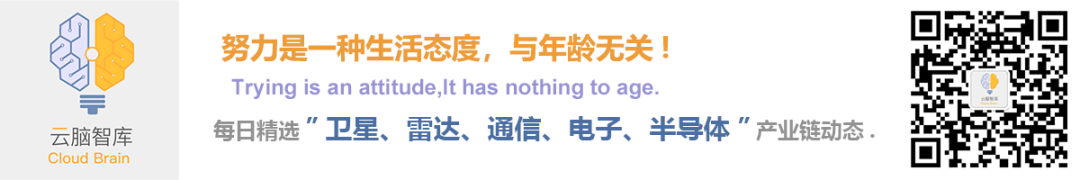

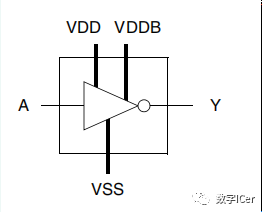

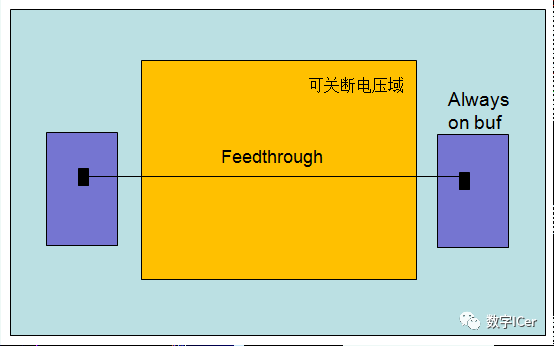

它与普通cell的区别在于,多了一个secondary power pin,这个second power pin必须连在always on stripe上。通常由于它的面积很大,而且secondary pg pin又占绕线资源,所以一般很少用它。它一般加在feedthrough net上比较多,也可以加SRPG cell的control端或者isolation cell的enable端

UPF文件描述always on buffer,如下所示:

define_always_on_cell -cells { VIAONPTBUFF} buffer cell名字

-ground {GND} primary ground pin

-ground_switchable {GNDINT} secondary ground pin

-power {VDD} primary power pin

在这些Cell的Liberty格式描述中就会有一个属性“always-on”是true。同时对于Always-On Logic Cells,pg_pin描述一般都会有两组,primary和backup,工具看到该cell为Always On,就会把2组电源地都接到长开的电源/地上。

cell(buffer_type_AO) {

always_on : true;

pg_pin(VDD) {

voltage_name : VDD;

pg_type : primary_power;

}

pg_pin(VDDB) {

voltage_name : VDDB;

pg_type : backup_power;

}

pg_pin(VSS) {

voltage_name : VSS;

pg_type : primary_ground;

}

...

pin (A) {

related_power_pin : VDDB;

related_ground_pin : VSS;

}

pin (Y) {

function : "A";

related_power_pin : VDDB;

related_ground_pin : VSS;

power_down_function : "!VDDB + VSS";

}

...

- The End -

版权声明:欢迎转发本号原创内容,转载和摘编需经本号授权并标注原作者和信息来源为云脑智库。本公众号目前所载内容为本公众号原创、网络转载或根据非密公开性信息资料编辑整理,相关内容仅供参考及学习交流使用。由于部分文字、图片等来源于互联网,无法核实真实出处,如涉及相关争议,请跟我们联系删除。我们致力于保护作者知识产权或作品版权,本公众号所载内容的知识产权或作品版权归原作者所有。本公众号拥有对此声明的最终解释权。

投稿/招聘/推广/合作/入群/赞助 请加微信:15881101905,备注关键词

“阅读是一种习惯,分享是一种美德,我们是一群专业、有态度的知识传播者.”

↓↓↓ 戳“阅读原文”,加入“知识星球”,发现更多精彩内容.

分享💬 点赞👍 在看❤️@以“三连”行动支持优质内容!