在十分复杂的芯片制作流程中,任何环节出现差池或失误都将导致研发成本提高,甚至延误产品的上市时间。只有经过严格、细致并快速的测试,才能保证每个阶段的顺利推进。芯片检测也逐渐成为集成电路产业中一个不可或缺的独立行业,为半导体产业链提供有力的技术支持。

谈起芯片测试和相关检测设备,自然无法绕过ATE(Automatic Test Equipment)。ATE即指可以利用自动化技术,针对产品进行快速测试。具体到半导体领域,是指在芯片制造过程中,用于CP(Chip Probe)和FT(Final Test)测试的设备。作为能够控制良率、提高效率与的重要测试仪器。ATE在半导体产业的重要地位已经日益凸显。

ATE面临效率、良率双重挑战

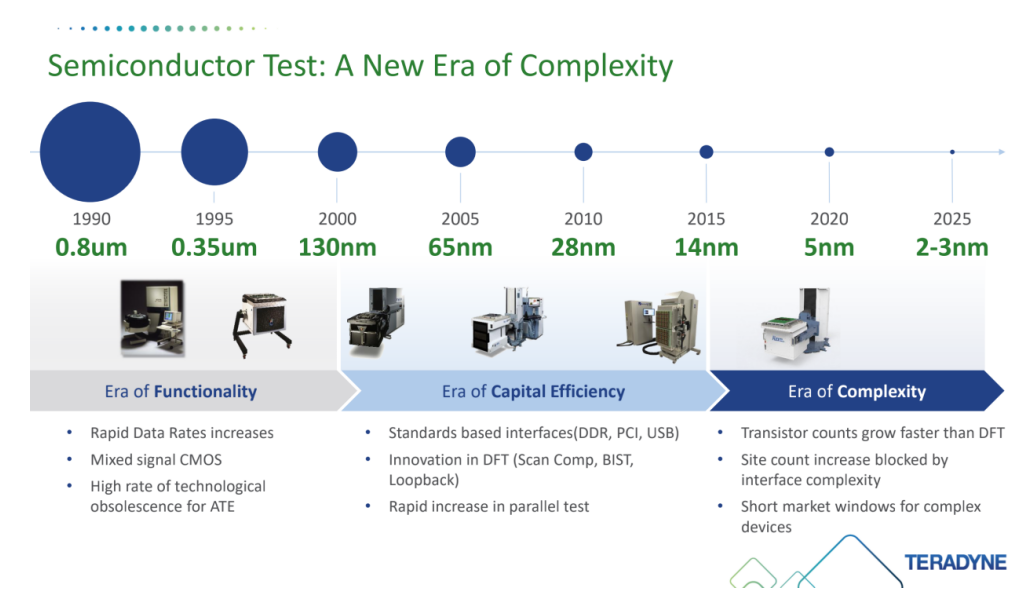

从1990年至2020年间,半导体工艺逐渐从0.8um下探至3nm,工艺尺寸越来越小,芯片上的晶体管集成度却越来越高,这也势必致使测试工作量、数据量呈指数级增长、芯片缺陷率有所上升。面对这一系列挑战,芯片测试技术不得不快速迭代、不断演进,以满足日趋复杂的测试需求。

泰瑞达中国区销售副总经理黄飞鸿曾表示:“随着芯片工艺尺寸不断缩,晶圆初次良率在不断下降,而芯片复杂度的提升也带来了测试时间的增加,时间就是成本。”由此可见,先进的制造工艺在赋予芯片更强大性能的同时,让芯片的测试成本大幅增加,而如何提升芯片测试效率,降低测试成本,已经成为当前半导体市场亟待解决的难题。

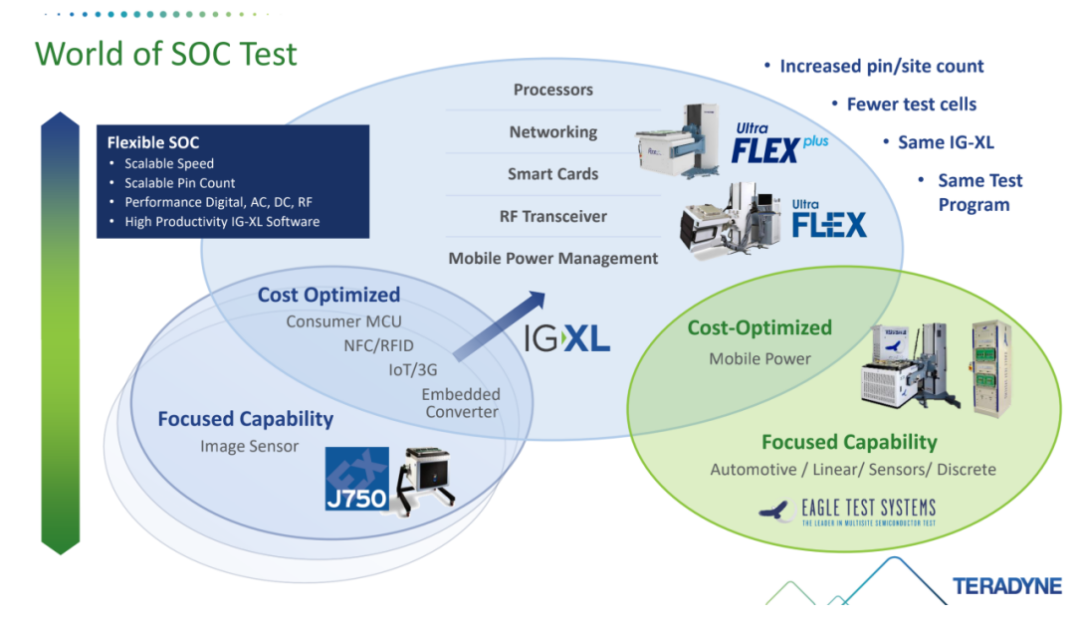

泰瑞达(TERADYNE)在ATE领域深耕多年,拥有雄厚的技术积累和完整的半导体测试解决方案。过去多年中,泰瑞达已经推出了多款测试设备,包括测试偏简单芯片的低成本解决方案J750和用来应对更高级别的测试需求的UltraFLEX系列。作为泰瑞达UltraFLEX家族的新成员,UltraFLEXplus是专为AI和5G网络部署中必不可少的处理器和ASIC芯片提供测试方案。

底层架构全新升级,良率效率可以兼得

在UltraFLEX系列测试平台的基础之上,UltraFLEXplus测试平台对芯片测试接口板进行了全新设计,并首次采用了创新性PACE运行架构,能够将程序控制指令的执行和算力下放,提升处理效率,实现以最小的工程量创造出最高的测试单元产能。 PACE 取得这一成果,得益于分布式多控制器 (DMC) 计算架构,以及板卡硬件数据带宽的提高。多核系统控制器能够保持板卡高效、协调工作,从而提高系统产能。增加工位数提高生产效率,以及改进并行测试效率,使测试工程师能够更高效地对复杂芯片进行调试和特性分析,将新产品更快地推向市场。

UltraFLEXplus 上的“Broadside”应用接口简化了 DIB 布线设计,并改善工位间结果一致性。与传统的 ATE 相比,Broadside DIB 结构,将板卡较原先结构旋转了 90 度,因此板卡的资源,能够向芯片区域并行传送。这意味着每个工位,都能够获得与之匹配的信号传输路径,使得多工位之间也更易进行SiteCopy设计, 通过简化原本复杂的 DIB布局,实现更快的上市时间和更高的PCB良率。

J750/UltraFLEX/UltraFLEXplus都已经得到了市场的检验与客户的认可。值得一提的是,三款产品均使用统一的测试软件平台:IG-XL,在测试程序方面可做到相互兼容。同时意味着工程师开发的程序可以轻易在上述设备间实现无缝迁移,而这也是泰瑞达产品家族的核心竞争力之一。