1 后摩尔时代微电子科学研究面临的重大机遇与挑战

1.1 微电子科学研究的战略意义

自1958年第一块集成电路诞生以来,以集成电路为核心的微电子技术被认为是信息社会发展的驱动器。微电子产业已经超过诸多传统产业,发展成为全球经济增长的支柱产业,越来越多的国家开始重视其相关技术的发展。近年来,我国微电子技术发展迅速,涌现出以中芯国际、海思半导体、新潮科技等为代表的一批集成电路制造、设计与封测企业。然而,受限于技术、人才和资金等多方面的因素,我国微电子产业与美国等发达国家还有明显差距,从图1[1]给出的过去20年我国集成电路消费与生产对比曲线可以看出,集成电路的生产还远不能满足市场需求,仍旧要依赖于进口。

随着物联网、云计算、大数据、人工智能以及5G等新兴技术应用需求的快速增加,微电子产业在国民经济和国防建设中的战略地位日益凸显。2014年6月,国务院印发的«国家集成电路产业发展推进纲要»中指出:集成电路产业是信息技术产业的核心,是支撑经济社会发展和保障国家安全的战略性、基础性和先导性产业。2018、2019年中兴和华为相继被美国制裁的事件不仅暴露出美国对高新技术领域的防范,还充分说明了“关键核心技术是要不来、买不来、讨不来的。只有把关键核心技术掌握在自己手中,才能从根本上保障国家经济安全、国防安全和其他安全”[2],同时也暴露了我国的高科技产业,特别是微电子产业,与世界先进水平的差距。发展自主产权的高科技产品,加快微电子产业的自主知识产权布局迫在眉睫。国家自然科学基金“十三五”发展规划在“学科布局与优先领域”中将微纳集成电路和新型混合集成技术列为优先资助领域之一。

1.2 微电子科学发展面临的挑战与机遇

自集成电路发明以来,其工艺技术一直遵循着摩尔定律不断进步,如今最小线宽已达到几个纳米,进入了量子物理和介观物理的范畴,由此产生了诸如费米钉扎、库伦阻塞、量子隧穿、杂质涨落及自旋输运等物理现象[3]。延续了五十余年的摩尔定律遇到的这些物理障碍,使得基于硅的CMOS技术依靠单纯尺寸缩小来提升集成度面临着物理原理和工艺技术的巨大挑战。另一方面,随着晶体管密度的增加,单位面积内的功耗也越来越大,由此产生的巨大热量严重影响了集成电路的高频性能和可靠性。例如,从1997年到2010年,CMOS器件的栅长缩小了约300倍,但能耗密度增加了近10万倍,时钟频率只提高了2000倍左右[4]。功耗已然成为微电子产业发展的另一挑战。

当前,微电子发展正处于理论技术变革迅猛的重要时期,延续摩尔定律(More Moore)和超越摩尔定律(More than Moore)是其发展的两个重要方面。一方面,为了延续摩尔定律,解决纳米尺度器件面临的短沟道效应、高泄漏电流和60mV/dec的亚阈值摆幅限制等问题,以FinFET技术为标志的后摩尔时代新器件技术已经到来。CMOS器件从平面进入三维FinFET时代是解决功耗问题的必然选择,而FinFET从发明到实用历时14年,到2025年,传统CMOS微缩可能面临终结,新原理、新结构或新材料的器件必将登上历史舞台,在这种机遇期,基础研究显得尤为重要。另一方面,当集成电路工艺达到20nm和14nm时,每百万门的成本非但没有继续下降反而略有上升[5],单纯的缩小线宽失去了市场价值。超越摩尔定律则致力于在一个很小的空间内集成传感器件、射频器件、功率器件以及处理器等更多的功能来提高系统的集成度。单个芯片上的异质集成技术、系统级封装(SiP:System in Package)技术开始得到广泛关注,量子器件、自旋器件、神经形态器件等新型信息器件也逐步开始崭露头角。加强后摩尔时代微电子技术的基础研究,对未来微电子产业的发展及其产业格局意义深远。

2 微电子领域研究现状及重要成果

2.1 神经形态器件

2.1.1 人工突触器件的基本机理与发展现状

生物突触的特性表现在控制前后神经元连接的强度及突触强度的可塑性,受此启发,神经形态突触器件利用电子材料表现出的电阻特性模拟生物突触的连接强度,并且从外部电极端口对突触器件的电阻进行调制。按照突触器件所含有的端口数的不同,可以将突触器件分为两端器件、三端器件和多端器件等,其区别在于执行信号传递的路径和权重调制的路径不同。两端神经形态突触器件主要是忆阻器,根据机理不同可分为阻变存储器(RRAM)、相变存储器(PCM)、磁存储器(MRAM)等,这类器件的信号传递路径与权重调制路径为同一路径,均为上电极下电极。三端人工突触器件包含浮栅晶体管(Floating Ggate FET)、铁电晶体管(Fe FET)、电化学存储器(ECRAM)或突触晶体管等,此类器件的信号传递路径与权重调制路径是不同的,其中信号传递路径为漏极源极,而权重调制路径为栅极源极。2008年Nature报道了首个实验制备出的神经形态突触器件———忆阻器[6],2017年NatureMaterials报道了利用扩散性的神经形态器件实现了突触可塑性[7],2019年,Science报道了利用离子型浮栅存储器件进行神经形态计算等[8]。

对于人工神经网络应用来说,人工突触器件的电学特性是其应用表现的决定性因素。突触器件的重要电学特性包括模拟电导状态数、高低阻比值、电导调制的线性度和对称性、电导稳定性、电导调制的耐用性和器件良率。前四个电学特性影响着应用的性能,其中模拟电导状态数决定每次电导调制的步长,高低阻比值影响器件所能存储的信息量,电导调制的线性度和对称性决定着神经网络应用训练时的收敛能力。后三个电学特性决定应用的鲁棒性,其中电导稳定性和电导调制的耐用性决定器件能否长时间的进行推理和训练操作,器件良率影响神经网络应用的可行性。目前,人工突触器件的工艺及材料组成还处于不断变化发展中。

2.1.2 人工神经元器件的基本机理与发展现状

要构成完整的神经网络,除了人工突触器件之外,还需要可以模拟生物神经元功能的人工神经元器件。相比于突触神经形态器件的研究,神经元神经形态器件的研究进展相对有限,其中一个主要原因是生物神经元的多样化发放行为难以通过现有器件以低功耗、低硬件成本的方式精准模拟。2013年,惠普实验室的研究人员在Nature Materials杂志上报道了两个莫特忆阻器以及电阻、电容元件模拟HodgkinGHuxley(HH)神经元功能的方法,其中每个莫特忆阻器与一个电容并联,分别代表了HH神经元模型中的钠离子和钾离子通道,这种方法相比传统CMOS神经元电路更易于小型化[9]。IBM苏黎世研究中心于2016年展示了随机相变神经元电路,用相变材料的结晶化过程代替传统CMOS神经元的电荷积累过程模拟神经元的积累发放特性,同时相变物理过程能有效模拟生物神经元带来的固有随机性,有助于支持生物启发的群体编码等功能[10]。北京大学基于忆阻器和晶体管级联结构,用低硬件代价实现了视网膜神经元的积累发放功能,并搭建了基于此神经元的视网膜边缘检测网络,实现了图像处理功能[11]。

2.1.3 神经形态器件集成与应用

神经形态器件规模化集成是其实现大规模应用的关键,而规模化集成受器件的制备工艺与CMOS工艺的兼容性等因素制约。目前,大部分基于无机材料的神经形态器件均能与CMOS工艺兼容。从国际前沿研究来看,面向神经形态器件的芯片集成规模一直在上升,由1k发展至最近的4M。最近的国际电子学权威期刊NatureElectronics报道了64个突触器件和8个神经元器件组成全神经形态器件的神经网络,并完成了图案分类的演示[12]。清华大学2020年在Nature杂志上报道了基于多个忆阻器阵列的存算一体硬件系统,每个阵列集成了2k个突触器件,成功部署了多层卷积网络,结合混合训练的方法,在手写数字集上识别准确率高于96%,同时能效比TeslaV100GPU高出110倍[13]。由于神经形态器件支持三维集成,未来的器件密度将进一步提高,从而能够完成更复杂的应用。

2.2 BeyondCMOS器件

2.2.1 低功耗自旋电子学器件及芯片研究进展

相比传统CMOS器件而言,自旋电子学器件在尺寸微缩上不会受到物理效应的限制,存储密度不断提高。同时,自旋电子学器件具有极低的操作功耗,数据写入速度可小于1纳秒,非常有潜力替代SRAM和DRAM作为数据处理芯片的主存储器,解决逻辑运算单元与数据存储单元间的速度失配问题。在后摩尔时代,自旋电子学器件必将会扮演重要的角色。然而,自旋电子学存储器件同样面临一些技术难题:(1)数据写入时,电流密度会大幅度升高,会造成读写干扰及器件击穿等可靠性问题;(2)高阻态与低阻态间的比值不够高,局限在2.5以下,造成较高的读取错误率。

2.2.2 基于二维层状半导体的新型逻辑存储架构

新型二维层状半导体具有原子层级别的厚度,单层情况下其厚度可小于1nm。当采用二维层状半导体作为晶体管沟道时,可以大幅度削弱小尺寸下的短沟道效应,从而降低漏电流;同时,二维层状半导体具有完备的材料体系和丰富的能带结构,从而可以从能带设计出发开展新机理电子器件研究。并且二维层状半导体的表面不存在悬挂键,当二维层状半导体之间进行相互堆叠时,不会存在晶格失配的问题。2019年Nature评述论文指出:二维层状半导体材料非常有潜力使得摩尔定律进一步向前推进。

目前,基于二维层状半导体的新型逻辑存储架构已经取得了一定的突破性进展。通过能带设计,基于二维层状半导体异质结结构的半浮栅存储器在实现数据高速写入的同时,数据可保持长达10s的时间(准非易失数据存储)[14],引入局域场后,数据保持能力还可大幅提高535%[15]。同时,这一结构在采用纳米探针调控异质结极性后,光电探测响应率提高300倍[16]。利用单个二维层状半导体晶体管实现的逻辑门,相比CMOS工艺技术,有效减少了晶体管的使用数量,提升了面积使用效率。不仅如此,逻辑运算结果还可进行原位存储,不再需要通过数据总线进行传输,实现数据计算与存储的一体化集成[17]。将这一新结构用于SRAM集成中,成功实现了目前集成电路研究领域中最少构建单元的2T2RSRAM[18]。

然而,二维层状半导体的规模化应用还需要攻克许多难关,比如大面积二维层状半导体的高质量生长、可控性掺杂等。

2.2.3 极端条件下CMOS与半导体量子器件研究进展

当前各种新型应用场景对电子器件的要求日益苛刻:更低的功耗、更低的噪声、更快的响应速度以及更强的环境适应能力等。例如,对于太空探测应用环境而言,传统的CMOS器件温度工作区间为零下55℃至125℃,而太阳系各行星表面的最低温度可达零下229℃、最高温度可达175℃,器件必将面临严重失效的问题。同时太空中器件会受到高辐照效应影响,例如单粒子效应、电离总剂量效应以及位移损伤效应等,同样会造成器件失效。因此,需要充分利用新型材料以及新型结构在极端环境下的性能优势开发新型元器件,并搭建极端工作环境对器件的性能进行验证与改善。相比于从材料和结构上改进电子元器件在极端条件下的性能,充分利用量子效应等新型原理开发新型元器件同样也是当前的研究热点之一。继法国格勒诺布尔大学成功研制2位半导体量子处理器之后,谷歌公司又推出72位的超导量子处理器,展现了量子器件在数据处理上的巨大应用潜力。除了量子处理器以外,近年来,关于量子随机数发生器、量子参数放大器、量子传感器、单色光源、纠缠光源等量子功能器件的研究层出不穷,部分甚至已经商用化[19,21]。我国在量子器件应用上也取得了一定的成果,例如中国科技大学与本源量子合力研制的量子参数放大器,温度噪声低于400mK,接近标准量子噪声极限水平[22]。

2.3 面向全方位智能感知的传感器件

早期的微传感器主要基于在集成电路制造工艺基础上发展起来的平面加工技术,三维微加工技术的发展促进了多种新型微器件的诞生,纳米科学技术的进步及其与微加工技术的结合推动了微纳传感器的发展,传感技术与集成电路、无线通信、信息处理等技术交叉融合促进了无线传感器网络和物联网的兴起。人工智能技术的发展,有望进一步推动智能感知和智能控制技术的进步。智能传感器的发展呈现以下趋势:

(1) 从单一的物理感知发展到全方位感知。传感器从物理传感器发展到光传感,再到生化传感器,并与人工智能等信息技术深度融合,形成智能传感系统。

(2) 微纳传感器从中低精度向高精度发展。随着技术的进步,近年来惯性传感器等微纳传感器从中低精度向高精度、高附加值发展。例如,借助MicroGPNT计划,美国波音公司将MEMS陀螺精度推进到0.1°/h以内。超灵敏传感器可以实现单光子、电子电量、分子质量和声子测量,为基础物理研究、量子计算机和量子通讯等提供了有力的工具,并形成高端仪器设备。

(3) 微纳制造技术进一步发展。作为实现微器件与微系统的基础,微纳加工、封装技术不断发展。加工特征尺寸和精度从微米向纳米发展,逐步趋近于集成电路的加工尺度,结构上将从单层准三维结构向多层复杂三维结构发展。

(4)集成化芯片系统更加受到重视。进入21世纪以来,集成化芯片系统,即将敏感器件、微执行器、专用集成电路(ASIC)与微能源(micropower)等集成在同一芯片上,不仅可以大大降低系统的体积和功耗,还可以提高系统的性能与可靠性,已经成为微电子领域和传感器领域的热门方向,也是世界各国争相发展的重要战略方向之一。

2.4 功率与射频器件

2.4.1 功率半导体材料与器件

功率半导体芯片是超越摩尔定律的重要组成部分,制造功率半导体芯片的材料从传统的Si向以SiC、GaN为代表的宽禁带半导体材料发展,此外,近年来出现的超宽禁带半导体Ga2O3和金刚石拥有近5~10倍于GaN和SiC的Baliga指数,成为下一代理想的功率半导体器件材料。大尺寸Si基GaN是目前GaN基功率半导体器件以及Si与GaN器件异质集成的主要平台,主要得益于:

(1)晶圆尺寸的增大使单位面积材料的成本不断降低,目前Si基GaN外延能实现12英寸,基于蓝宝石(散热较差)和SiC衬底的晶圆主要为6英寸,且SiC成本较高;

(2)可兼容CMOS工艺,有效降低GaN功率电子器件的制造成本[23];

(3)利用Si基GaN平台有望实现GaN功率器件、射频器件和Si逻辑控制电路及驱动IC的单片集成[24,25]。

尽管美国康奈尔大学基于GaN的强极化效应实现了P型沟道的GaN外延结构[26],但二维空穴气(2DHG)的迁移率偏低,需要从能带调控和载流子散射机制方面探索制约2DHG输运特性的科学问题,为推动Si基GaN类CMOS器件乃至Si与GaN的异质集成奠定物理基础。另一方面,Si与GaN两种不同半导体器件的集成,不仅涉及两种材料的外延兼容性和界面控制问题,SiGCMOS和GaNGHEMT的工艺和器件结构的多维度兼容性也是实现多功能智能功率器件的瓶颈。

在超宽禁带材料和器件方面,我国与国际水平正处于并跑状态,其中,氧化镓电力电子器件亟需解决沟道外延材料质量差、界面态密度高、欧姆接触电阻大、器件的功率指数过低以及难以实现增强型器件等核心科学问题。由于金刚石的P型与N型较难掺杂等因素,需要开展金刚石超宽禁带半导体外延生长、掺杂技术及核心装备研究,金刚石缺陷和杂质的表征与抑制方法研究以及氢终端金刚石表面导电稳定性研究等。

2.4.2 微波毫米波、太赫兹器件

学术界和产业界对GaN材料和GaN基HEMT器件进行了多年的研究,但目前器件的特性仍不理想,尤其是功率指标方面。目前比较成熟的毫米波功率器件主要采用AlGaN势垒来解决击穿电压低的问题,但由于AlGaN势垒材料较厚,高频情况下短沟道效应引起的关态特性恶化导致其效率下降明显。为克服短沟道效应,国际上也同时发展了采用AlN、InAlN、InAlGaN势垒和N面GaN等异质结构,利用其超薄势垒或背势垒的优势制作高频、超高频器件,但由于AlN、InAlN势垒过薄以及N面GaN表界面态难以调控等条件的制约,器件工作电压和输出功率受到限制。此外,受材料生长质量的限制,器件关态漏电较大、工作效率减低,造成整体功率特性并不理想。

针对毫米波功率器件效率的瓶颈问题,我国学者在采用低损伤刻蚀工艺的基础上,采用自对准低温等离子体表面氧化技术,有效抑制了超薄势垒厚度引起的泄露电流增加现象及器件超短沟道所引起的短沟效应等问题。制备的栅长100nm的AlGaN/GaN毫米波器件,关态漏电低至10-9A/mm量级[27]。

2.5 DTCO与EDA技术

集成电路的发展一直与电子设计自动化(EDA:Electronic Design Automation)技术相伴而行,无论是集成电路的前端设计还是后端设计,都离不开EDA工具的支持。随着微电子工艺技术的持续进步和集成电路规模的不断扩大,EDA的重要性急剧增加,当前其面临的问题主要有:

(1)设计工艺协同优化方法(DTCO:Design Technology Co-GOptimization)。设计与工艺协同优化是当前先进微电子技术中一个关键且紧迫的课题。DTCO的提出与纳米尺度CMOS技术中出现的一个重要科学问题密切相关,即器件的随机涨落,称为统计涨落性或可变性(variability)。DTCO通过在先进工艺节点的研发初期,引入电路单元性能功耗面积成本(PPAC)和良率(yield)的新要求,协同制造设计GEDA三方信息,从而实现对产品的有效评估。目前DTCO方法流程和相关技术正处于不断探索中。

(2)敏捷设计方法。集成电路芯片从构想到成品不仅时间长而且资本投入大,为此,美国DARPA在电子复兴计划中提出了IDEA项目,研究通过机器学习等方法以及高层次描述提升集成电路设计效率和能力,最终实现非专业化电子系统自动设计。

(3)存算一体设计方法学。存算一体设计方法是克服存储计算分离的有效手段,可实现更高的吞吐率和能效,满足人工智能、物联网、超算等应用的数量级能效提升。在EDA工具方面,目前需要解决图计算等新计算范式的自动编译和近存计算自动编译等问题。

3 后摩尔时代微电子领域未来的主要研究方向和科学问题

针对目前我国集成电路芯片领域存在的瓶颈和未来发展趋势,与会专家学者坚持基础研究与产业需求相结合,以解决相关基础问题为目标,经过深入研讨和分析,凝练了后摩尔时代微电子发展的重大关键科学问题,提出未来5~10年微电子学科在以下几个方向的发展建议:

(1)神经形态计算方向:一方面注重神经形态器件与集成技术研究,揭示材料物性与器件神经形态特性的内在关联、神经形态器件多场输运机理与调控机制,探索神经形态器件大规模互联与类脑集成架构等。另一方面关注类脑芯片与智能系统研究,掌握器件非理想因素对智能系统的影响规律,优化材料器件电路架构协同设计方法,创新脑启发的新原理神经网络与算法等。

(2)Beyond CMOS器件方向:需要深入探究与硅融合的新材料多参数调控规律,面向能效提升的新器件机理;研制非易失自旋存算一体器件及芯片,基于二维半导体本征材料特性的新原理器件以及半导体量子芯片与量子计算系统等。

(3)智能传感器件方向:超高灵敏传感器的材料、原理和跨尺度集成,面向复杂传感量的多域、多场传感器的异质异构集成,多传感器、微能源、电路三维异质异构巨集成设计与制造,复杂多传感信号的智能处理,针对多样化应用的生物学、信息科学、机械学交叉融合以及面向物联网和健康医疗应用的多传感器集成微系统都是有待深入研究的问题。

(4)功率与射频器件方向:一方面需要深入开展基于新材料、新结构和新原理的功率半导体器件和集成研究,包括超结功率MOS器件的三维电荷平衡机理,宽禁带和超宽禁带半导体器件的表界面态钝化与界面态起源,载流子输运以及抗辐照特性以及兼容CMOS的宽禁带半导体智能功率芯片与异质集成等。另一方面需要继续开展面向下一代移动通信的射频器件和芯片研究,包括高效微波毫米波太赫兹器件与集成电路,GaN微波毫米波大功率器件在高压大动态、高温、重离子辐照条件下的可靠性失效机理以及多物理场条件下的电磁兼容等。

(5)EDA和DTCO方向,需要从EDA中的机器学习方法、面向新架构新电路的设计方法学、基于新器件的电路和系统架构自动设计以及新器件模型和设计与工艺协同优化方法等多方面开展研究。

4 总结与展望

器件的基础创新是微电子产业发展的基石,随着摩尔定律推进并达到物理极限,基于新原理、新材料和新结构的半导体器件引发集成电路工艺变革,后摩尔时代已然到来。本次论坛研讨了超越摩尔定律的核心研究内容和重要的前沿进展,展望了超越摩尔定律的低功耗、多样化、智能化器件及其与材料、架构的协同设计研究对后摩尔时代微电子路径的突破性和颠覆性前景,初步凝练了超越摩尔定律发展路径上的基础科学问题和关键挑战,从交叉、融合、协同等角度提出了前沿性和战略性的重点发展方向,对促进我国微电子前沿研究再上新高度起到积极推动作用。

文章信息与来源:

《后摩尔时代的微电子研究前沿与发展趋势》

孙 玲1†∗∗ 黎 明2† 吴华强3 周 鹏4 黄 森5 张丽佳1 潘 庆1 李建军1 张兆田1

1 . 国家自然科学基金委员会 信息科学部, 北京 100085

2. 北京大学, 北京 100871

3. 清华大学, 北京 100084

4. 复旦大学, 上海 200433

5 . 中国科学院 微电子研究所, 北京 100029

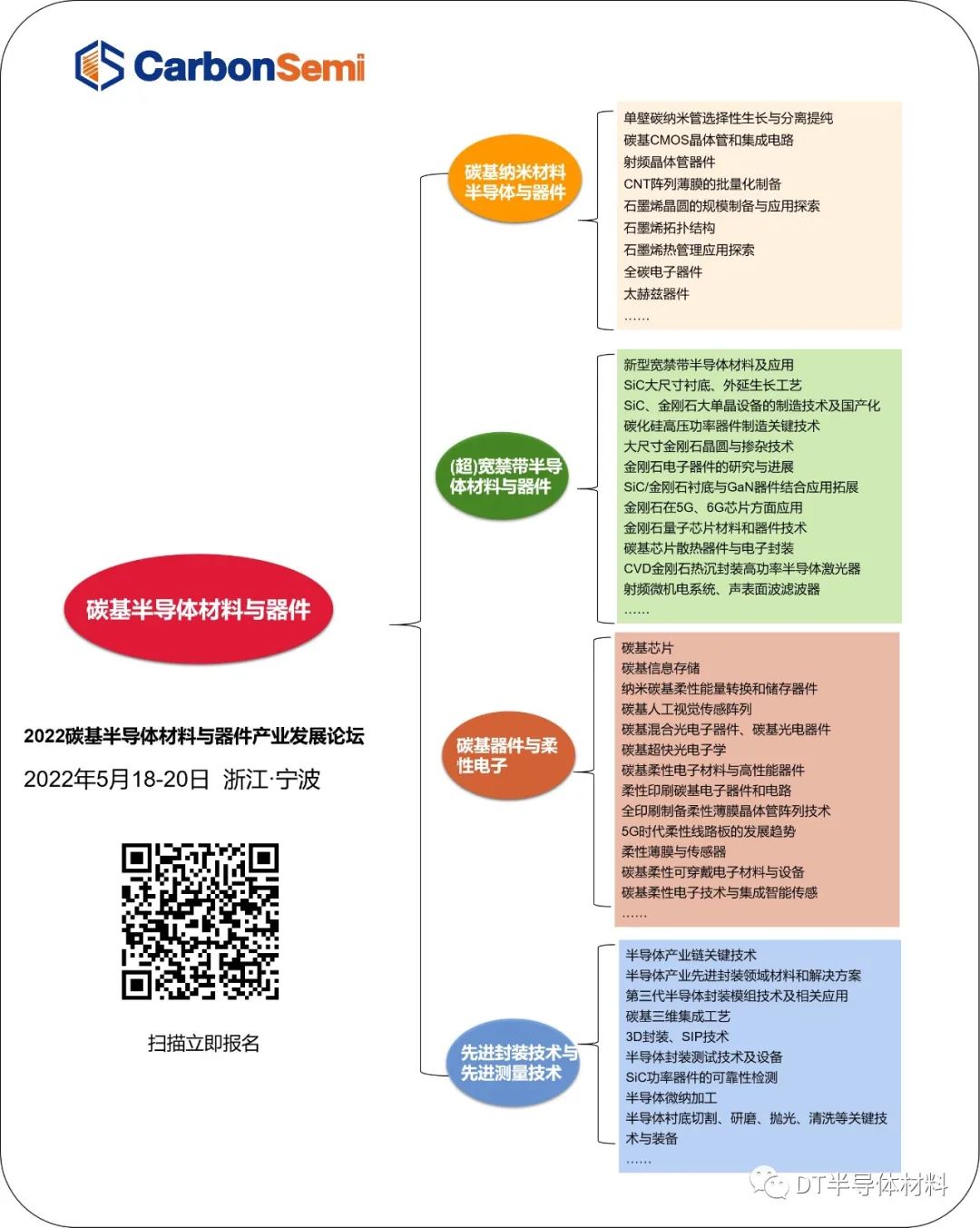

2022碳基半导体材料与器件

产业发展论坛

演讲及征文联系

Mable

手机号码:18989362825

邮箱:liushuang@polydt.com

高校、企业注册及赞助合作

Luna

手机号码: +86 13373875075

邮箱: luna@polydt.com

Bella

手机号码:+86 13336674895

邮箱: chanel@polydt.com