来源 | 秦岭农民

智库 | 云脑智库(CloudBrain-TT)

云圈 | 进“云脑智库微信群”,请加微信:15881101905,备注您的研究方向

声明 | 本号聚焦相关知识分享,内容观点不代表本号立场,可追溯内容均注明来源,若存在版权等问题,请联系(15881101905,微信同号)删除,谢谢。

1 3D堆叠技术

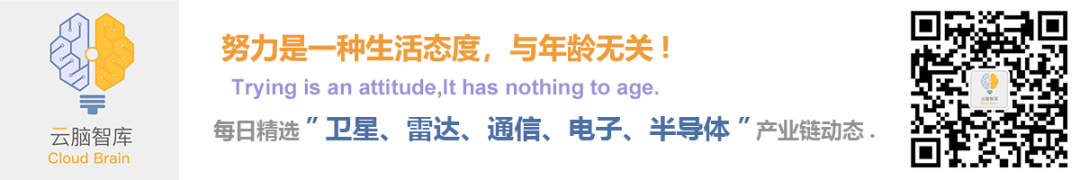

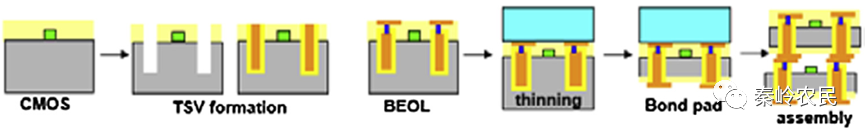

芯片3D堆叠技术涉及如图1描述的几个关键工艺:晶圆减薄,TSV通孔,Wafer handling,Wafer bonding和Wafer test。

图1 3D堆叠技术关键工艺

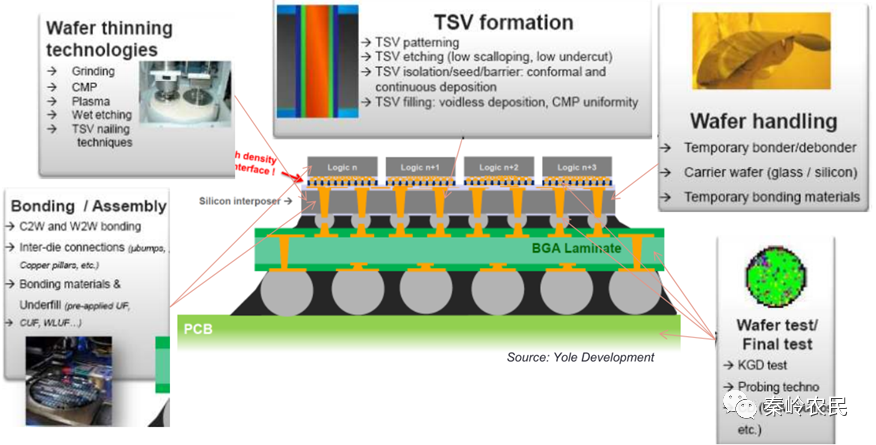

图2 为几种叠层封装形式对比

图2 a)叠层绑线封装 b)TSV封装 c)POP package on package 叠层d) PiP Package in package 叠层

2 3D堆叠技术优缺点

2.1 3D堆叠技术存在的优点

基于 TSV 的三维高密度集成/封装技术具有以下四个主要优点:

(1)高密度集成:通过三维封装,可以大幅度地提高电子元器件集成度,减小封装的几何尺寸,和封装重量。克服现有的 2D-SIP (System In a Package二维系统级封装)和POP (package on package三维封装堆叠)系统的不足,满足微电子产品对于多功能和小型化的要求。

(2)提高电性能:由于TSV技术可以大幅度地缩短电互连的长度,从而可以很好地解决出现在 SOC(二维系统级芯片)技术中的信号延迟等问题,提高电性能。现电子元器件的多功能。同时也降低了芯片的整体功耗。

(3)多种功能集成:传统的二维SOC技术必须通过复杂的设计以及很大的芯片尺寸来实现有限的集中功能芯片集成,很难实现多功能芯片的集成。通过 TSV 互连的方式,可以把不同的功能芯片(如射频、内存、逻辑、数字和 MEMS 等)集成在一起实现电子元器件的多功能。

(4)降低制造成本:TSV 三维集成技术虽然目前在工艺上的成本较高,但是可以在元器件的总体水平上降低制造成本。

2.2 3D堆叠技术存在的缺点

(1)设计更复杂,因为绑线布局有更多选择。

(2)TSV 和晶圆减薄的成本增加。

(3)在晶圆成品率不高情况下增加芯片的组装和测试成本。

(4)3D 堆栈中芯片的功率传输、分配和冷却更加困难。

3 TSV技术

硅通孔技术(TSV,Through -Silicon-Via)是通过在芯片和芯片之间、晶圆和晶圆之间制作垂直导通,实现芯片之间互连的最新技术。

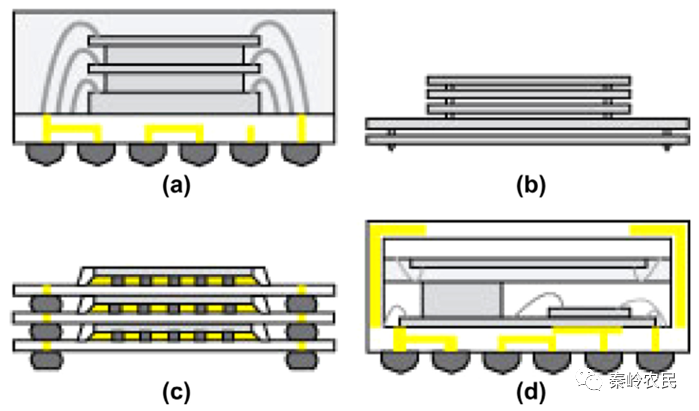

与以往的IC封装键合和使用凸点的叠加技术不同,如图3 TSV封装与叠层封装对比图。

图3 Comparisonof package height for wide I/O DRAM with (a) TSV connectionsand (b) wirebondconnections

TSV能够使芯片在三维方向堆叠的密度最大,外形尺寸最小,并且大大改善芯片速度和低功耗的性能。

TSV 技术通过铜、钨和多晶硅等导电物质的填充,实现硅通孔的垂直电气互连。硅通孔技术带来的好处主要有:通过垂直互连减小互连长度,减小信号延迟,降低电容、电感,实现芯片间的低功耗、高速通讯,增加带宽和实现器件集成的小型化。

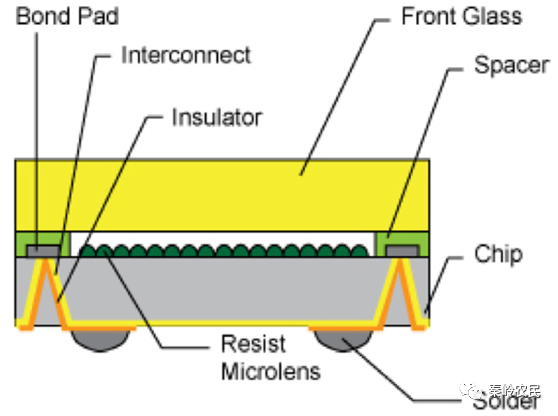

图4 Image sensor formed using wafer level package andTSVs

4 TSV技术工艺

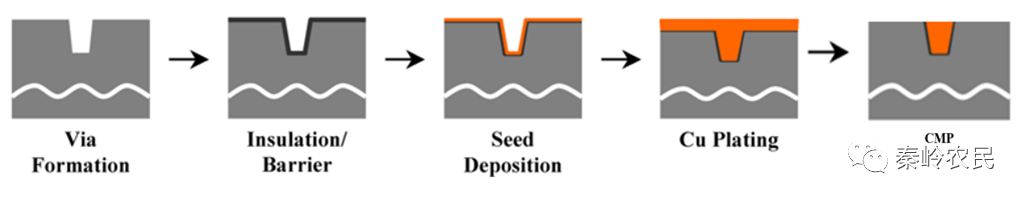

TSV 制作工艺主要有以下几个步骤

1)激光钻孔或者离子深刻蚀(DRIE)形成通孔。

2)通过热氧化或等离子体增强化学气相沉积 (PECVD) 沉积中间介电层。

3)通过物理气相沉积 (PVD) 沉积阻挡层和种子层。

4)通过电镀或者PVD工艺将TSV孔用铜或者钨孔进行填充。

5)镀铜层(覆盖层)的化学和机械抛光 (CMP)

图5 TSV工艺过程

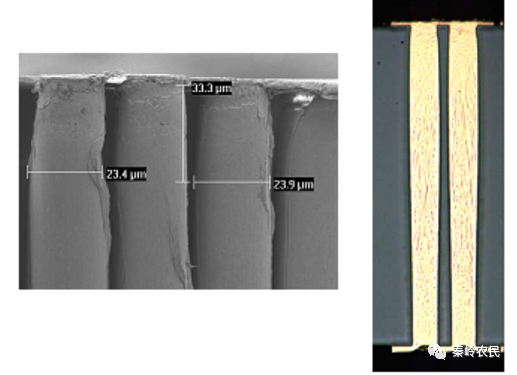

图6 是扫面电镜(SEM)和金相显微镜拍摄的Cu TSV工艺图

图6扫描电镜和金相显微镜下的Cu TSV通孔

TSV 可以采用先通孔(via-first)、中通孔(via-middle)、后通孔(via-last)及从晶圆背后的后通孔技术(backside via-last)制备。

4.1 先通孔(via-first)

先通孔工艺(见图6)是指在器件(如 MOSFET 器件)结构制造之前,先进行通孔结构制造的一种通孔工艺方法。晶圆上先进行 TSV 结构的通孔刻蚀,孔内沉积高温电介质(热氧沉积或化学气相沉积),然后填充掺杂的多晶硅。多余的多晶硅通过 CMP 去除。这种方法允许使用高温工艺来制造绝缘化的通孔(即高温SiO2 钝化层)并填充通孔(即掺杂的多晶硅)。由于多晶硅通孔的高电阻率,先通孔工艺并未广泛用于有源器件晶圆。使用先通孔工艺的图像传感器产品和MEMS 产品数量有限,对于这些应用,通孔尺寸较大(大于 100μm),因此掺杂多晶硅通孔的电阻是可以接受的。

图6 先通孔工艺

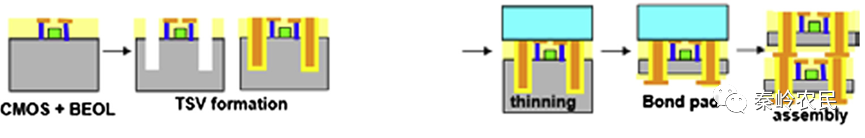

4.2 中通孔(via-middle)

中通孔工艺(见图7)是在工艺流程的制造过程中形成的TSV 结构。常常在形成器件之后,在制造叠层之前制造的通孔工艺。在有源器件制程之后形成TSV 结构,然后内部沉积电介质。电介质沉积对于中通孔工艺具有挑战性,因为必须使用相对低温的电介质沉积方法(小于 600 ℃),以避免损伤器件性能(但对于无源Si 转接板,可以使用高温电介质来做绝缘钝化层,因为晶圆上没有有源器件)。淀积阻挡层钛金属和铜种子层,然后电镀铜填充通孔,或者可以通过化学气相沉积钨金属填充通孔。通常,钨用于填充高深宽比 TSV(深宽比大于 10∶1),而铜用于填充低深宽比TSV(深宽比小于 10∶1)。中通孔工艺适用于 100 μm及以下的 TSV 间距。中通孔工艺的优点是TSV 结构间距小,再布线层通道阻塞最小以及TSV 结构电阻较小。其主要缺点在于它必须适合产品器件性能要求这样才不会干扰器件(如低热应力影响),并且也不会干扰相邻的布线层(即将 TSV 结构的凹陷减小到最小,使应力影响最小化)。此外,TSV结构中通孔工艺成本相对较高,尤其是 TSV 结构的刻蚀工序、铜电镀工序以及铜面的化学机械抛光工序。

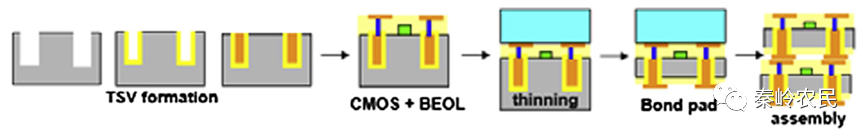

图7 中通孔工艺

4.3 后通孔(via-last)

正面后通孔工艺(见图 8)是在 Back End of Line(BEOL)工艺处理结束后,从晶圆正面形成通孔的一种制造工艺。从概念上讲,在晶圆上制造的后通孔工艺与中通孔工艺相似,但是对工艺温度有进一步的限制(必须小于 400 ℃)。正面后通孔工艺的一个优点是TSV 结构的粗略特征尺寸可与全局布线层的特征尺寸相媲美,因此简化了工艺集成的某些制造流程。对于通过晶圆与晶圆间键合形成的 3D 堆叠,正面后通孔工艺也具有一些优势。TSV 结构可以在工艺结束时形成,连接堆叠中的多层封装。正面后通孔工艺的一个缺点是 TSV 结构的刻蚀更具挑战性,因为除了 Si 刻蚀之外,还必须刻蚀整个电介质叠层。该工艺的另一个问题是它会阻塞布线通道,从而导致更大的芯片尺寸。由于这些限制,正面后通孔工艺的应用受到了限制。

图8 后通孔工艺

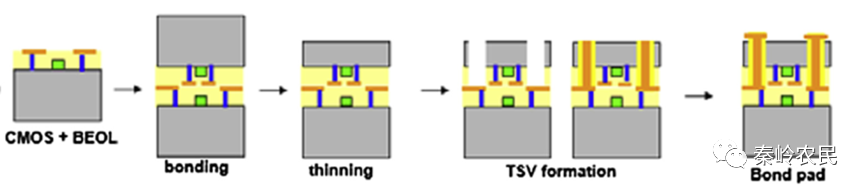

4.4 背后通孔(backside via-last)

背面后通孔工艺是在 BEOL 工艺处理结束后,从晶圆背面进行通孔结构的一种制造工艺。对于晶圆到晶圆间的堆叠,可以简化工艺流程,因为省去了许多背面工艺步骤,例如背面焊料凸点和金属化。可以使用氧化物或聚合物粘合剂从正面到背面或从背面到背面键合晶圆。图 9 显示了背面后通孔工艺的示例。首先使用粘合剂将两个器件晶圆以面对面方式粘合,接下来,将顶部晶圆减薄,将 TSV 结构刻蚀至顶部晶圆和底部晶圆上的焊盘,孔内沉积电介质,最后,将金属沉积到 TSV 结构中并进行表面金属层再布线。背面后通孔工艺被广泛用于图像传感器和 MEMS 器件。对于这些应用,TSV 结构尺寸较大,因此通孔可以逐渐变细,从而简化了电介质和金属的后续沉积。由于通孔直径大(大于 100 μm),因此可以实现足够的电介质保形性。通过掩模步骤或使用间隔物刻蚀形成 TSV 结构的底部介电层,TSV 结构内部沉积金属,通过电镀再分布层进行表面图案化。一般不需要完全填充 TSV结构的金属,因此可以缩短处理时间或简化处理步骤。

图9 背面后通孔工艺

- The End -

版权声明:欢迎转发本号原创内容,转载和摘编需经本号授权并标注原作者和信息来源为云脑智库。本公众号目前所载内容为本公众号原创、网络转载或根据非密公开性信息资料编辑整理,相关内容仅供参考及学习交流使用。由于部分文字、图片等来源于互联网,无法核实真实出处,如涉及相关争议,请跟我们联系删除。我们致力于保护作者知识产权或作品版权,本公众号所载内容的知识产权或作品版权归原作者所有。本公众号拥有对此声明的最终解释权。

投稿/招聘/推广/合作/入群/赞助 请加微信:15881101905,备注关键词

“阅读是一种习惯,分享是一种美德,我们是一群专业、有态度的知识传播者.”

↓↓↓ 戳“阅读原文”,加入“知识星球”,发现更多精彩内容.

分享💬 点赞👍 在看❤️@以“三连”行动支持优质内容!