来源 | 数字ICer

智库 | 云脑智库(CloudBrain-TT)

云圈 | 进“云脑智库微信群”,请加微信:15881101905,备注您的研究方向

声明 | 本号聚焦相关知识分享,内容观点不代表本号立场,可追溯内容均注明来源,若存在版权等问题,请联系(15881101905,微信同号)删除,谢谢。

在 multi-voltage design 中,常常用到level shifter;

本文简单介绍:

什么是 level shifter?

何时需要用到level shifter?

level shifter的插入位置?

在multi-voltage design中,将信号从一个power domain到另一个power domain需要一个Level Shifters(电压/电平转换器)。level shifter用作缓冲器,输入端有和输出端的电压域不同,若不进行电压转换,可能无法正常工作;

这种cell在我们使用的IO中也广泛存在,用于将外部的电压与core电压之间进行转换。

此外,如果设计中还采用了Power Gating技术,在不同电压域之间进行通信的情况下,除了需要添加Level Shifter之外还需要用到另外一种cell :低功耗设计 | isolation cell

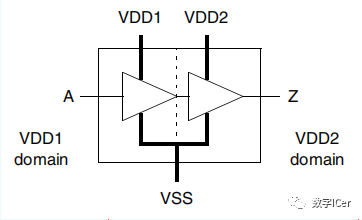

从高电压到低电压的level shifter,可以是两个反相器的串联:

根据电平转换的方向,Level Shifter可以分为三种:

需要在两个Power domain之间插入level shifter的情况有三种:

情况1和情况2如果不插入level shifter,可能造成功能错误或者芯片不稳定;

情况3虽然VDD_PD1传入VDD_PD2可能能够正确识别逻辑功能,但是由于VDD_PD1和VDD_PD2不是完全相同,为了保证时序,还是需要插入level shifter;

如果是高电平域的信号输出到低电平域,由于低电平域器件的阈值电压低,直接接高电平信号有可能会造成误抖动;

如果是低电平域信号输出到高电平域,由于高电平域器件的阈值电压高,所以高电平域器件很难区分低电平域信号的0/1,如果直接连接会有驱动不足等问题;

建议:

不管是从高到低转换还是从低到高转换,都要加上level shifter。Level shifter通常不具备逻辑功能,只是用于不同电压值之间的信号电平的转换,也就是Level shifter并不会影响逻辑设计,它只是一个电压转换的buffer;所以level shifter不会对功能仿真造成影响,不需要去写验证激励来测试;

上面这个列子是一个buffer类型的Level shifter, 逻辑上相当于一个buffer,只是输入输出的电压不一样。

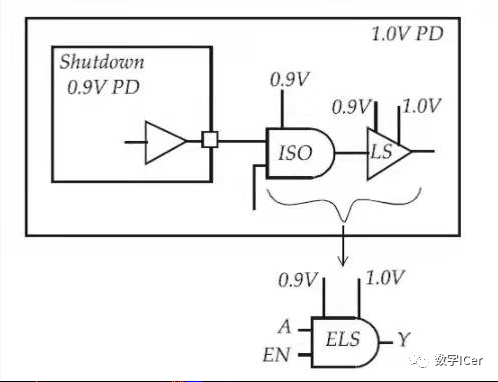

上面这个例子是带ISO的level shifter,将两个cell合成一个,叫做enable level shifter (ELS);

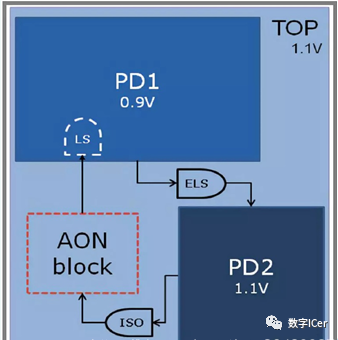

比如当下图中信号从AON block传输到PD1时,需要加Level shifter。

当信号从PD1传输到PD2时,由于PD1是power gating模块,所以需要在PD1和PD2之间加带Isolation 功能的Level shifter cell(ELS:Enable Level shifter)。

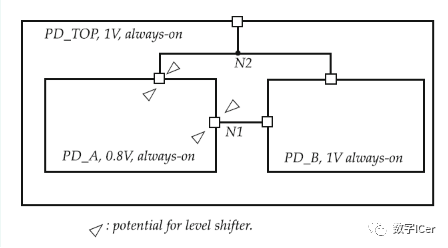

又例如:

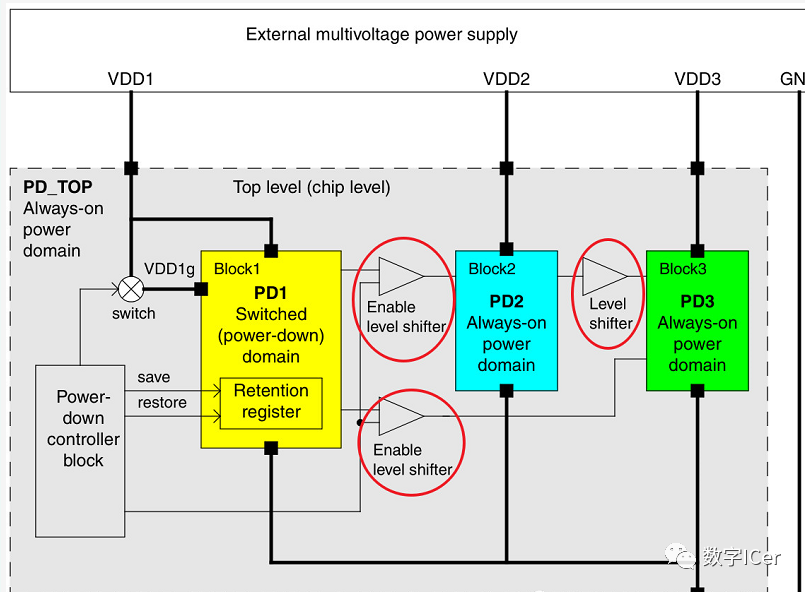

下图,PD1是可被关断的,PD1与PD2、PD1 与PD3之间用的Level Shifter就是带有Isolation功能的Level Shifter。而PD2是Always On的,所以PD2与PD3的数据只需要用普通的Level Shifter即可。

Level Shifter可以加在信号的源(source)端,也可以加在信号的目的(destination)端。一般推荐加在目的端,因为不需要连secondary pg pin,更加节省资源。

也就是说:

但是这个规则并不绝对,具体要结合实际情况,比如要考虑功耗,时序等。

cell(Buffer_Type_LH_Level_shifter) {

is_level_shifter : true;

level_shifter_type : LH ;

pg_pin(VDD1) {

voltage_name : VDD1;

pg_type : primary_power;

std_cell_main_rail : true;

}

pg_pin(VDD2) {

voltage_name : VDD2;

pg_type : primary_power;

}

pg_pin(VSS) {

voltage_name : VSS;

pg_type : primary_ground;

}

...

pin(A) {

direction : input;

related_power_pin : VDD1;

related_ground_pin : VSS;

input_voltage_range ( 0.7 , 0.9);

}

direction : output;

related_power_pin : VDD2;

related_ground_pin : VSS;

function : "A";

power_down_function : "!VDD1 + !VDD2 + VSS";

output_voltage_range (1.1 , 1.3);

...

...

}

- The End -

版权声明:欢迎转发本号原创内容,转载和摘编需经本号授权并标注原作者和信息来源为云脑智库。本公众号目前所载内容为本公众号原创、网络转载或根据非密公开性信息资料编辑整理,相关内容仅供参考及学习交流使用。由于部分文字、图片等来源于互联网,无法核实真实出处,如涉及相关争议,请跟我们联系删除。我们致力于保护作者知识产权或作品版权,本公众号所载内容的知识产权或作品版权归原作者所有。本公众号拥有对此声明的最终解释权。

投稿/招聘/推广/合作/入群/赞助 请加微信:15881101905,备注关键词

“阅读是一种习惯,分享是一种美德,我们是一群专业、有态度的知识传播者.”

↓↓↓ 戳“阅读原文”,加入“知识星球”,发现更多精彩内容.

分享💬 点赞👍 在看❤️@以“三连”行动支持优质内容!