新手如何学习数字芯片设计验证

初学数字芯片设计验证切忌一口吃个胖子,上来就是武林高手,瞬间能写设计代码,甚至是复杂的代码。我也不建议上来就要认真的去学习数字逻辑电路基础,甚至要去学习C语言之类的,要说起基础课程,半导体物理,数字集成电路甚至模拟集成电路,还有半导体器件,半导体工艺这些都是基础,都要学的话,你能学得完吗?要这么学,那你基本学不会,所以,来看看正确的学习思路吧!

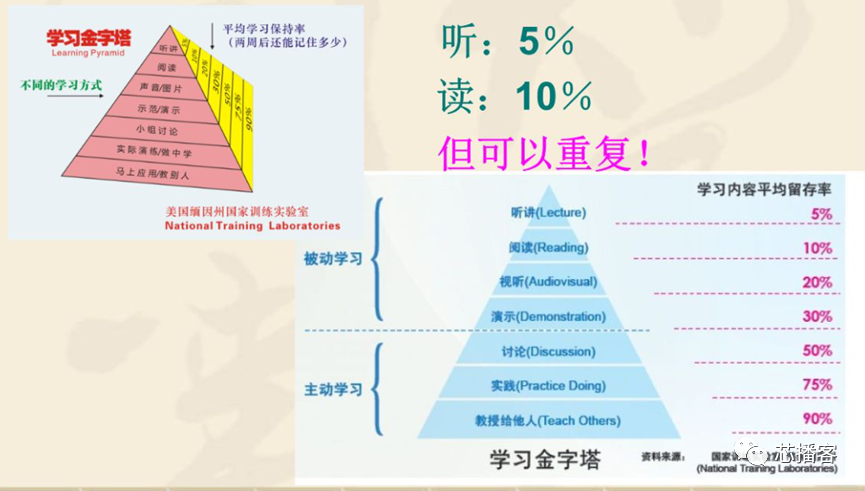

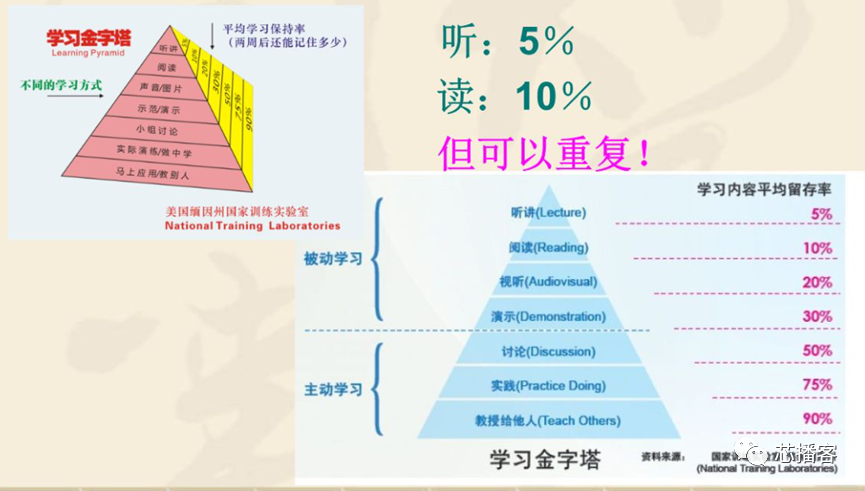

其实学习数字芯片设计验证的技能,我认为可以简单分为三个阶段:输入阶段、加工阶段、输出阶段。输入阶段,照猫画虎是不可能的,我们用“照虎画猫”可能更加合适一点!按图索骥就非常好,首先了解好你要学的技能是干啥的,比如你要学数字芯片设计,你首先要知道数字芯片是啥,数字芯片设计的流程是啥,每个阶段大家都在干啥?要学习Verilog HDL,很简单,先一行行照着例子或者书上的example敲出来,然后照着视频或者userguider去编译通过,再run起来,照着能把波形dump起来,然后能正常拉出波形,当你学会改一改其中的assign语句的逻辑运算,或者是always语句的if条件,case语句的时候,那么这个时候再去纠结这些运算符是个啥意思,这时候可以考虑去查询数字逻辑的书了,如果还想再往下一点,再去查询CMOS管组成的反相器,以及与非门、或非门是什么样子。通过输入阶段初步理解了很多比较晦涩难懂的底层基础知识,再考虑从module到endmodule独立写出来一个小模块,这样你对数字芯片设计的模块的概念会越越来越熟悉,当然,testbench不能少,学着在Verilog HDL的testbench里面把激励能给进去,编译起来,run起来起来,dump波形,甚至debug起来。这个阶段旨在把我们书本的、理论的知识变成自己能记住的知识,能运用的知识,当然,语法点很多,没有必要全部记住,但是,一定要知道这些知识点在哪儿,用的时候要去查。当然了,经常用的assign和always之类的一定要记住的,关键的一些关键词要记住的。这就是加工阶段。这个阶段可能会持续很久,你才可能会有点思路。但是,没关系,这时候,就选择一些常见的笔试面试题,看看自己有没有思路,先自己想一下,如果实在想不出来,没有思路,就先看懂别人的思路,然后不要照着抄了,开始自己按照想着那个思路去理解。比如状态机,看看是怎么按照这个状态转移图就写出三段式的代码了,三段式的结构是什么?先有一个思维定式。然后慢慢地去优化这个定式。慢慢地,去找Verilog HDL编程和实际的硬件电路对应的感觉,俗称硬件思维。输出阶段就是应用阶段,掌握的知识如果无法应用到实际中去,那就说明还没有彻底掌握。所以这个时候你需要理解数字芯片PPA的概念了,可以把你写的代码以及你对整个数字芯片的理解跟实际的数字芯片的PPA去对应了,不是简单的写代码,因为Verilog HDL很简单,比C语言还简单,一本Verilog HDL的书,你写出花儿来,也就三四百页足足的够了,要是光写语法知识,估计几十页足以,那咱们就输出一些学习成果,比如写个学习比较,Verilog HDL学习笔记,把你掌握的笔记写出来。通过输出应用阶段,这些基础知识会印刻在我们的大脑里,成为本能。当然,输出,除了写出来,还有一个特别难得的机会,就是讲出来,如果有机会分享自己的学习成果或者学习过程,这是一个非常好的过程,一定要积极应对,你准备材料的过程,你讲的过程,以及面对面人的质疑,反思的过程,都是升华。说完学习的三个阶段,再来看看学习金字塔吧,都是成年人了,不用我说,大家都能理解是啥意思吧? 人生有三个最大错觉:她喜欢我、手机震动、我能反杀,对于0基础学数字芯片设计的同学们来说,还要加一个:这题我会!。但事实是,面对很多简单的example,很多人面临的结果是:一看就会,一练就废!所以,一定要自己练习,虚拟机安装好相应的开发环境,搞起来!这就跟我们小时候背课文最后必须默写下一个道理,纸上得来终觉浅,需知此事要躬行。自己写出来的感觉就完全不一样了,它代表了真正的理解和深度的认知。脑补和代码真实跑起来完全是两码事,细节是魔鬼,那些微小的细节恰恰是你以为理解其实没理解的东西。不动手练习的同学,对编辑器比如gvim或者VIM,对Linux操作系统,以及仿真验证工具VCS等等等,都会充满恐惧,大多数情况,刚开始上手都是Error频出,标点符号写错的,编译option写错的,0和O傻傻分不清的,太多低级的Error了,很多新手,遇见编译不过就慌神了,到处问,完全没有自己解决问题的能力,其实Error提示的信息大多数情况下很明确的。动手写代码还可以帮你积累自己的module库,这就跟滚雪球一样,越早启动最后滚的越大。也就是说你把常见的module都写几遍,比如FIFO,分频,倍频等等这些电路,如果都有接触,那么后面再设计整个大一点的模块,就一点都不怕了!动手编写Verilog HDL代码,最终你的Verilog HDL得跑起来吧,得看看有没有实现你的功能吧?跑起来就一定会有各种稀奇古怪的Error,编译的Error,解决完编译的Error,然后debug功能对不对,追信号,追驱动,熟悉软件的操作,又是一段修行!debug的过程真的是精华,是数字芯片设计工程师成长的利器。

人生有三个最大错觉:她喜欢我、手机震动、我能反杀,对于0基础学数字芯片设计的同学们来说,还要加一个:这题我会!。但事实是,面对很多简单的example,很多人面临的结果是:一看就会,一练就废!所以,一定要自己练习,虚拟机安装好相应的开发环境,搞起来!这就跟我们小时候背课文最后必须默写下一个道理,纸上得来终觉浅,需知此事要躬行。自己写出来的感觉就完全不一样了,它代表了真正的理解和深度的认知。脑补和代码真实跑起来完全是两码事,细节是魔鬼,那些微小的细节恰恰是你以为理解其实没理解的东西。不动手练习的同学,对编辑器比如gvim或者VIM,对Linux操作系统,以及仿真验证工具VCS等等等,都会充满恐惧,大多数情况,刚开始上手都是Error频出,标点符号写错的,编译option写错的,0和O傻傻分不清的,太多低级的Error了,很多新手,遇见编译不过就慌神了,到处问,完全没有自己解决问题的能力,其实Error提示的信息大多数情况下很明确的。动手写代码还可以帮你积累自己的module库,这就跟滚雪球一样,越早启动最后滚的越大。也就是说你把常见的module都写几遍,比如FIFO,分频,倍频等等这些电路,如果都有接触,那么后面再设计整个大一点的模块,就一点都不怕了!动手编写Verilog HDL代码,最终你的Verilog HDL得跑起来吧,得看看有没有实现你的功能吧?跑起来就一定会有各种稀奇古怪的Error,编译的Error,解决完编译的Error,然后debug功能对不对,追信号,追驱动,熟悉软件的操作,又是一段修行!debug的过程真的是精华,是数字芯片设计工程师成长的利器。

本文由EETOP 创芯大讲堂首荐IC职业&就业培训课程:《零基础学习数字芯片验证入门到实战》特约讲师于兆杰博士撰写。课程共99课时,目前已更新至39课时。《零基础学习数字芯片验证入门到实战》可推荐就业 赢高薪职位!" linktype="text" imgurl="" imgdata="null" data-itemshowtype="0" tab="innerlink" data-linktype="2">点击查看->《零基础学习数字芯片验证入门到实战》可推荐就业 赢高薪职位!