在产品定型前的电磁兼容测试不合格的问题,我们完全可以遵循正常的电磁兼容设计思路,按照电磁兼容设计规范法和系统法,针对产品存在的电磁兼容问题重新进行设计。从源头上解决存在的电磁兼容隐患。这属于电磁兼容设计范畴。 在电磁兼容设计中电容的使用看似简单其实是很有讲究的,电容使用得好的话能解决很大一部分电磁兼容问题。

一、芯片电源滤波设计

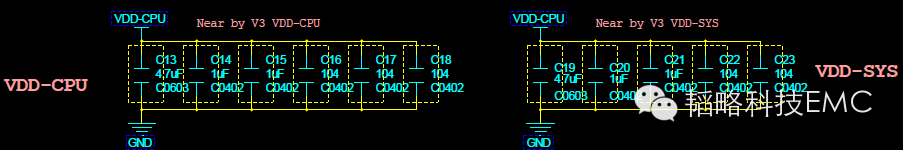

高速电路芯片每个电源引脚用使用不同容值电容下地进行滤波

某产品CPU电源滤波系统

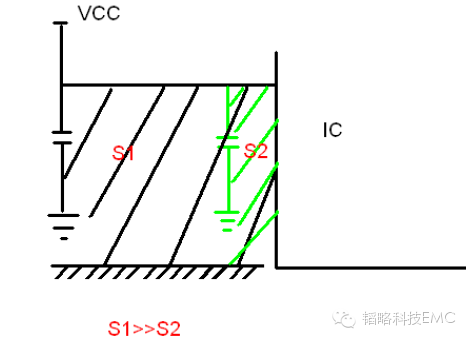

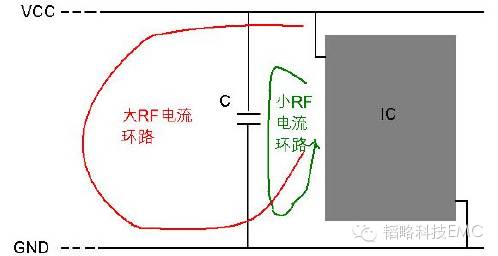

电容放置的位置是有讲究的,原则是经量靠近IC端,下图中S2的环路面积要远远小于S1中的环路面积。去耦电容越靠近IC电源处所形成的RF电流回路就越小,从而大大减小来自电源和地噪声的电磁干扰。还有重要的一点是,要经量减小所使用去耦电容的引脚或引线的长度,同时当电容安装到PCB上时,使连接此去耦电容的PCB走线越短越好,这样的去耦效果才会比较好。

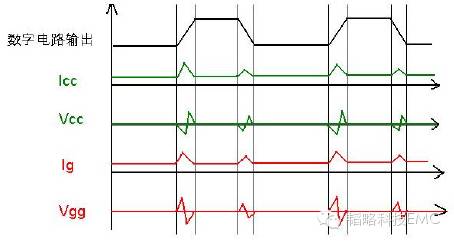

下面来探讨一下为什么要使用去耦电容,从下图可看出,当数字信号有上升沿和下降沿产生是,电源和地在对应的时间上也产生了不同程度的噪声,这些噪声将会使电路系统辐射超标。

电源线上和地线上的噪声

首先从抗干扰角度上来说,去耦电容能够提供一个局部的没有电感的或者很小电感的电源。通过去耦电容,把电压保持在一个恒定的参考点,阻止错误的逻辑转换。

再从产品产生电磁干扰来说,去耦电容能够给高速数字电路中的高低电平转换而产生的开关电流提供一个比较小的回路面积,从而减小辐射面积以降低电磁干扰,同时去耦电容对数字电路供电来说,也能够提供一个局部的能量存储源,也可以减少电源系统的辐射环路面积,从而进一步减小来自电源系统的电磁干扰产生。

EMC概念中的电容等效电路

电容引脚及其在电路中的引线长度在高频是不可忽略,而应该等效于该电容的寄生电感(ESL),同时引脚及其在电路中的引线电阻构成了该电容的寄生电阻(ESR).所以告诉电路中的电容实际上构成了一个串联自谐振电路。

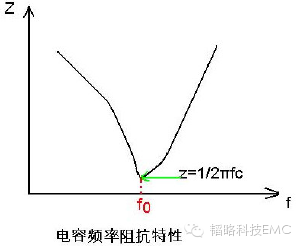

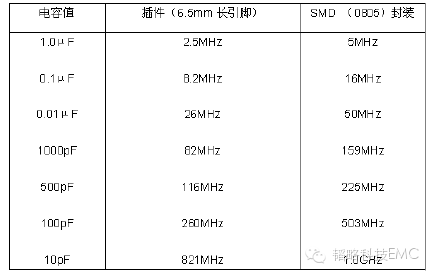

下图为电容的自谐振频率

电容自谐振频率

选择电容时,并非取决于电容值的大小,而是电容的自谐振频率,且以之使需去耦的频率相匹配。

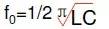

电容的自谐振频率

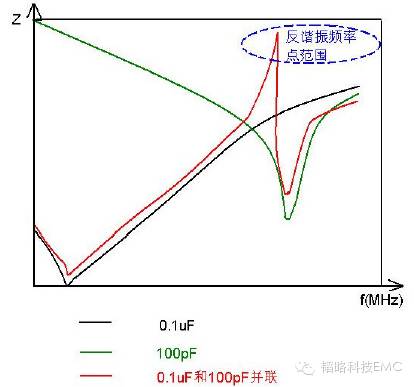

多电容的并联在实际应用中,两个或多个电容并联使能够提供更宽的频率回流带宽,此时,两个电容或者多个电容值必须要有不同的容值,一般来说数量级相差100倍以上。(容值相差大是为了让反谐振频率点范围变得更窄,以达到最佳的使用效果)。

另外,两个同值的电容并联,也可以提高去耦的效果,这时电容寄生电感和寄生电阻因为并联后而减小,但谐振频率不变,只是在谐振频率处谐振电阻更小,能够对高频干扰提供更低阻抗的通路。

电容并联的频率阻抗特性