1前言

小编发现,很多硬件攻城师在设计PCB上的电源供应系统时,一般会在各个电源之间输入与输出加入磁珠隔离一下,这样能防止干扰。但是如果磁珠使用不当,也会造成负面影响。磁珠这玩意儿虽好但也不能贪杯哦,建议攻城师在使用磁珠之前先看看这篇来自业界著名 FPGA 供应商 Altera 公司的FPGA 电源设计应用笔记。

本应用手册介绍了如何正确选择磁珠以及一些设计方面的考虑,例如:anti-resonance、避免 LC 谐振效应、传输阻抗分析和直流IR压降最小化,同时还要满足去耦的目标阻抗要求。另外,还介绍了某些情况下使用 PCB 布局结构来替代铁氧体磁珠功能的秘技。PCB 结构与铁氧体磁珠的性能对比仿真结果,可用于评估验证 PCB 结构滤波器网络的效果,同时可以了解其诸多局限性。

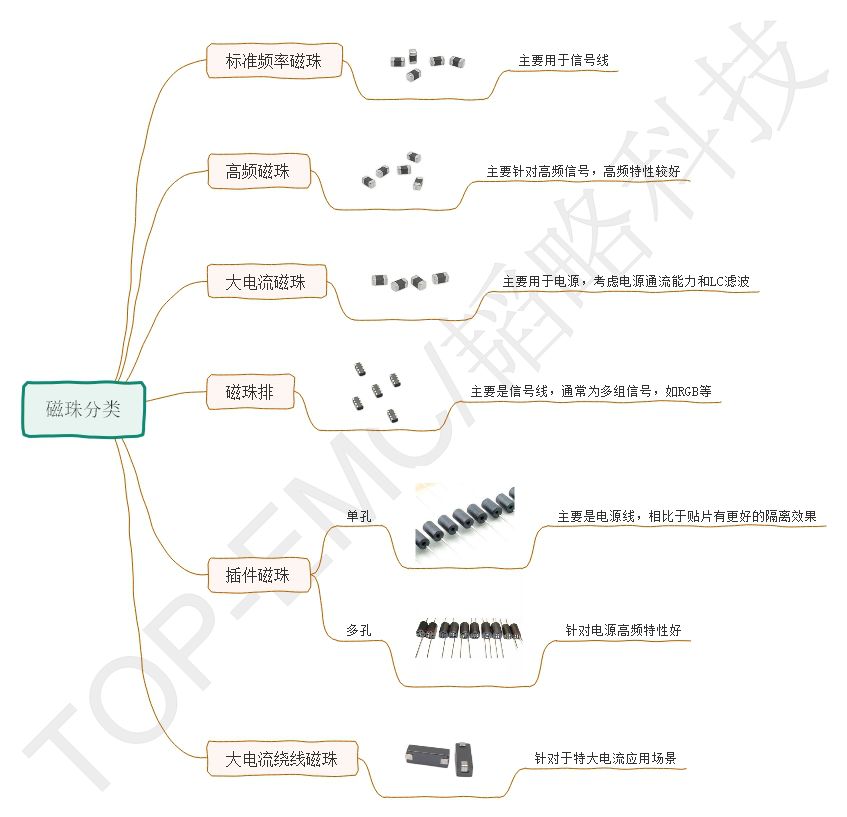

2铁氧体磁珠的选择

3铁氧体磁珠建模与仿真

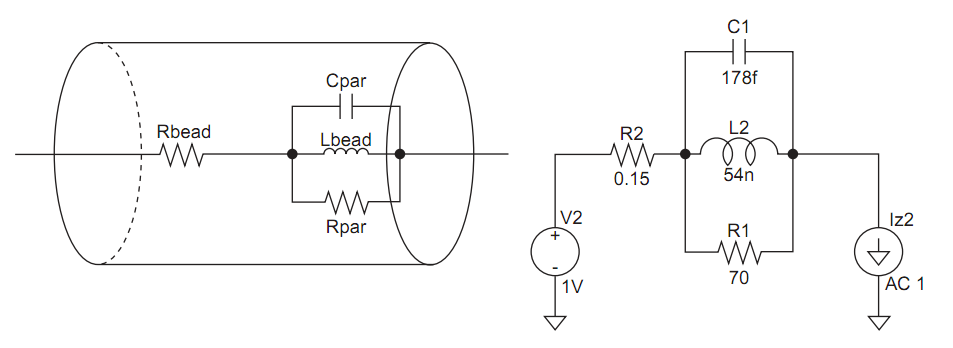

铁氧体磁珠厂商通常提供其器件的等效 SPICE 电路模型,以用于系统仿真。当无法从厂商那里获得铁氧体磁珠模型的情况下,可以将铁氧体磁珠建模成一个由 R、L和 C 元件组成的简单网络,如下图所示:

尽管该模型为 first-order approximation,但是您仍然可以将其有效地用于 sub-GHz 的仿真。

Rbead 和 Lbead 为铁氧体磁珠的直流电阻和有效电感。

Cpar 和 Rpar 为铁氧体磁珠相关的并联电容和电阻。

低频条件下,Cpar 为开路,而 Lbead 为短路,从而只有 Rbead 作为铁氧体磁珠的直流电阻。随着的频率增加,Lbead 的阻抗开始随频率 (jωLbead) 线性上升,而 Cpar 的阻抗随频率 (1/jωCpar) 反比例下降。铁氧体磁珠的阻抗-频率曲线图的上升斜率主要由 Lbead 的电感决定。

从某个高频点开始,Cpar 的阻抗开始占主导,而铁氧体磁珠的阻抗开始下降,从而降低其电感效应。这种情况下,阻抗-频率曲线图的下降斜率主要由铁氧体磁珠的寄生电容 Cpar 决定。Rpar 有助于减缓铁氧体磁珠的 Q 因子。然而,过大的 Rpar 和 Cpar 值会增加铁氧体磁珠的 Q 因子,并降低其有效带宽。形成高Q铁氧体磁珠,导致电源分配网络 (PDN)上出现不期望的瞬态振铃响应。

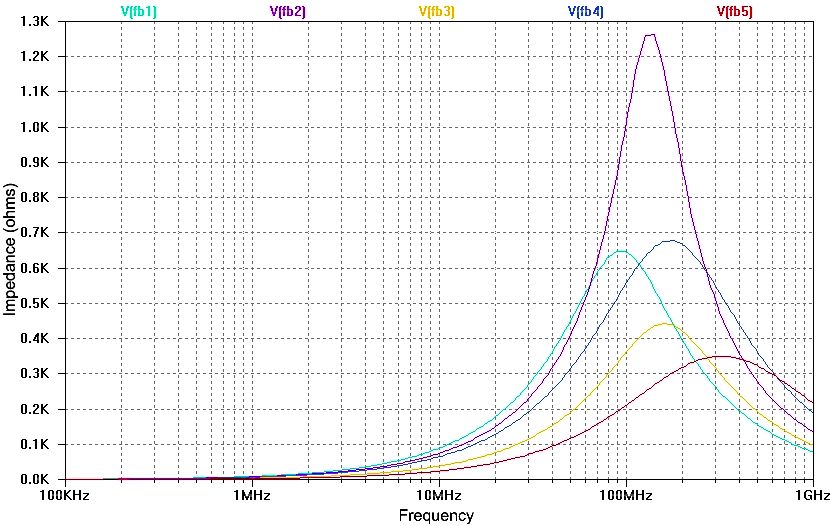

要想观察这些参数对铁氧体磁珠频率响应产生的影响,您可以使用 SPICE 来仿真用于隔离的铁氧体磁珠的交流响应。上图(右)显示了用于获取一个铁氧体磁珠样本的交流响应的 SPICE 电路设置, 其中DC电阻为 0.15Ω,有效电感为 54nH,并联电容和电阻分别为 178pF 和 70Ω。

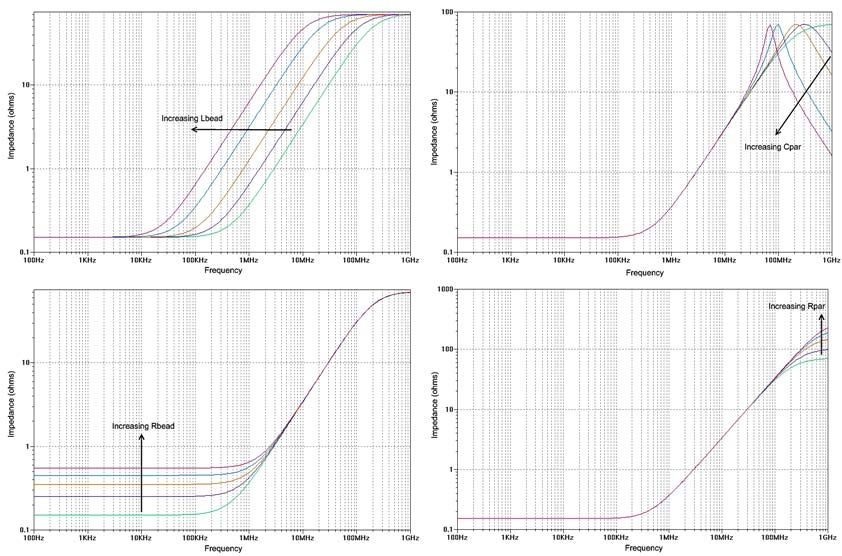

下图显示了 SPICE 中,施加一个 1V 电源和 1A AC电流负载,100 Hz 到 1 GHz范围内扫描的交流分析,得到的该铁氧体磁珠的特征阻抗-频率曲线图。在一些厂商没有提供 SPICE 模型的情况下,通过在模型中单独改变每一个 R、L 和 C 元件,可用曲线拟合方法来近似描述某个特定的铁氧体磁珠。

4设计建议

Altera 对您的设计提出如下建议:

选用一个铁氧体磁珠或设计 PCB 滤波结构,使其可以承载去耦电源所需的电流负载。

为了避免内核饱和,选择一个额定电流至少两倍于目标电源预计电流的铁氧体磁珠。

需最小化铁氧体磁珠或 PCB 结构的 DC 电阻,以减少 DC IR 压降。

确定所有压降都没有导致目标电源低于器件的建议操作环境。

使用 SPICE 或其它类似工具,以确保所有铁氧体磁珠或 PCB 电感结构带来的反谐振峰值均没有超出目标阻抗限制。

如果出现反谐振超标,向电源层添加大的Bulk去耦电容来减少或消除峰值。

使用 SPICE 或其它类似工具对有过大电压过冲或振铃的 PDN 电路进行瞬态响应分析,这种过冲或振铃可能会超出器件建议操作环境。

使用 SPICE 或其它类似工具对被隔离的电源对未滤波的电源层的传输阻抗进行分析,以获得充分衰减。

以上小编只截取部分内容,要获取全文百度云自取。点击阅读原文领取哦,提取码:7m5j 。