以前的FPGA设计很简单。设计人员只需在芯片中全局设置基本时钟约束即可。而如今FPGA设计变得复杂起来。设计中会有多个时钟,需要考虑这些时钟之间的关系。还可能需要考虑时钟域交叉的问题。因此,当今的FPGA设计工具必须拥有更强大的分析功能,从而为设计人员确定时钟域交叉的位置,或者能够约束多个时钟,并对I/O进行约束确保顺利进行芯片设计。

约束是用来指导FPGA设计的实现工具,例如综合和布局布线。它们可以让设计团队确定设计的性能要求并帮助设计工具满足这些要求。设计约束和时序约束在FPGA设计中十分重要,因为它们明确了工具需要优化和报告的内容。不受约束的设计不会获得优化和产生报告,因为没有对它们设置约束来明确其运行速度;此外,这些工具也不会告知设计的执行速度如何,因为没有明确的指示来告诉工具需要此类信息。

因此,在最新版本的莱迪思Radiant设计工具中,我们关注两个目标——性能和分析。

图1:Radiant 3.1

Radiant 3.1改进了时序约束和时序分析之间的关联性,从而让模拟性能尽可能地接近实际的器件性能。该版本的设计工具还延续了我们在时钟频率方面取得的进展。就去年而言,系统的平均最大频率(Fmax)增加了10%,运行时间减少了15%。

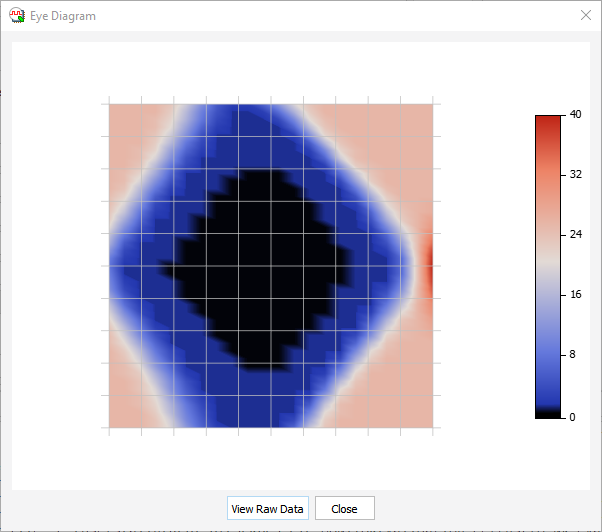

但要真正了解设计是否会达到要求的性能,你需要更多的“假设(What-if)”分析——尤其是在I/O上,便于更好地了解IO的使用。Radiant 3.1包括了一个独立的时序分析工具和一个差分I/O“眼图”监视器,显示从低到高的过渡,设计人员可以看到“眼图”的开口大小。设计人员可以微调SerDes设置以优化“眼图”的大小,从而优化操作窗口。

图2:CertusPro-NX SerDes I/O的眼图监视器

易于使用

莱迪思工具的一大优势就是,由于莱迪思专注于更小型的FPGA(Radiant最多支持100K LUT),与需要支持数百万LUT器件的Xilinx Vivado或Altera Quartus相比,它们更加高效。因此,与竞品解决方案相比,莱迪思工具的下载、安装和实现速度更快。如今伴随着Radiant的更新,我们可以一键读取代码、进行优化并产生结果。随着莱迪思向更高密度的器件进军,我们将继续改进基于分层模块的设计以支持大型的团队设计。从Radiant 3.1开始,我们新增了一个虚拟IO功能,可加快模块设计和宏创建,无需将内部信号映射到外部I/O引脚即可估算性能和利用率。

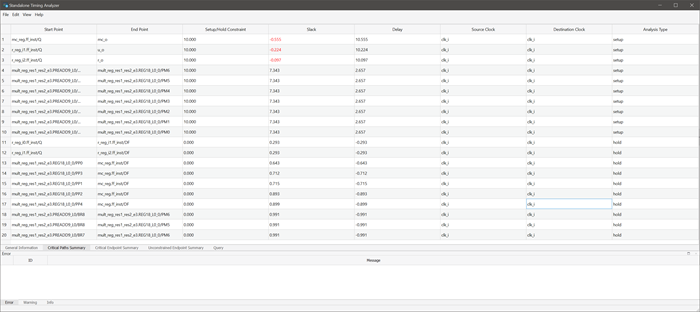

设计的复杂性始终存在,因此设计工具使用起来必须简单直观。我们的工具是FPGA行业中最为简便易用的工具。它们通过使用大量向导来指导设计人员完成整个设计过程,我们在工具中采用图形化约束方法,使约束管理更加便捷。报告的方式也很简单——尤其是可以进行独立的时序分析——下文的电子表格可以直观看到这些时序分析的内容。

不同级别的参考设计可以帮助设计人员更方便地使用FPGA——从简单的演示到特定应用,例如,实现PCIe接口或使用莱迪思解决方案集合实现机器学习视频传感器类型的应用,这些应用可能包含多个IP和不同的设计效果。

图3:独立的时序分析的报告

莱迪思还提供可达到最佳性能、最小面积和最低功耗的策略。这些Radiant的策略设置用于指导工具的行为、调整不同的综合选择、不同的映射和布局布线选择。

Radiant还提供了一个值得信赖的IP生态系统。除了采用非常易用和直观的用户界面外,Radiant环境还采用了业界领先的第三方工具,例如Synopsys的Synplify™ Pro综合工具和Mentor Graphics/Siemens的ModelSim™验证工具,这些工具广为人知,大家都在使用。

最后,除了莱迪思FPGA自身拥有的各类安全特性外,所有Radiant工具都经过数字签名认证,确保不会受到篡改。

Radiant经过优化,使用强大、准确的分析和调试工具为快速、高效的时序收敛进行了高级优化,实现可预测的收敛。