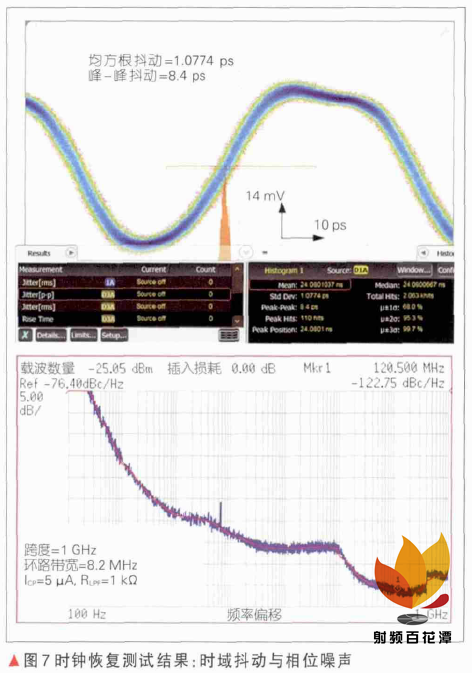

针对5G 通信中4 级脉幅调制(PAM4)格式数据的高速传输,提出了可集成的数据与时钟恢复中若干关键技术,包括波特率采样、边沿选择、最优采样和阈值调节等。在单路50 Gbit/s 以上速率可有效降低芯片硬件开销,降低系统功耗,降低误码率(BER),并可以提升芯片工作鲁棒性。上述技术在65 nm 互补金属氧化物半导体(CMOS)工艺下通过芯片设计及流片加工得到验证,测试结果表明:该芯片恢复时钟具备1.08 ps 均方根值(RMS)的时域抖动;恢复数据最高速率在51 Gbit/s 可实现3.4×10-9 的PAM4 信号BER,以及低至6.27 pJ/bit 的能耗效率。

1 光通信中的时钟与数据恢复

随着大数据和云计算技术的诞生,数据量呈现爆发式的增长,数据通信的带宽需求日益旺盛,而传统的电互连技术已经无法满足高速信息传输的需求。在此背景下,为了实现信息的更高速率的传输,利用光波作为传输介质,光信号作为信息载体的数据传输方案即光互连受到了越来越多的关注。光互连可以理解为光通信技术在短距离场景替代传统的电通信技术的一种实现形式,在具备光通信的所有技术优点的基础上,还具有更高性能的集成化、低功耗、低成本等特点,因此光互连能够实现超低功耗、较长距离、超高速、超高密度的数据通信,同时还具备无电磁干扰、短延时、长寿命、安全可靠等特点。由此可见,光互连技术代表了未来中长距离数据通信技术的发展方向。光互连具有低功耗和高集成度的特点,其中的核心是集成光子技术和集成电路技术,主要包括:高速激光器芯片技术、高速调制器芯片技术、集成光波导技术、集成驱动芯片技术、光电探测芯片技术、集成数字信号处理技术等。

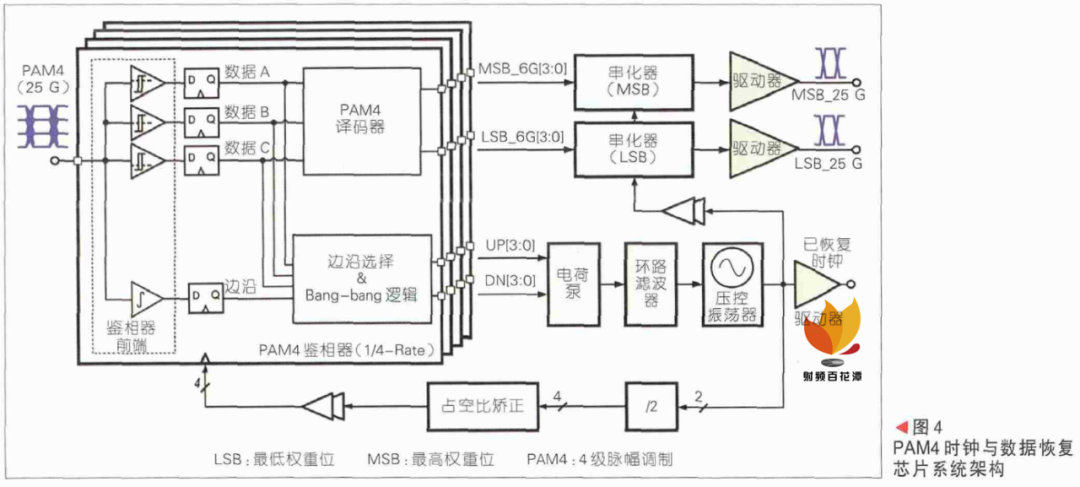

光互连系统是电光混合集成,由高速激光器和高速调制器将电信号加载到光波上,因此需要高速驱动芯片对激光器和调制器进行电信号到光信号的转换。当不归零码(NRZ)数据传输速率超过40 Gbit/s,电光转换的带宽成为限制光互连速度的瓶颈。4 级脉幅调制(PAM4)由于具有在相同带宽下2 倍的数据传输速率,得到越来越广泛的应用。在光互连系统中,当单通道数据速率达到25Gbit/s 时,无论在接收端和发射端都需要采用时钟与数据恢复(CDR)电路从高损耗的信号里恢复出高质量的数据,再通过驱动电路将数据加载到光波上。如图1 所示,PAM4 调制的CDR 电路在收发两端的电-光和光-电转换都是核心部件。在电-光转换接口,高速串行电信号经过高损耗电路板导致信号质量严重下降,通过PAM4 CDR 对信号进行恢复,得到低抖动的时钟和数据。在光-电转换接口,由于电光调制器的插入损耗及光纤传输损耗等,光电探测器接收到的有损信号同样需要CDR 进行数据恢复。

CDR 相对于锁相环(PLL)的区别主要在于鉴相器的设计上,CDR 基本的组成部分包括鉴相器(PD)、电荷泵(CP)、环路滤波器、压控振荡器(VCO)等。鉴相器通过用VCO 的输出时钟对输入数据进行采样来获得控制信号,控制信号输出到电荷泵产生控制电压来调节VCO 的振荡频率,由此恢复高质量的时钟信号和数据。PAM4 CDR 相对于NRZ 信号的CDR 而言,其设计难度增加很多,体现在:首先,高速多幅度信号的量化。PAM4 信号与NRZ 信号相比,对信噪比和电路的线性度要求很高,在对PAM4 信号进行量化时,需要3 个阈值,由于每级信号间的幅度降低为NRZ 信号的三分之一,那么对于阈值的偏差容限也降低了很多,如何准确地选择合适的阈值是一个难点。此外,由于PAM4 信号具有确定性抖动,对于高速信号而言,采样时钟的窗口变小,对时钟抖动的要求提高,增加了时钟链路的设计难度。其次,PAM4 信号中多种幅度转换类型下的时钟和数据对齐。PAM4 信号有12种电平转换模式,远多于NRZ 信号的2 种,在进行时钟数据边沿对齐时,其复杂度会增大很多。因此,需要选择合适的转换边沿来进行时钟与数据对齐,来降低鉴相器设计难度,减小误码率。由此可见,高速PAM4CDR 电路不仅需要考虑传统高速电路设计中的电路带宽、抖动、功耗等问题,还要结合新的调制格式下数据的特点来进行电路设计。

2 PAM4 时钟与恢复关键

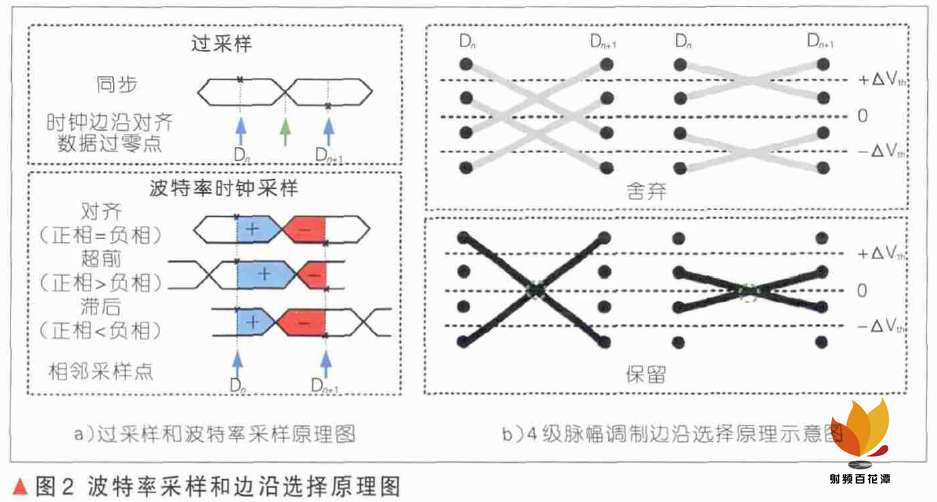

技术光通信中采用时钟与数据恢复技术实现2 个功能:首先,利用本地产生的多相位时钟对数据多次采样,判断数据比特的边沿,并通过PLL 将时钟边沿与其对齐,从而实现与数据同频率、同相位时钟的恢复。其次,利用已同步时钟的最优相位对输入数据采样,使其实现最高的输入信噪比,并把采样结果作为已恢复数据输出。如图2a)所示为传统的过采样型CDR,其中每比特数据采用数据(Dn)和边沿(Edge)2 个时钟相位进行采样,并最终将Edge 相位的时钟与数据边沿过零点对齐。其工作原理基于Edge 相位采样的数据值分别与上一周期数据Dn 及本周期数据Dn+1 进行比较的结果:当Edge 与Dn 的结果同为逻辑1 或0 时,表明Edge 相位超前于数据跳转边沿,判决结果为“ 超前(Early)”;而当Edge 与Dn +1 的结果相同时,表明Edge 相位滞后于数据跳转边沿,判决结果为“ 滞后(Late)”。随后锁相环路根据此结果反向调节时钟相位,最终实现时钟相位与数据边沿的对齐。不难看出:过采样型CDR 需要2 倍于数据率Nyquist 频率的时钟以产生足够多的相位进行采样,这带来了硬件开销的增大和系统功耗的上升。

2.1 波特率采样技术

2.2 边沿选择技术

2.3 最优采样与阈值调节

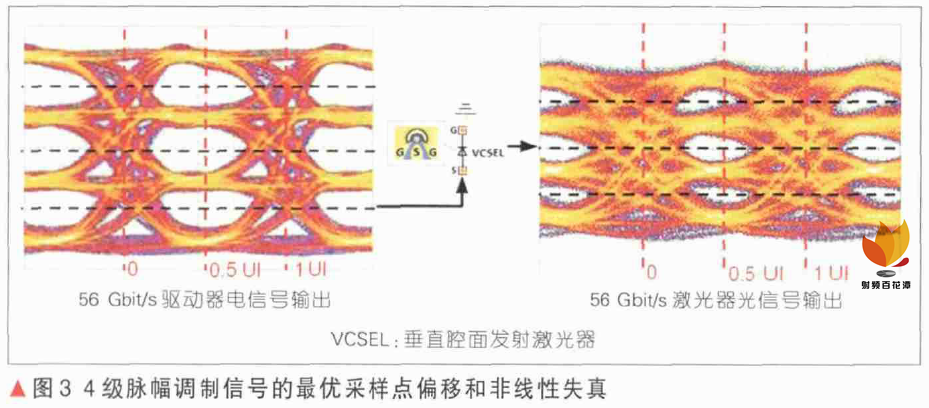

其次,在多幅值调制中特有的难题是PAM4 信号的非线性失真。具体来说,由于电信号输入信道的损耗或者电-光转换时引入的非线性,PAM4信号的3 个内眼可能具备不同的眼高与眼宽,这种情况下如果CDR 使用线性分布的阈值(图3 中横向黑色虚线)判别逻辑电平数值,将带来判决误码率的上升。例如:在直接调制型垂直腔体表面发射激光器(VCSEL)的光电发射机中,由于激光器本身非线性会导致光眼图的上升、下降时间不对称;而VCSEL 偏置电流较高时,其逻辑高的光功率受到压缩不再与输入电流成正比例关系,导致PAM4信号中逻辑±3 的眼高略低于逻辑±1的3 倍。

3 系统级设计

4 电路模块级设计

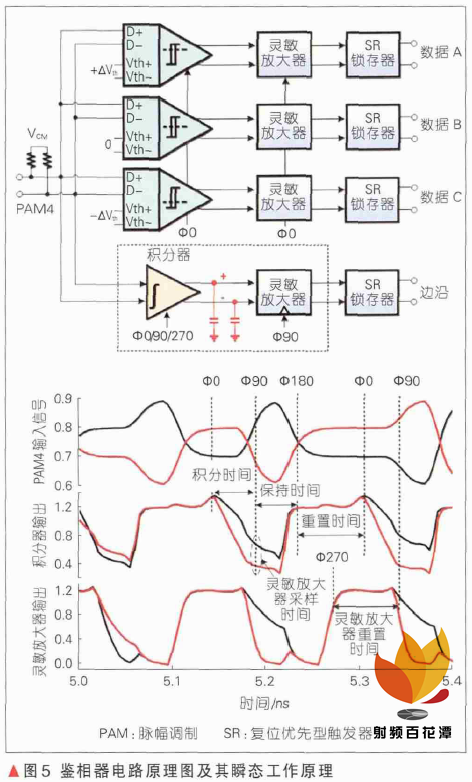

图5 描述了本文提出的波特率采样技术的工作原理。其中,ɸ0、ɸ90、ɸ180 和ɸ270 分别为采样时钟一个周期中的4 个相位0° 、90° 、180° 和270° ;PD 前端在1 个时钟周期内,将采样过程分成3 个步骤进行:积分阶段、保持阶段和复位阶段。在积分阶段,输入差分信号根据幅值和正负关系通过电容放电将输出电压分开;在保持阶段,上述差分电压输出被保持一段时间不变,以作为后级SR 锁存器的输入保持稳定;上述阶段完成时数据判决结束,进入复位阶段,输出节点重新被上拉到电源电压,等待下一采样周期的电容放电过程。需要注意的是:上述过程中,仅需要数据比特中心相位的时钟采样点,而节省了边沿相位采样点。

5 测试结果

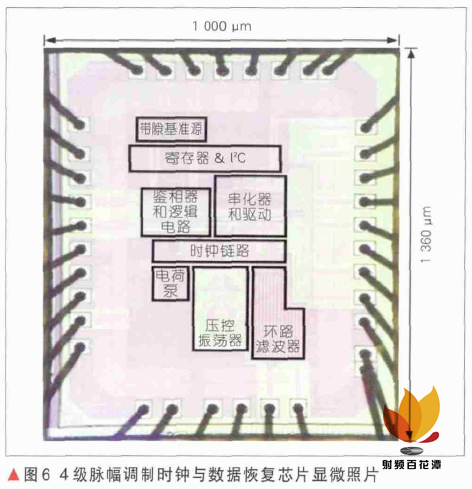

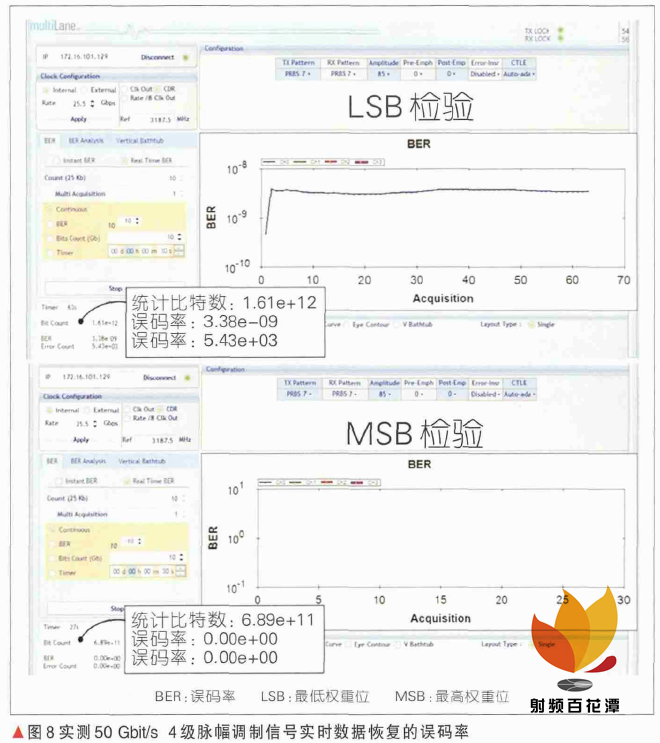

本文中我们提出的PAM4 信号时钟与数据恢复技术分别在65 nm 和40 nm 互补金属氧化物半导体(CMOS)工艺下进行2 次流片得到验证:如图6 中所示为利用波特率采样技术的65 nm 50 Gbit/sPAM4 CDR 芯片,该芯片共占用面积1.36 mm 2 并包含焊盘和3 kV 静电损伤(ESD)保护环。芯片的功能和性能测试均采用直接PCB 金线键合的封装形式。为测量CDR 误码率,25 G Baud/s 的PAM4 信号采用PRBS-9 编码作为输入,该信号在到达待测芯片之前经历同轴电缆线和板上传输线的高频损耗。CDR 芯片从输入PAM4 信号中恢复出2 路25 Gbit/s 的NRZ信号,分别对应于PAM4 解调之后的MSB 和LSB 位,并输出给30 G 误码仪分别进行测量对应的BER。

图8 所示为本文中CDR 芯片实时数据恢复的误码率(BER),测量时芯片输出到误码仪并实时与信号源的原始数据逐个比特进行对比。其中,MSB 数据输出所对应的BER 为0(低于10-12 认为无误码输出);LSB 数据对应的BER 约为3×10-9,满足带前向纠错功能的PAM4 通信网络的需求(常见数值为10-4~10-6)。通过测试发现:由于该芯片CDR 输入未集成信道均衡,PAM4 信号到达CDR 已存在较明显码间干扰,进而限制了BER 未完全达到0。

6 结束语

本文中我们介绍了单路50 Gbit/s速率光通信高速PAM4 调制下电路设计的挑战和潜在解决方法,提出了一种基于积分前端电路的数据与时钟恢复技术,该技术能够在高速率下节省鉴相器和时钟网络近一半硬件开销和功耗代价。上述技术通过65nmCMOS 工艺进行流片验证,实测获得最高51 Gbit/s PAM4 信号输入下恢复时钟1.08 ps RMS 的时域抖动,并且还实现了3×10-9 的数据误码率以及6.27 pJ/bit 的能耗效率。

来源:中兴通讯技术

声明:

投稿/招聘/推广/宣传 请加微信:15989459034