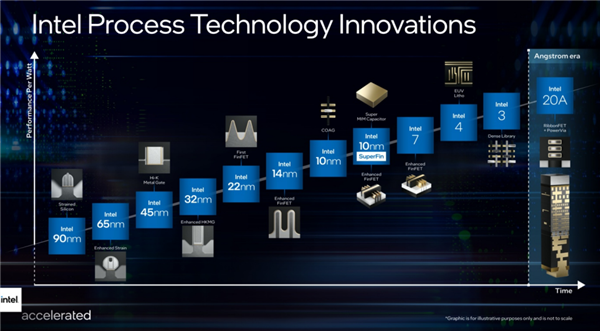

Intel作出了重大的工艺改名,10nm变成intel 7,7nm变成intel 4,不再使用纳米,循序渐进地提升芯片的性能,英特尔将采用两项突破性技术PowerVia 和 RibbonFET去开启埃米时代。

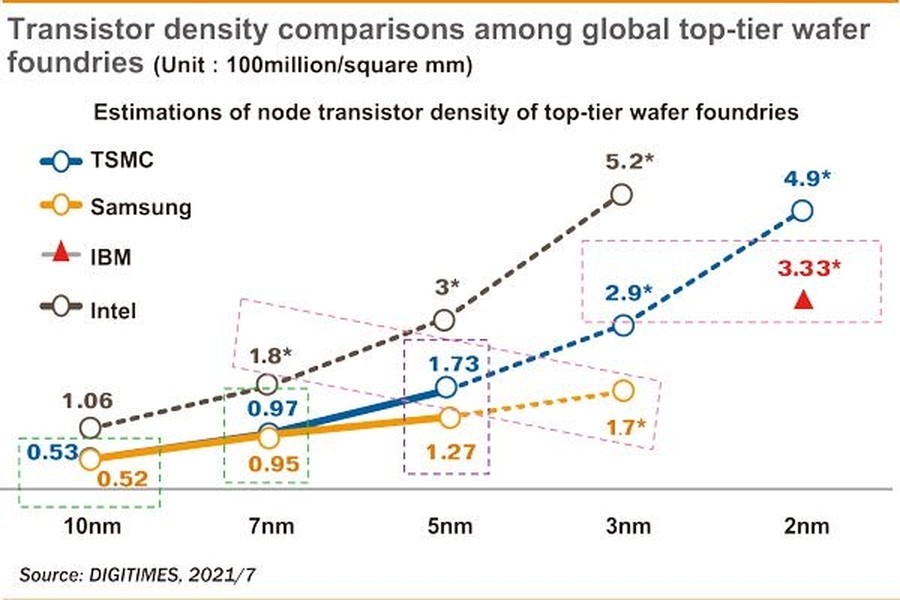

Digitimes在日前发表的研究报告中,分析了三星、台积电、Intel及IBM四家的半导体工艺密度问题,并对比了10nm、7nm、5nm、3nm及2nm的情况。

从表中可以看到,英特尔工艺在目前10nm节点上晶体管密度已经达到了已经达到了1.06亿/mm²,略超三星与台积电在7nm上分别0.95亿/mm²和0.97亿/mm²的密度。

而在下一代7nm的节点,英特尔目标将晶体管密度提升至1.8亿/mm²,如果计划达成,其密度不仅将超过目前台积电最新的5nm工艺,更大幅甩开三星的5nm。

在随后的5nm工艺中,英特尔将目标定在了3亿/mm²,此目标同样高于台积电的3nm计划,与三星3nm的差距还会进一步拉大。

Intel 10nm工艺

分析发现,Intel 10nm工艺使用了第三代FinFET立体晶体管技术,晶体管密度达到了每平方毫米1.008亿个(符合官方宣称),是目前14nm的足足2.7倍!

作为对比,三星10nm工艺晶体管密度不过每平方毫米5510万个,仅相当于Intel的一半多,7nm则是每平方毫米1.0123亿个,勉强高过Intel 10nm。

至于台积电、GF两家的7nm,晶体管密度比三星还要低一些。

换言之,仅晶体管集成度而言,Intel 10nm的确和对手的7nm站在同一档次上,甚至还要更好!

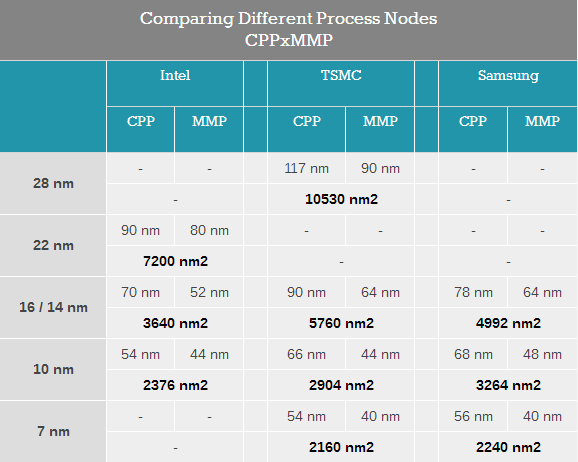

回到晶体管密度上,衡量晶体管密度的另一种方法是CPP*MMP,即将栅间距(接触多晶硅间距Contact Poly Pitch)乘以鳍间距(最小金属间距)。种种这些改进加在一起,使Intel的CPP*MMP尺寸只有54nm*44nm,相比台积电和三星的7nm也只是略输一点点,这也是Intel一直强调前两者只是商业命名的原因。

另外,Intel 10nm的最小栅极间距(Gate Pitch)从70nm缩小到54nm,最小金属间距(Metal Pitch)从52nm缩小到36nm,同样远胜对手。

事实上与现有其他10nm以及未来的7nm相比,Intel 10nm拥有最好的间距缩小指标。

Intel 10nm的其他亮点还有:

- BEOL后端工艺中首次使用了金属铜、钌(Ru),后者是一种贵金属

- BEOL后端和接触位上首次使用自对齐曝光方案(self-aligned patterning scheme)

- 6.2-Track高密度库实现超级缩放(Hyperscaling)

- Cell级别的COAG(Contact on active gate)技术

当然了,技术指标再先进,最终也要转换成有竞争力的产品才算数。

7nm工艺

若要谈7nm的性能强度,我们可以以新款iPhone为例,谈谈7nm和Intel 10nm处理器的差距。新款iPhone最吸引人的创新其实就是这款基于7nm工艺制程的A12处理器,苹果仅用一年时间就从10nm制程的A11升级到可以商用的7nm制程芯片,而其他移动芯片厂商比如高通,可能要在2019年才能推出基于7nm制程的芯片。

预计A12处性能相较理器于A11 Fusion会有更加明显的提升,CPU性能预计提升在25%左右,图像处理性能可能会提升超过30%。没有意外的话GPU内核将由3个提升到6个,并且会结合AR应用推出更多有意思的AR游戏,新一代怪兽级别的处理器即将诞生。

新推出的iPhone X Plus电池容量预计会在3200mAh左右,根据A12代工厂台积电官网显示,7nm制程的芯片功耗相比上一代芯片最高可以降低40%!这才是真正的突破,下一代大屏iPhone X Plus的续航可能不再会是iPhone的短板了。而5.8和6.1英寸的iPhone电池容量可能不会有明显变化,但是续航相较于A11处理器的iPhone X还是会好一些。

不过近几年移动芯片工艺的提升比我们想象的要快得多,并且5nm很有可能是目前芯片的极限,如果要进一步提升工艺的话,目前最大的难题依旧是FinFET结构也不能在保障性能的前提下同时抑制漏电情况,在这样小的尺度下,可能会有经典物理的短沟道效应、量子力学的量子隧穿效应等等物理学的影响,目前还没有很好的方法应对这些情况。

以往 Intel CPU 的制程命名方式就一直坚持摩尔定律的规则,只有当新工艺能实现的晶体管密度到达上一个工艺的两倍时,才会更新一次制程命名数字。

例如 AMD 去年发布的锐龙 5000,该系列CPU 采用台积电二代 7nm 制程,晶体管密度是 110MTr/mm²。

三星初代 5nm 制程,晶体管密度是 112.79MTr/mm²。

而 Intel 的 二代 10nm 制程,密度也达到了 100.8MTr/mm²,虽然依然差了一点,但远没有命名看上去那样成倍的差距。

Intel为何换命名?

具体来说,10nm Enhanced SuperFin改名为Intel 7,7nm改名为Intel 4,未来还有Intel 3,这足以让Intel面对台积电的5nm、3nm工艺时不落下风,至少名字上对应起来了。

对于换命名一事,Intel表示,此前的工艺节点命名规则始于1997年,都是以实际的栅极宽度来定义(xxnm),但是近些年来,工艺命名和栅极宽度已经不匹配,因此Intel启用了新的命名方式,便于产业、客户、消费者理解。

如果要深究下Intel为什么过去十几年都在坚持,今年偏偏就不肯沿用之前的命名体系,那就有意思了,因为Intel是不想吃亏了,友商多年来在工艺命名上占尽了便宜。

Intel高管在日前与超频玩家Der8auer的交流中透露,基于栅极长度的纳米命名已经有12年历史了,已经不能反应现在的工艺水平,Intel敦促业界统一一种标准以便所有客户都可以理解,但是Intel的友商多年来对这一提议置若罔闻。

如果看晶体管密度,Intel以前的命名确实吃亏,10nm工艺的密度就达到甚至超过了三星、台积电的7nm,但消费者都会认为后者更先进。

责编:editorAlice