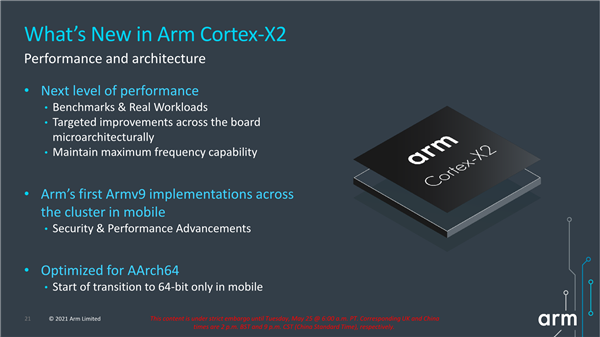

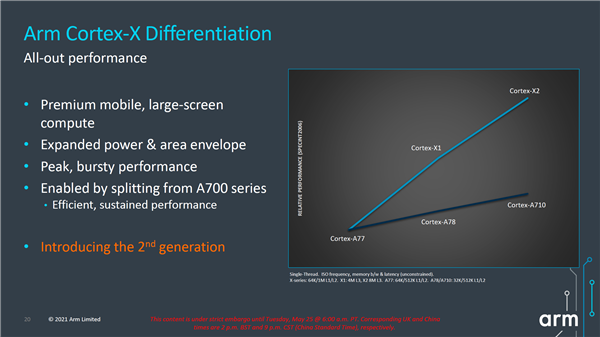

ARM在(5月25日)周二发布的旗舰产品就是所谓的X2计算核心,ARM可以为其每个大客户进行不同的定制。ARM 公司公布了基于 ARMv9 指令的移动设备向全新产品系列:Cortex-X2、Cortex-A510、Cortex-A710 CPU 内核以及全新的 Mali-710、Mali-310 GPU 内核。

5月25日,ARM发布了2020年度新品家族,包括纯粹64位的超大核心Cortex-X2、大核心Cortex-A710、小核心Cortex-A510(分别取代X1、A78、A55),三级缓存和丛簇设计DSU-110,互连网格网络IP CI-700,芯片网络IP NI-400。

A710、A510也是基于ARMv9 64位指令集,架构上和X2是相通的,因此可以集成于同一颗SoC,但需要注意的是,X2、A510都是纯64位,不再兼容32位,A710则继续支持OL0 AArch32。A710 同样可以作为 Big 引入到异构 SoC 中,但是在性能定位上要低于 X2,用于取代目前的 A78,A710 的 IPC 要比 A78 高 10%,人工智能性能是 A78 的两倍。

A510 用于取代目前的 A55 内核,采用顺序流水线,IPC 提升了 35%,人工智能性能提升了两倍,和上一代的大核 A73 相比,A510 的 IPC 差距在 10% 以内,但是耗电降低了 35%。

G710 旗舰级

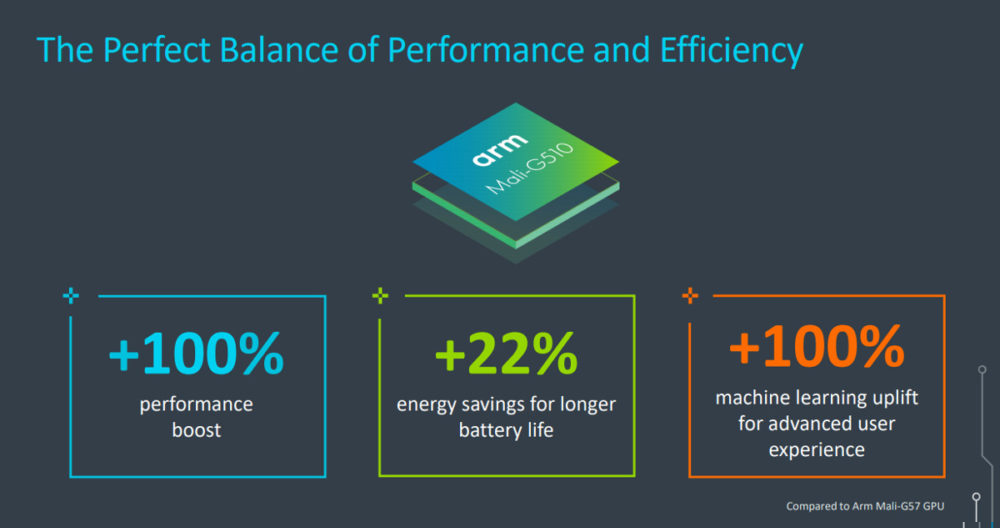

G510

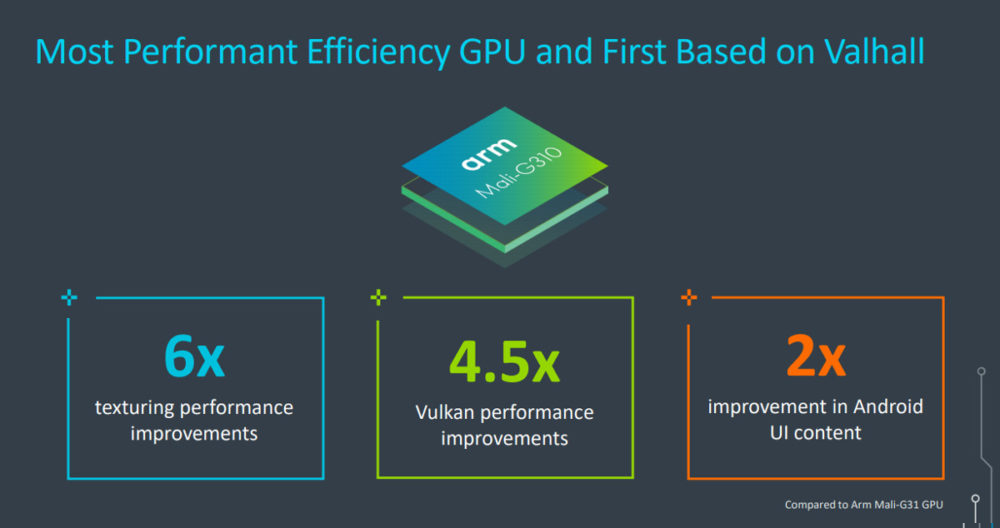

G310

这是应中国客户要求特殊设计的,因为中国市场还有太多应用停留在32位。

今年3月底,ARM正式发布了64位指令集ARMv9,号称10年来最重要的创新,IPC性能提升多达30%。

4月底,我们看到了ARMv9指令集的首个产品,面向数据中心的Neoverse N2(同时还有32位的Nerovers V1)。

现在,ARMv9首次来到了消费级市场,而且同时用于三种不同级别的核心,上来就是完整的一整套解决方案。

先来看超大核心X2,仅支持AArch64 64位指令而不再兼容32位,拥有全新层级的性能。

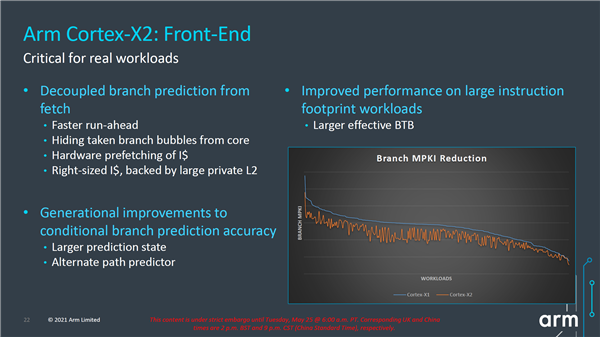

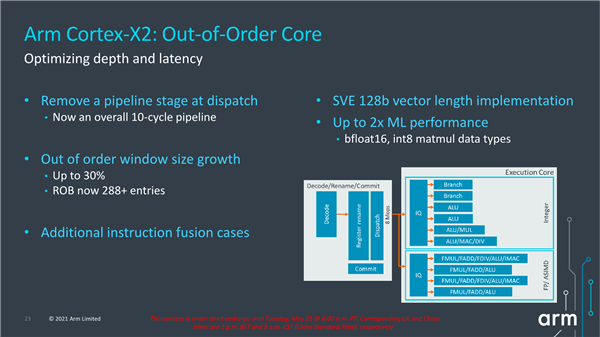

前端方面,分支预测与预取单元解耦分离,从而可以在内核之前提前运行,从而减少预测错误,同时改进了分支预测精度,提升了大型指令负载的性能。

核心方面,流水线长度从11个指令周期减少到10个,其中分派阶段从2个周期减少到1个,这可是个非常大的变动。

同时,乱序执行窗口增大了最多30%,244条增至最多288条,再加上指令压缩和绑定,实际还可以保存更多。

FP/ASIMD流水线现在支持SVE2,矢量长度为128b,可以大大提升机器学习性能。

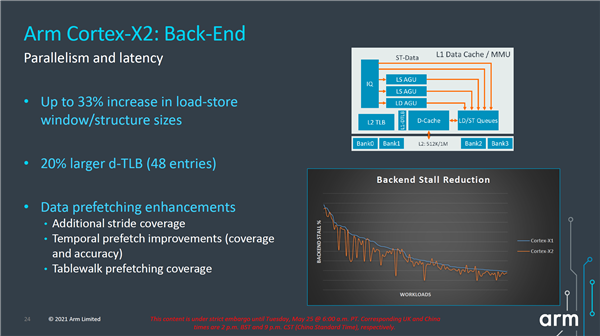

后端方面,载入存储窗口和结构增大了33%,可以提升内存级并行度,一级缓存d-TLB也增大了20%,另外增强了数据预取能力。

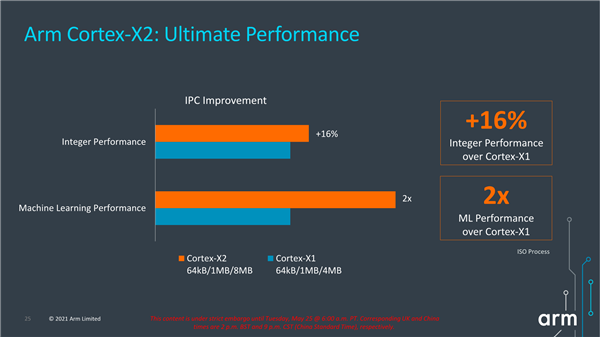

性能方面,ARM宣称X2相比于X1整数性能提升16%,机器学习性能则可以翻一番,不过注意对比时X2的三级缓存容量为8MB,增大了一倍。

X1核心何时商用取决于芯片厂商,不过ARM提到它正在用于笔记本等大屏计算设备,显然已经有了不少设计,只待宣布。

责编:editorAlice