随着AI技术向边缘和端侧设备广泛渗透,芯片设计师不仅需要考虑在其设计中引入加速器,也在考虑采用速度更快和带宽更高的总线和接口来传送数据。在2025年初于拉斯维加斯举行的消费电子展(CES)上,相关行业组织宣布了两项显示接口技术的重大进展,即HDMI 2.2和DisplayPort 2.1b;此外,加上去年下半年刚刚推出的蓝牙6.0和Wi-Fi 7等协议,让许多无晶圆厂半导体公司忙于将这些标准和协议集成到他们的芯片中。

针对这些新发布的标准和协议,以及他们相对更早的版本,验证IP(VIP)已被证明是一种能够更快和更好地验证芯片设计的方法。对于一个精明的芯片设计验证工程师来说,VIP远远不仅是一个朗朗上口的缩略词,有经验的设计人员都知道验证IP是带有可重用验证组件库和预定义功能单元的验证流的支柱,用以加速验证工作的核签。

随着需要处理和传送大量数据的智能设备快速广泛普及,各种总线、接口、协议和标准都在快速进步,促使芯片设计人员去找到高效验证其设计的方法。现在是时候把验证IP(VIP)放在其工具箱的最上层了。本文诠释了为什么在今天的电子行业中更加需要使用VIP在验证环境中来改进调试、覆盖收敛和提升质量,以加快项目交付和增加投资回报,并减少芯片重新流片的风险。

验证一款布满了集成IP单元模块的复杂片上系统(SoC)设计的功能正确性是一项艰巨的任务,其中许多模块都基于复杂的行业标准接口协议。这就是为什么验证团队在他们的验证策略中导入验证IP,并将其视为验证流程的关键组件的原因。它确保了在调试、收敛覆盖和验证质量方面的改进,并减少了项目进度中的复杂环节。它为行业标准接口和对互连协议的支持创建了基础设施,并为测试/验证(DUT)项下的设计提供了可进行比较的已知参考。

无论使用什么工具,验证都是复杂的,并且估计会消耗项目资源的60-80%。用于复杂SoC的测试台需要各种验证IP来验证系统级功能,并通过生成特定于应用的数据流量和检查器来确认目标性能。

使用高质量的VIP可以使设计师不必成为多种协议的专家。VIP负责根据协议规范的细节来验证设计,这是很“繁重的工作”。它生成全面的测试方案,去刺激和验证不同的接口和标准总线协议,缩短了SoC的验证流程并增加测试覆盖率。它包括事务/序列、驱动、配置组件和特定接口的测试计划,以及连接到测试台上的DUT测试套件,以模拟或模拟IP或SoC设计。

VIP是符合行业标准的即插即用模块,通过生成特定于应用程序的数据流来验证系统级功能和目标性能。

VIP不是一种验证方法。它与通用验证方法(UVM)和开放验证方法(OVM)不同,UVM是一种用于构建测试平台的Accellera互操作性标准,OVM是一种方法和功能单元库。验证IP是在可用的标准验证方法(如UVM)中实现的有价值的组件。

VIP由可重用的验证组件库和预定义的功能单元组成,它们创建了一种基础设施来支持行业标准接口、SystemVerilog和SystemC硬件验证语言(HVL),以及像UVM这样的方法。高质量的VIP是独立于平台,可以跨所有方法和语言工作。

当然,一些VIP针对的是某一个模拟和/或仿真平台,而不是所有的商业平台。从模拟到仿真的转换可能是确有困难、耗费时日和大量资源。然而,一些供应商提供了与平台无关的VIP,它可以跨不同平台无缝地使用覆盖驱动的验证流,包括模拟、仿真、FPGA原型和形式验证。

用于仿真和FFGA原型的验证IP单元模块是具有完全API兼容性的、可进行逻辑综合的寄存器传输级(RTL)代码,可以将设计从模拟转移到仿真。这些VIP模块是内置的智能调试器,提供快速编译和系统级模拟运行时间,以及快速固件/软件开发。其基础设施框架或测试台附带刺激生成器、监视器、计分板/检查器和功能覆盖模型。

正如我们在本文一开始就提到了,近年来各个行业组织和标准机构为了在智能化时代抢占有利位置,都在加速推出或者修订新的协议和标准。立即找到支持这些新的或修订的协议或开放标准,或处理整个验证流程的VIP可能是一个挑战。开发新的或定制的VIP需要时间,并且可能无法在验证平台之间进行移植。通过开发专门的编译器,可以快速创建新的VIP或基于现有的VIP进行定制,帮助减少推出新的VIP或对现有的VIP针对新功能进行定制所需的时间。

一款先进的编译器可以为业界带来诸多好处。例如,作为全球领先的设计IP和验证IP提供商,SmartDV开发了一种高度创新和极为高效的编译器“SmartCompiler”。该编译器通过与SmartDV的标准和协议专家配合,就可以为新的协议和标准快速生成设计IP和验证IP,不仅速度大大快于人工开发模式,而且还避免了由人工开发引入的错误和风险。

当然,一些(但不是所有)VIP的编译速度可能很慢,而另一些可能只针对特定的验证语言和方法,而与其他语言和方法不兼容。平台独立性和可重用性也是需要考虑的问题;一个常见的抱怨是验证工程师难以分析和调试结果;此外,人工开发的VIP可能无法保持同等水平的性能、生产效率、易于调试的能力和可读性。

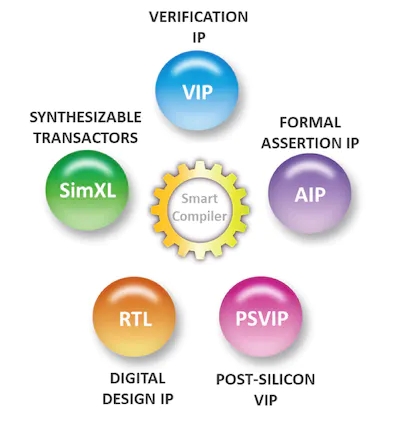

图片说明:一家第三方VIP供应商可以使用智能编译器来为一系列验证任务创建VIP,包括形式验证和可进行逻辑综合的事务处理器、流片后测试IP和设计IP,以及图中未包含的测试套件和文档。(来源:SmartDV)

在更高抽象层上编写的验证IP,即使用诸如SmartDV的SmartCompiler这种先进的智能编译器/生成器(见图)来生成的VIP的最终可部署版本,可以帮助开发者不必遇到这些抱怨。SmartCompiler这样的机器生成的VIP可以将代码质量和测试结果保持在事先确定的水平上,以有效地进行编译和执行。这样的VIP可以快速跟随和补充当今不断发展的标准与协议、以及硬件设计方法,该方法从更高层次的抽象编码设计规范生成RTL代码。

VIP通常由第三方供应商提供,这些供应商活跃于网络、存储、汽车、总线、MIPI和显示协议等领域内的接口标准开发组织。他们比内部资源更有优势,因为他们能够验证功能的正确性以及行业标准的符合性。除了这些能力,像SmartDV团队中的这些标准专家都具有标准和芯片设计两个方面的专业知识。

但是,验证工程师必须对第三方供应商的VIP进行研究和评估。如果需要,他们需要了解为VIP使用和定制提供的技术支持。对于不同的情况,支持可能不完全一样,定制可能既昂贵又耗时。评估过程的另一个重要方面是确保第三方VIP解决方案与标准完全兼容,并覆盖整个验证流程。

在实际应用中,没有一种统一的验证IP解决方案可以去覆盖整个验证流程。实际上,该过程的不同步骤需要不同的验证IP;在VIP提供的验证覆盖类型中通常存在空白。例如,用于模拟的VIP可能并不是用于仿真、形式验证和/或甚至流片后验证的良好解决方案。而专业的VIP供应商可以填补相关空白。

一个曾经流行的经验认为,VIP的最佳来源是来自提供验证和仿真平台的同一供应商。这过去可能是真的,现在也可能不是真的。在一个竞争异常激烈的市场中,这些供应商的主要业务通常集中在构建验证环境所需的软件和硬件的开发和销售上,这并不是一个很容易的细分市场。所以虽然他们也提供VIP,但这并不是其技术和业务的核心焦点。相反,这是一项用于帮助和支持销售更昂贵的软件和硬件平台的投资。专注于开发和授权VIP的供应商通常提供更广泛的产品和更好的支持,诸如SmartDV这样的领先设计IP和验证IP提供商的产品组合中都有数百种IP产品。

由于各项测试需要覆盖一系列场景并生成相当数量的测试,创建测试套件以覆盖100%的协议可能是一项艰巨的工作。对于主要业务不是创建VIP,而是为其EDA等工具创建支持解决方案的VIP提供商来说,这样的任务可能是一种负担。对于专门生产VIP的公司来说,情况并非如此。他们是专家,并在生产过程采用了先进的工具,以产生所需的测试套件,以实现100%的协议覆盖率,并与所需的文档配对。

全球电子行业将在2025和未来的几年看到各种新标准和协议的更快推出,因此现在是与那些拥有先进的VIP开发工具,并拥有熟悉这些标准和协议的专家VIP提供商深入合作的时候了。