现代半导体工艺极其复杂,包含成百上千个互相影响的独立工艺步骤。在开发这些工艺步骤时,上游和下游的工艺模块之间常出现不可预期的障碍,造成开发周期延长和成本增加。本文中,我们将讨论如何使用 SEMulator3D®中的实验设计 (DOE) 功能来解决这一问题。

在 3D NAND 存储器件的制造中,有一个关键工艺模块涉及在存储单元中形成金属栅极和字线。这个工艺首先需要在基板上沉积数百层二氧化硅和氮化硅交替堆叠层。其次,在堆叠层上以最小图形间隔来图形化和刻蚀存储孔阵列。此时,每层氮化硅(即将成为字线)的外表变得像一片瑞士奶酪。在这些工艺步骤中,很难实现侧壁剖面控制,因为刻蚀工艺中深宽比较高,且存储单元孔需要极大的深度。因此,刻蚀工艺中可能会出现弯折、扭曲等偏差。从堆叠层顶部到底部,存储单元孔直径和孔间隔可存在最高25%的偏差。

在存储单元孔中沉积存储单元材料后,在区块外边缘上图形化和刻蚀一系列窄长的狭缝沟槽。这第二次刻蚀暴露出狭缝沟槽侧壁中的牺牲氮化硅后,对其从边缘到中间进行横向刻蚀,直至完全去除。(1) 随后,沉积阻挡层化合物内衬和导电金属,填充氮化硅层边缘到中间的空间。这一工艺会生成金属栅极存储器单元和字线。(2) 从外部存储单元孔到狭缝沟槽内边缘的距离称为“轨距”(如图1)。该导通路径提供一条沿字线外边缘的低电阻传导通路。字线很长,通常等于存储区块的整个长度。为了维持所需的存储器开关速度,需要对字线电阻进行高度控制。

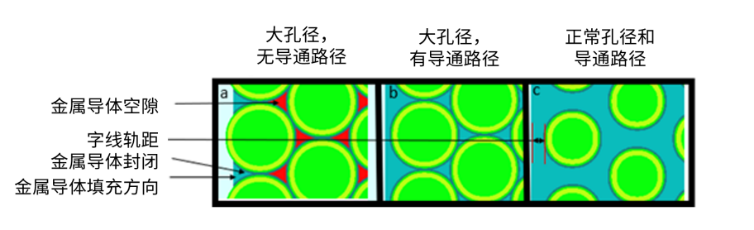

图1:虚拟模型实验的俯视图,每次实验(a、b和c)设置不同的实验条件。a) 模型中有较大存储单元孔、有空隙、无字线导通路径。字线空隙标红。由于存储单元孔间距较小,空隙引发封闭。b) 模型中有较大存储单元孔、字线导通路径正常、无空隙。c) 模型中有正常大小存储单元孔、字线导通路径正常。

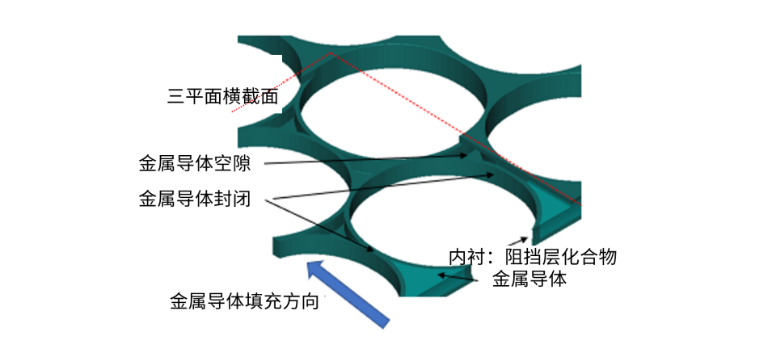

我们使用 SEMulator3D 模型以更好地研究 3D NAND 中字线电阻的影响因素。该研究表明,仅因为去除了存储单元孔中的导电材料,造成的 3D NAND 字线电阻远大于预期值。这表明,去除牺牲氮化硅,或用导电金属替换牺牲氮化硅的过程会形成空隙,从而增加字线电阻。SEMulator3D 虚拟模型显示,如果存储单元孔过大,或孔间隔过窄,通向字线内部的横向沉积通路将被封闭,并在导电金属中形成空隙(如图2)。

图2:SEMulator3D 虚拟模型展示了字线边缘的三平面横截面图。金属导体填充没有从狭缝沟槽边缘的封闭处持续到字线中心。电流仅通过内衬,从字线中心传导到封闭处。

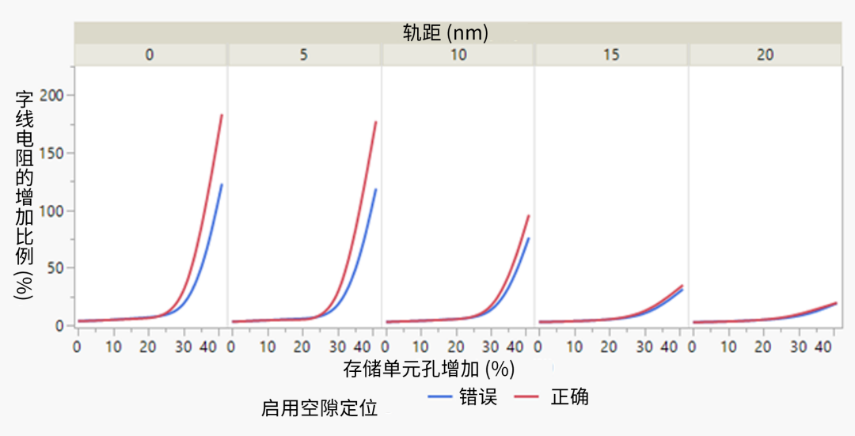

我们使用 SEMulator3D 工艺模型,以不同的存储单元孔直径、轨距和空隙定位,进行了200次虚拟模型实验。用 SEMulator3D 电性分析软件包模拟了字线电阻,随后从虚拟模型实验中提取字线电阻,并绘制了电阻增加百分比与轨距、存储单元孔径增加和带有空隙的对比图(如图3)。

图3显示了空隙形成对字线电阻的影响。如果比较无空隙时的字线电阻增加(红线)和存在空隙时的字线电阻增加(蓝线),空隙的影响比较明显。不考虑存储孔大小,空隙的存在使字线电阻增加了55%。增加外轨距后,存储单元孔大小对字线电阻的影响减少200%,并将引入空隙对字线电阻的影响降低到可以忽略不计的程度。结果表明,字线电阻随存储孔大小增加而增加。

图3:字线电阻增加(单位:百分比)与存储单元孔直径增加(单位:百分比)和轨距(单位:nm)的关系图。红线表示模型中包含字线空隙的结果(正确),蓝线表示模型中删除字线空隙并对其填充的结果(错误)。

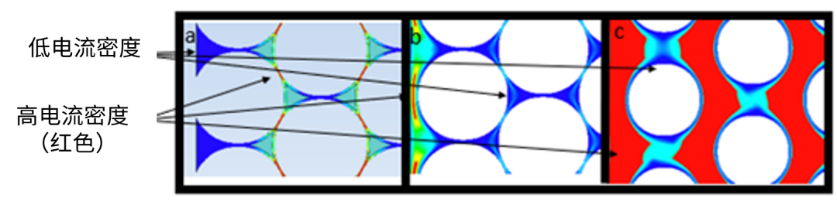

随着轨距趋于零,迫使更多电流流入字线内部区域。当存储孔尺寸增加时,空隙尺寸增加,低电阻导电金属和较高电阻的阻挡层化合物内衬间的体积减小(如图4)。当保留字线轨距时,字线电阻对存储孔尺寸和金属空隙的依赖降至最低。

图4:虚拟模型实验中的电流密度俯视图,每项设定(如图a、b和c所示)根据不同实验有所变化(参阅图1)。a) 导通路径不连续,导致电流流入字线内部。b) 存储孔大小与图a中的一致,但较宽的导通路径使电流沿着字线外边缘流动。c) 字线轨距产生更均匀的电流密度图形。

使用 SEMulator3D 空隙定位,虚拟模型可以在不考虑存储孔大小的情况下,预测空隙对字线电阻的影响。在实际的硅晶圆工艺中,没有办法在 3D NAND 工艺开发中对空隙形成和存储单元孔大小进行分离实验。SEMulator3D 可实现晶圆厂中很难或者不可能进行的实验。

我们用 SEMulator3D 工艺建模模拟了 3D NAND 字线形成工艺。我们观察到,上游存储单元空隙模块会对下游字线形成模块产生负面影响,并导致字线电阻的急剧增加。通过虚拟模型,我们得以模拟上游和下游模块间存在的问题,并用多次实验探索潜在的解决方案(在我们的案例中,解决方案涉及设计上的调整)。SEMulator3D 工艺建模可以在开发早期识别工艺和设计问题,其间无需大量的硅晶圆实验,这减少了开发延迟、晶圆制造成本和上市时间。

参考资料:

[1] Handy, “An Alternative Kind of Vertical 3D NAND String”, Jim Handy, Objective Analysis, on Semiconductor Memories, Nov 8, 2013.

[2] A. Goda, “Recent Progress on 3D NAND Flash Technologies”, Electronics2021, 10(24), 3156.