以下内容根据芯华章研究院研究员杨思超发表在《中国集成电路》的《Machine Learning for Verification:智能化EDA浪潮来袭》一文梳理,了解全文请点击文末“阅读原文”。

感谢《中国集成电路》对芯华章的认可!

为什么“AI+EDA”如此让人向往?

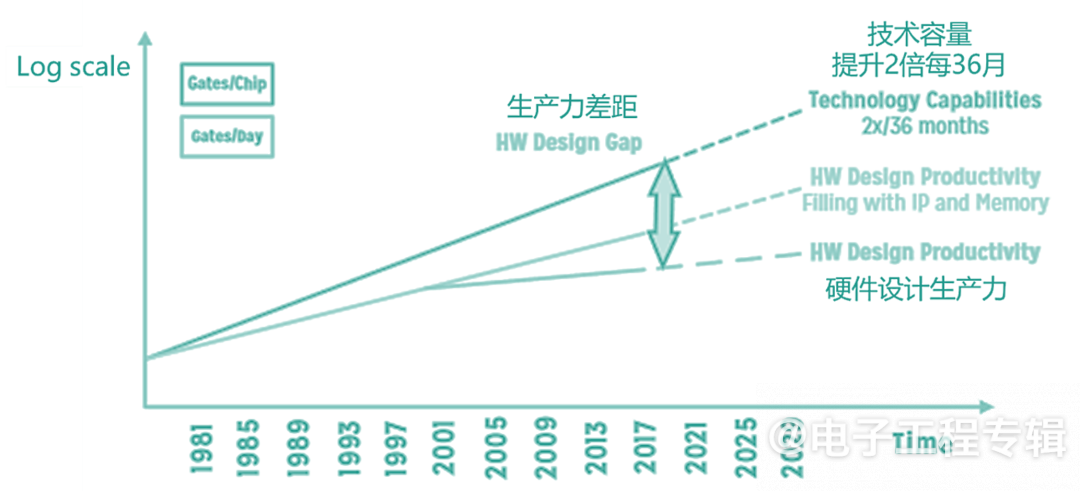

生产效率。当下大规模的芯片已经可以包含超过 100 亿个晶体管,而芯片研发的生产效率(Gates/Day)却没有办法保持同步的提升,两者之间存在一定距离。有研究表明,验证在某些项目中的耗时占比甚至超过70%,验证的效率因此成为了关键中的关键。

芯片规模和生产力的矛盾

研发成本。另一个问题是成本。由于芯片的研发成本非常之高,单次研发失败的概率理应被降到最低,验证的重要性自然不言而喻。因此现有EDA工具需要不断创新,来提升设计和验证效率。其中一个重要的创新技术点,就是引入数据驱动的方法来改进现有的算法和流程。

通常我们谈论的人工智能(AI)技术,主要分为机器学习(ML)和深度学习(DL)两种路径。其中,机器学习技术是现有和EDA结合更紧密的方向。为什么是ML?简单来说,ML技术就是通过统计模型在历史数据中发掘某种模式,然后在当前数据中识别是否存在该模式的技术。理论上,只要一个系统里存在无法被明确或精确定义的函数关系,又存在大量的观测或实验数据,就可以使用ML技术来学习。

而EDA领域里正好存在很多这样的系统。特别是传统的启发式策略逐渐趋于瓶颈,大量数据无法得到有效利用,通过引入ML技术,历史数据得到利用形成经验知识,再结合现有的技术可以进一步加速问题的求解,就可以辅助研发人员做出更优更高效的决策。

AI如何融入EDA?

看起来,我们似乎已经找到了这条通往答案的隐秘路径,但现实却更为复杂。

出于技术的天然契合性,目前因为EDA后端的设计和制造涉及到的数据类型,天然地可以被表示为几何图形,因此非常适合把原本应用在图像上的ML和DL技术做横向的迁移。但是,前端设计以及验证里的问题,通常都是基于布尔函数的组合搜索问题,这一类问题是目前公认ML或者DL很难求解或者精度上还没有能超越传统方法的问题。

简单来说,验证的目的是——在有限时间内,尽可能完整地覆盖到所有的系统状态,同时,尽可能多的找出功能或性能上的错误(bug),并进行修复以确保系统的正确性。

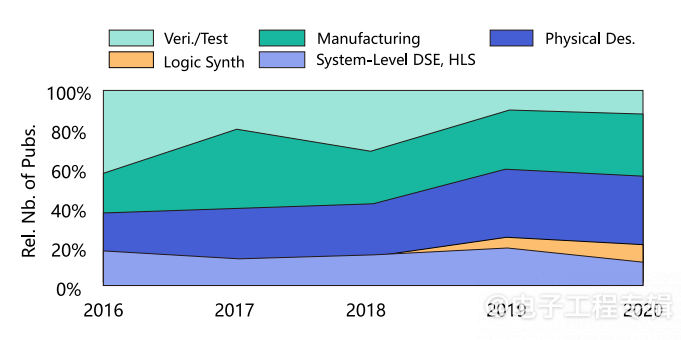

我们可以依据其实现的方式,大致分为两类——动态仿真和形式验证。目前在仿真验证里,关于融入AI的研究主要围绕如何通过ML提升测试效率或调试效率;在形式验证里则是围绕提升SAT求解器效率或模型检查效率的ML研究工作。

ML主题的文章里各细分领域的占比:后端上的研究增加明显

最大的挑战来自?

EDA行业的标准流程经历了几十年的发展,相对完善,当前ML技术通常是作为一个传统功能模块的替代,而一个end2end的ML方案很难被接受。

一方面,ML模型的引入可能会导致数据安全和模型所属权的问题。比如说客户A的设计和供应商的IP可能会在不知情的情况下被ML模型学习到,再在推理的场景下被客户B使用。

另一方面,IC领域的发展迅速,每一代技术节点对应的设计与制程都不一样,当前训练的ML模型很可能有效期太短。

最后,数据有限、精度不高、解释性不好等问题,依然在限制AI技术的应用。比如现在的AI技术很难给到用户其预测结果的合理解释,使得用户对于其预测结果的信任度不高,特别是在IC研发这样安全性要求非常高的领域,这一问题会进一步被放大。

系统级需求,驱动ML应用的三大方向

技术发展的挑战,最终还是需要通过技术发展来解决。

未来ML的技术需要朝着 reusability + evolvability + Interpretability 的三大方向继续发展,才能解决以上这些应用的痛点。同时,为了更好的支撑ML技术在验证里的应用,我们应该倡导系统级别的协同设计,进而发展出对ML更为友好的基础设施,例如:生成更可见、包含更多关系的数据,构建更适合于ML数据存放、使用和更新的数据仓库,提供ML模型更多和EDA系统交互及请求的权限等。

作为撬动芯片及系统创新的关键杠杆,EDA近些年在智能化、自动化的方向上一路狂奔,但属于这个领域的 “ChatGPT”,甚至 “AlphaGo”级别的突破,目前还没有出现。

唯一可以确定的是,AI与EDA的创新融合,绝不是简单形式上的增加,也不是摆在桌子上的自助餐,依然没有可以完全依循的标准答案,而是存在于各个隐秘的角落,亟待产业与学界的深入探索。

不只是EDA,AI技术的发展对芯片设计的影响,其实还有很多,体现在算法、架构等很多方面。5月19日,芯华章科技资深产品和业务规划总监、芯华章研究院研究部部长杨晔,与全球首家利用芯粒(Chiplet)技术研发车载大算力芯片的高科技初创企业——芯砺智能,就高性能计算的AI设计挑战及解决方案,一起讨论了从底层到应用的技术创新影响。欢迎大家点击观看!

Fabless100系列技术和应用直播 – 高性能计算的AI设计挑战及解决方案-EE直播间-EET电子工程专辑 (eet-china.com)

关于芯华章研究院

作为企业驱动型创研平台,芯华章研究院旨在凝聚国内外学界和行业中坚力量,从数字产业需求出发,推动异构计算、云原生、人工智能等EDA共性技术创新研究,以更智能易用的下一代EDA 2.0作为应用系统和芯片设计之间的桥梁,让芯片设计更简单、更普惠。

点击链接,下载完整版报告。

https://www.x-epic.com/index.html#/zh/article/detail?rId=d3c3e5beaaef4ba182dacaf046be2f81&id=8865f9be977b49038f5a6182c6f87dc4&l=zh_CN&t=1684767974470&t=1684810509065