2023年2月15日,中国,苏州——半导体存储解决方案厂商华邦电子今日宣布正式加入UCIe™(Universal Chiplet Interconnect Express™)产业联盟。结合自身丰富的先进封装(2.5D/3D)经验,华邦将积极参与UCIe产业联盟,助力高性能chiplet接口标准的推广与普及。

UCIe产业联盟联合了诸多领先企业,致力于推广UCIe开放标准,以实现封装内芯粒间(chiplet)的互连,构建一个开放的chiplet生态系统,同时也将有助于2.5D/3D先进封装产品的开发。

随着5G、新能源汽车和高速运算等技术的飞速增长,业界对芯片制程与封装技术的要求日益严格。如今,2.5D/3D多芯片封装可实现芯片性能、能效和小型化的指数级提升,已经成为行业聚焦的主流趋势。作为高性能内存芯片的行业领导者,华邦的创新产品CUBE: 3D TSV DRAM可提供极高带宽低功耗,确保2.5D/3D 多芯片封装的能效,并且为客户提供优质的定制化内存解决方案。

加入UCIe联盟后,华邦可协助系统单芯片客户(SoC)设计与2.5D/3D后段工艺(BEOL, back-end-of-life)封装连结。UCIe 1.0规范通过采用高带宽内存接口来提供完整且标准化的芯片间互连环境,促进SoC到内存之间的互连升级,以实现低延迟、低功耗和高性能。总体而言,标准化将助力加速推出高性能产品,为设备制造商和终端用户带来更高价值与收益,从而推动先进多芯片引擎的市场增长。

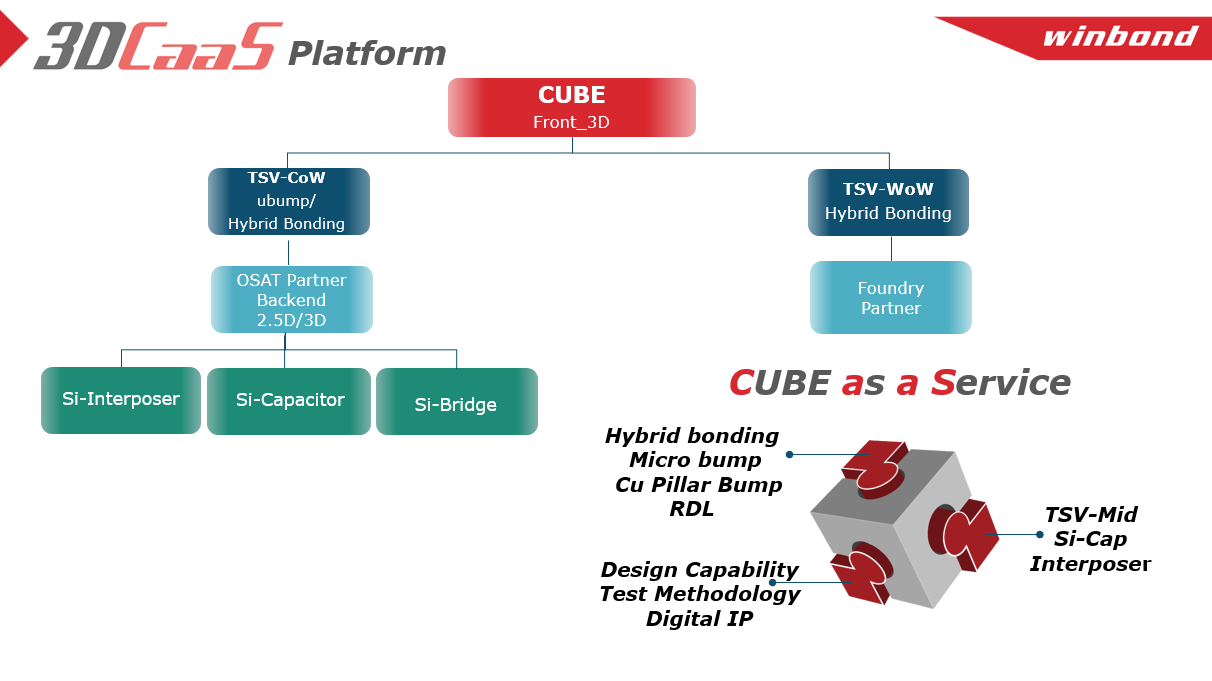

不仅如此,加入UCIe联盟后,华邦提供3DCaaS(3D CUBE as a Service)一站式服务平台,为客户提供领先的标准化产品解决方案。通过此平台,客户不仅可以获得3D TSV DRAM(又名CUBE)KGD内存芯片和针对多芯片设备优化的2.5D/3D 后段工艺(采用CoW/WoW技术),还可获取由华邦的平台合作伙伴提供的技术咨询服务。这意味着客户可轻松获得完整且全面的CUBE产品支持,并享受Silicon-Cap、interposer等技术的附加服务。

华邦电子DRAM产品事业群副总范祥云表示:“2.5D/3D封装技术可进一步提升芯片性能并满足前沿数字服务的严格要求,而随着UCIe规范的普及,我们相信这项技术将在云端到边缘端的人工智能应用中充分发挥潜力,扮演更加重要的角色。”

UCIe联盟主席Debendra Das Sharma博士表示:“作为全球内存解决方案的知名供应商,华邦电子在3D DRAM领域拥有坚实的专业知识,因此我们十分欢迎华邦的加入,并期待华邦为进一步发展UCIe生态做出贡献。”