全球最大代工服务供应商台积电(TSMC)近日将加速向45nm工艺发展的消息,就如同一声发令枪响,各大代工企业45nm节点竞赛就此展开。但事实上,目前种种迹象表明,对代工客户来说,向45nm节点的转变不仅代价高昂且充满艰辛。

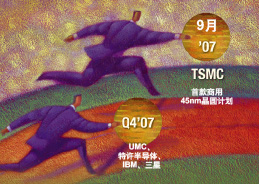

TSMC原计划在今年第四季度推出其第一款“商用”45nm晶圆,而且据称目前已将计划提前到了9月。其首个45nm工艺是一种低功耗技术,而且2008年上半年就会采用该工艺进行规模量产。

作为TSMC在45nm工艺方面的主要竞争对手,台联电(UMC)以及IBM技术联盟与TSMC之间并没有太大差距,而且二者也都计划在年底前推出各自的工艺。IBM的代工联盟伙伴是新加坡特许半导体和韩国三星电子。

虽然富士通、东芝、中芯国际(SMIC)及其它几家代工厂也有望涉足45nm工艺,但其是否加入或何时加入45nm竞赛,情况尚不明朗。

目前来看,问题是这些领先的代工企业是否能顺利地提供45nm工艺。虽然从90nm向65nm的过渡相当平滑,但有些人却担心,向45nm节点的转换是否会遭遇130nm节点所经历的梦魇。

在130nm节点,芯片制造商们将许多新技术(例如铜互连和低k电介质材料)引入到工艺流程中。为了保证按时交货,代工企业使出了浑身解数。

同样,在45nm节点,这些领先的代工企业还将首次采用193nm浸没式光刻技术和超低k电介质。但是,代工企业可能不会在45nm节点的早期阶段采用高k电介质或金属栅,因为目前人们仍然无法证明高k电介质是否适合量产。

“我不认为代工企业面对的挑战与IDM相比有什么不同,”Gartner分析师Dean Freeman表示,“采用浸没式光刻技术会带来挑战,低k电介质也会增加难度。”

另一个问题是代工客户接纳45nm的速度。事实上,对IC制造而言,仅IC设计一项的成本就在2,000到5,000万美元之间。考虑到光掩膜成本,90nm节点的“一套掩膜组”所需的费用在50到80万美元,65nm节点则需150万美元。在45nm,光掩膜成本要比65nm高出一倍,Open-Silicon公司协创人、总裁兼CEO Naveed Sherwani表示。Open-Silicon是一家无晶圆ASIC设计公司。

“但这并不会吓倒所有客户,”Sherwani指出,“我预计像赛灵思、英特尔和TI这样的高产量芯片厂商将带动45nm节点的进展。”

但MIPS科技公司营销副总裁Jack Browne表示,其它许多公司目前还不会一窝蜂跟进。“用老工艺更便宜,”Browne说,“所以原有工艺会存活很长时间。半导体领域有许多小公司,对它们来说,100万美元的掩膜费用太高了。”

认识到这一事实,一些代工企业已开始提供一种渐进的升级途径。TSMC目前推出一种55nm的半节点工艺,通过对其65nm工艺裸片进行缩微后实现。

TSMC计划在9月推出低功耗45nm工艺后,随之在2008年推出嵌入式存储器、通用高性能产品以及RF派生产品。据TSMC品牌管理总监Chuck Byers介绍,其中的一个重要产品是将于明年二季度推出的高性能逻辑技术。

“你将看到多种技术。”Byers说。

TSMC的45nm工艺据称能够提供两倍于65nm工艺的门密度,而功耗则会降低30%。该工艺采用了十层金属技术,带铜互连、应变硅,和k值为2.5的低k膜。

与其在90nm和65nm中的表现一样,TSMC在45nm也将采用基于Applied Materials公司“黑钻”(Black Diamond,即碳掺杂氧化硅)技术的低k膜。此外,它还将采用ASML Holding NV的193nm浸没式工具。

IBM及其合作伙伴特许半导体和三星并没落的太远。去年,该联盟宣布了开发45nm工艺的计划,并表示将于2007年底投入使用。与TSMC一样,这三家公司首先推出的也将是低功耗工艺。

F1:领先代工厂的45nm产品计划

该联盟称,其45nm生产已在按部就班的进行中。“我们目前正为客户提供原型硅,”IBM公共平台技术副总裁Steve Longoria介绍,“我们在65nm节点上曾稍有落后,但在45nm,我们与领先的代工厂齐头并进。”

IBM联盟提供“公共平台”?

人们猜想IBM联盟将发明一种“公共平台”,在该平台上,只要利用一个GDS-II文件,就可以在联盟内的任意代工厂制造芯片并进行移植。虽然一直有报道说联盟各成员在努力克服兼容问题,但是Longoria却否认了这些传言。

虽然如此,但是他承认45nm节点带来了诸多挑战。例如,有报道称,193nm浸没式工具需要在代工厂内进行一些手工操控,而且工艺缺陷也是个问题。“业界对浸没法存在许多恐惧、不确定以及怀疑,”Longoria说,“但我们仍然满怀信心。”

UMC在45nm工艺开发上有类似的时间表,但是其管理层并未对该技术进行任何评论。不过,这家全球第二大的代工厂向EE Times发表了一个声明。“尽管有FPGA和RF这样的应用,但是向45nm的迈进仍然面临诸多挑战。”UMC CRD Logic部门代理总监兼45nm开发主管Chia Wen Liang表示,“新的制造技术通常会导致缺陷问题。例如,在UMC目前的45nm SRAM生产中,就遇到了伴随浸没式光刻的缺陷问题,其中包括对表面涂层的选择。”

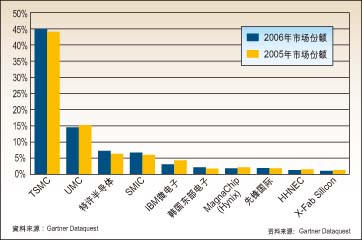

F2:10大晶圆代工厂的市场份额分配

“另外,由于受到栅介质材料的物理局限,传统的器件缩微方法在这里无法派上用场。所以,在45nm节点必须引入许多灵活性增强的技术,例如:SiGe、高压缩氮化物膜和用于多晶栅的stress memory效应。”Liang表示,“新的集成规划、新材料以及新工具,这些极大增加了45nm工艺的复杂性。”

这种极端的复杂性意味着,45nm代工竞赛才刚刚起步,距离竞赛结束还有很长的一段路,IBM的Longoria表示。“虽然一线代工企业计划在年底大力推动45nm工艺,但要过了明年夏天,才能看到一些结果。”他说。

作者:马立得