许多电信系统,包括那些基于先进电信运算架构(AdvancedTCA)规范的设计,需要保持其内部接口和外部网络的同步。为了能够实现这样的系统,AdvancedTCA或者PICMG3.0规范在架构中定义了一个同步时钟接口。根据这种规范,产生时钟信号的任务是由符合TIA/EIA-899(多点低电压差分信号传输或者M-LVDS)标准的集成电路来实现的。

本文提供了使用美国国家半导体的M-LVDS器件来设计符合AdvancedTCA标准的时钟分配网络的指南。该指南包括对AdvancedTCA标准的同步时钟接口的简要说明、M-LVDS标准的概述,还包括有关在AdvancedTCA背板上的M-LVDS器件性能的广泛讨论,和一整套有助于建立稳固的时钟分配网络的设计建议和规则。

AdvancedTCA背板上的同步时钟接口

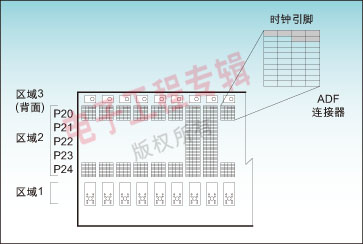

在一块AdvancedTCA背板(图1)上存在三种连接器区域:

1. 区域1为电源连接和机箱管理;

2. 区域2为数据传输接口;

3. 区域3为用户定义的I/O互连。

数据传输接口有基本接口、交换接口、更新通道接口和同步时钟接口。这些接口提供多达16组槽位连接。如图1所示,每个槽位可提供高达5个先进差分交换接口(ADF)或者区域2连接器。ADF连接器的实例是Tyco HM-Zd和ERNI ERmetZD。

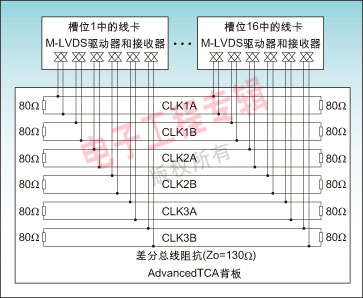

时钟同步接口可以使背板上所有的槽位相互交换时序信息。它由三对冗余时钟总线组成:CLK1A、CLK1B、CLK2A、CLK2B、CLK3A和CLK3B。PICMG3.0规范定义了每个时钟组的使用方法、频率和质量:

1. CLK1A和CLK1B提供冗余的8kHz标准数字语音传输系统的时钟信号;

2. CLK2A和CLK2B为SONET/SDH网络的同步提供19.44MHz的时钟信号;

3. CLK3A和CLK3B是用户可定义的信号(时钟或者数据)。

每个P20 ADF连接器的首两行引脚连接到6条时钟总线。总线实际上是130Ω阻抗的差分PCB走线,两端用80Ω电阻终结。图2说明了当三块或更多的线卡装入背板时,M-LVDS驱动器和接收器如何创建一个多点的时钟分配网络。

图1:在AdvancedTCA背板中的时钟引脚的位置

图2:连接到时钟总线的M-LVDS驱动器和接收器

M-LVDS概述

M-LVDS(TIA/EIA-899)标准详细说明了线路驱动器和接收器的电气特性。这些线路驱动器和接收器用于多达32个节点的多点总线内的通用数据传输。该标准更加明确地定义了驱动器的输出特性,以及两种接收器类型的输入特性。

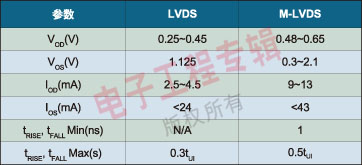

根据TIA/EIA-899标准,一个M-LVDS驱动器可产生一个幅度在480~650mV,失调范围在0.3~2.1V的差分信号。信号必须有超过1ns的10%~90%转换时间(上升和下降),和高达一半的单位间隔(tUI)来减轻多点架构造成的分支(stub)的影响。表1总结了LVDS(点对点拓扑结构的通用接口)和M-LVDS驱动器的关键特性。

表1:驱动器关键参数之间的比较

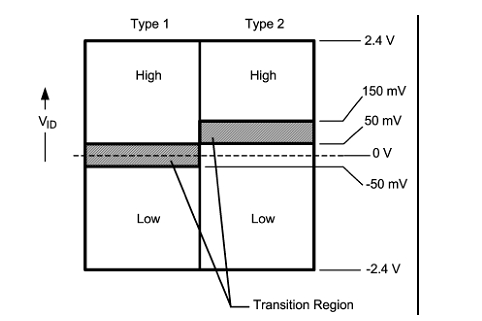

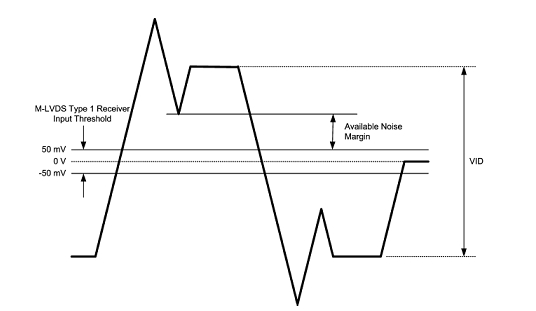

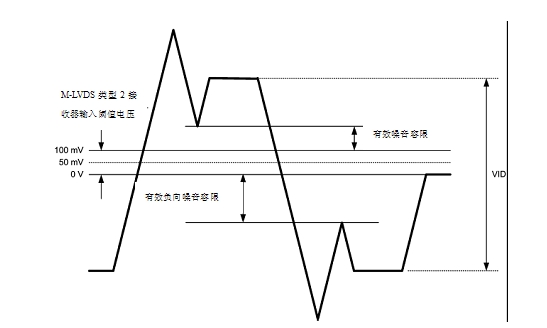

M-LVDS接收器的关键规格是输入电压阈值和输入共模范围。输入阈值电平区分了图3所示的两种类型的M-LVDS接收器。

图3:M-LVDS标准定义了两种接收器的类型

类型1接收器的阈值电平以0V居中,而且比类型2接收器提供更高的噪声容限。类型2接收器拥有较低的正噪声容限,但为控制信号提供了故障-安全防备(如图5和图6所示)。

图5:类型1接收器的有效噪声容限

图6:类型2接收器的有效噪声容限

接收器输入共模范围在-1.4V~3.8V之间,使得M-LVDS成为一个具有鲁棒性的接口,来连接那些参考地之间的电势差可能高达±1V的子系统。

在AdvancedTCA背板上的M-LVDS性能

目前,美国国家半导体M-LVDS产品系列包括四种单通道芯片。

1. DS91D176:一个具有类型1的M-LVDS输入的半双工芯片;

2. DS91C176:一个具有类型2的M-LVDS输入的半双工芯片;

3. DS91C180:一个具有类型1的M-LVDS输入的全双工芯片;

4. DS91D180:一个具有类型2的M-LVDS输入的全双工芯片。

下面叙述了M-LVDS系列的代表产品DS91D176在AdvancedTCA背板上的性能,详细说明了实验装置、实验方法和结果。

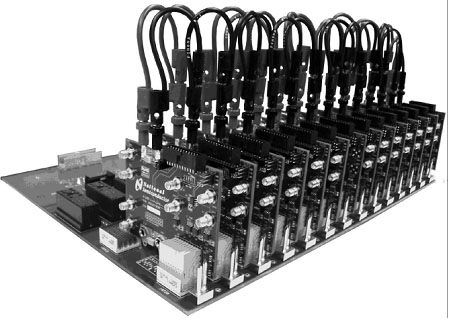

实验装置描述

可用ELMA Bustronic(www.bustronic.com)开发的一种14槽位符合双星形AdvancedTCA标准的背板和美国国家半导体开发的14块线卡(P/N:DS91D176EVK)来对不同的多点时钟分配网络进行实验。每块线卡中起重要作用的是六个DS91D176器件,其M-LVDS I/O引脚连接到一个ADF连接器。通过在背板上安装线卡,线卡上六个器件分别与背板上的六根时钟总线相连。所有十四块线卡的安装创建了六路多分支网络。每块线卡都可以设置为一块驱动卡(所有六个器件都可以配置为M-LVDS驱动器)或者一块接收卡(卡上的所有六个器件都可以配置为M-LVDS接收器)。图4显示了装满M-LVDS线卡的背板照片。

图4:装满M-LVDS线卡的14槽位AdvancedTCA背板

在M-LVDS线卡上,连接M-LVDS I/O引脚到总线的未终结的短PCB走线(信号线分支)对于每个器件来说有不同的几何形状。信号线分支的长度范围从0.25~2英寸(1英寸≈2.54cm),差分分支线阻抗的范围为80~130Ω。表2显示在线卡上的信号线分支的特性。

表2:M-LVDS线卡信号线分支特性和引脚映射

实验方法

在评估M-LVDS时钟分配网络的性能时,主要是靠噪声容限将一个好的设计与仅处于临界状态的设计区分开来。信号线分支在多支点环境中是影响噪声容限的主要原因。它们通过两种方式减少噪声容限:

1. 信号线分支加载到总线从而减少了驱动器输出信号的幅度;

2. 信号线分支造成了阻抗不连续从而引起信号反射,最终会减少有效的噪声容限。

在这个实验中,评估方法包括:在每个接收器输入端考虑有效的噪声容限;检查时钟驱动器位置和信号线分支特性对噪声容限的影响。

实验结果

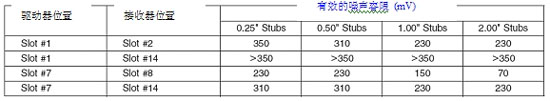

采用不同的多分支配置、分支线长度、分支线阻抗和频率进行广泛的实验,可得出以下结论:

1. 如果驱动卡的位置更接近终结电阻,接收器输入端的噪声容限会更高。换言之,背板上第一个和最后一个槽位是最好的驱动卡位置。在中间的槽位是最差的。

2. 驱动卡邻近槽位的接收器的噪声容限是最低的;与驱动卡距离最远的接收器的噪声容限是最高的。表3显示出离驱动卡最近和最远的接收器的有效噪声容限。背板是满载的,时钟频率为19.44MHz。

表3:取决于驱动卡和接收卡的位置和分支线长度的噪声容限

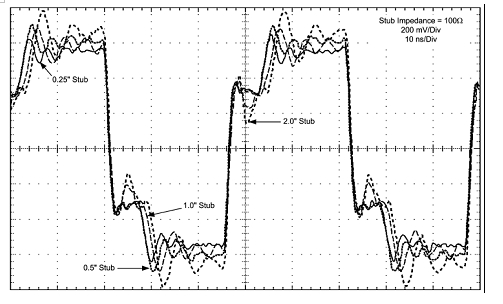

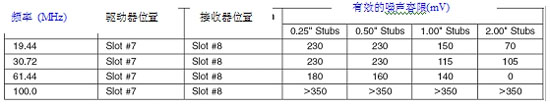

3. 信号线分支越短和越窄,其噪声容限就越高。一旦分支线作为未终结传输线,在它连接总线的位置点上,会降低总线那部分的阻抗。这些沿着总线的阻抗变化或者不连续会造成信号反射,进而降低噪声容限。图7显示出当7号槽位的驱动卡驱动19.44MHz的时钟至所有的十三块接收卡时,分支线长度对8号槽位接收器的有效噪声容限的影响。

图7:分支线越短则噪声容限越大

4. 具有0.25、0.5、1和2英寸信号线分支的四种网络在其邻近接收器的输入端测量出的四种波形如图7所示。很清楚地发现,来自具有2英寸信号线分支的网络的接收器有最低的噪声容限。表4给出了当7号槽位中的驱动卡在某些通用频率下向所有十三块接收卡驱动时钟信号时,测量8号槽位接收器得到的噪声容限。

表4:随着分支线缩短而增加的噪声容限

正如表4中数据表明的,当时钟信号频率在60MHz附近时,给定配置存在最差的噪声容限。在时钟信号频率为100MHz,即AdvancedTCA系统允许的最高频率时,信号存在最大的衰减,变成正弦波形,在接收器上不存在任何大的信号反射。因此,噪声容限在那个频率点具有最大值。

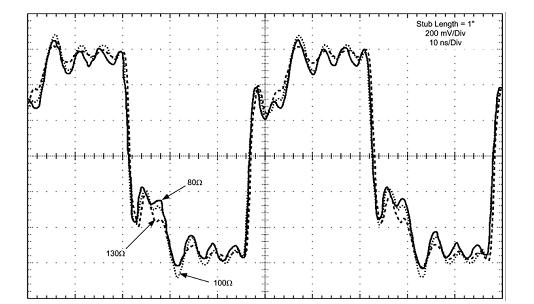

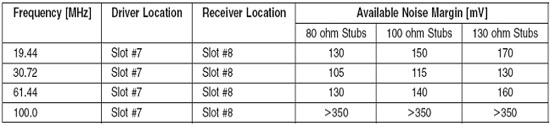

图8给出了当7号槽位中的驱动卡向所有13块接收卡驱动19.44MHz时钟时,信号线分支阻抗对8号槽位中的接收器的有效噪声容限的影响。

图8:阻抗越高的分支线对噪声容限的影响越小

在具有80、100、130Ω信号线分支的三种网络条件下,邻近接收器的输入端测量出的三种波形如图8所示。具有130Ω信号线分支的网络中的接收器存在最高的噪声容限。表5给出了7号槽位中的驱动卡在某些通用频率下向所有十三块接收卡驱动时钟信号时,在8号槽位中的接收器上测量出的噪声容限。

表5:阻抗越高的分支线对噪声容限的影响越小

设计M-LVDS时钟分配网络的技巧和诀窍

设计符合AdvancedTCA标准的M-LVDS时钟分配网络的任务并没有看上去那样简单,如果只依赖于PCIMG3.0标准中所给出的建议的话。下面是用符合AdvancedTCA标准的背板和美国国家半导体的M-LVDS产品进行实验得出的设计建议和诀窍,按照这些建议设计将会有助于建立一个具有最高噪声容限的可靠的时钟分配网络。

1. 选择具有最慢转换时间的M-LVDS驱动器将会满足对时钟系统的带宽要求。TIA/EIA-899标准规定1ns为M-LVDS驱动器输出的最小转换时间。在具有1英寸分支线的AdvancedTCA背板上,1ns的转换时间对某些配置来说太短了。美国国家半导体的M-LVDS驱动器典型的10%~90%转换时间为1.7ns,可以在高达100MHz的频率下工作。

2. 如果其它的系统要求允许,将线卡上的时钟驱动器尽可能靠近背板末端的槽位。这种排列创建较长的信号路径。较长的信号路径损耗也会增大,并丢弃信号边缘信息。此外,当遇到阻抗不连续的情况时较慢的转换时间也使系统表现得更加“宽容”。

3. 尽可能使分支线长度最短。PCIMG3.0标准规定1英寸(包括ADF连接器)为M-LVDS器件的最大分支线长度。更长的分支线会造成系统故障。缩短分支线长度从1英寸至1/2英寸将会增加50%的噪声容限。

4. 当噪声容限非常重要时,应该考虑使分支线的阻抗值最大。这可以通过以下手段实现:增加分支线和铜箔板之间介质的厚度,或者将分支线做到PCB制造商所能实现的最窄值(除了使分支线长度最短以外),或者同时实现上述的两者。

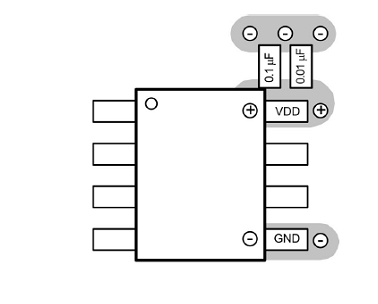

5. 任何电源噪音都能减少有效的噪声容限。确保M-LVDS器件已经正确地去耦。为VDD和GND引脚使用两个过孔,并靠近器件的VDD引脚放置去耦电容。图9显示如何放置去耦电容和连接DS91D176至电源层和地层。

图9:DS91D176的去耦

本文小结

较短并且很窄的分支线结合可控制输出边缘速率的信号驱动器(例如M-LVDS线路驱动器),对增加噪声容限和提高任何多点网络(包括AdvancedTCA背板上的M-LVDS时钟分配网络)的整体性能是至关重要的。牢记这点并遵循本文中给出的PCB设计建议,可以很容易地设计出可靠的时钟分配网络。

作者:

Davor Glisic

美国国家半导体公司