在NAND闪存和DRAM这两个最重要的半导体存储器件市场,三星已稳坐头把交椅,分别占有52.9%和32.1%的份额,相应地是第二名的两倍多和接近两倍。即便如此,该公司也并未被外界看到有丝毫懈怠。三星继续积极采用更先进的工艺来生产其存储器件,这也是该公司得以获得当前强势市场地位的一个法宝。

三星成功的秘诀在于采取积极进取的战略,以尽可能快的速度将最先进的工艺技术用于产品制造。通过快速采用先进工艺技术,三星能以更小的裸片尺寸制造存储器件。因此,每个晶圆能切割出更多的裸片,从而降低了制造成本,其终级好处是使其具有更大的价格灵活性。该战略使三星在存储器行业具有其它厂商目前尚无法复制的竞争优势。

该公司最新的工艺缩微努力的一项例证是一款4Gb NAND闪存,据称这是首款采用65nm节点制造的独立存储器。这款产品的裸片尺寸乃属Semiconductor Insights目前所见到的最小的一个,它使得三星在NAND市场具有成本优势。

在此之前,三星曾制造出第一款90nm DRAM,比其它任何供应商的90nm DRAM都早。三星还将可能是第一家制造80nm DRAM的厂商,当许多竞争对手还在为90nm工艺技术的量产而努力时,三星的80nm DRAM可能已经问世。目前已很清楚,与DRAM相比,NAND闪存产品将更多地采用先进的工艺节点制造。在NAND市场,三星是第一家采用70/73nm节点的厂商,现在又是它率先推出65nm节点产品。东芝和Hynix等NAND对手紧随其后,各自拥有一些技术优势。

创新的工艺技术

三星的65nm 4Gb NAND闪存(K9F4G08U0A)是一款采用每单元单比特SBC(single-bit-per-cell)技术的单片器件。该器件采用三层金属、双多晶(triple-metal, double-poly)的65nm CMOS工艺制造,裸片大小131mm2。其中的单晶体管闪存单元的尺寸约为0.126×0.13μm大小,整个单元面积仅有0.016μm2。总的额定比特效率为31.3Mb/mm2。

这款65nm器件的尺寸比先前采用73nm工艺节点制造的器件小15.9%。但65nm器件的裸片效率是54%,比73nm器件低了约6%。效率的降低可能是由于存储器阵列和外围电路间缩微比例的不一致造成的。

65nm和73nm器件共用了几项创新的工艺技术,它们成功地被从73nm节点移植进65nm节点。这些特性包括自对准浮动栅多晶单元及类似的控制栅和浮动栅结构。但65nm器件还采用了其它几项新的工艺技术,用于处理浮动栅耦合、精选晶体管触点和浅沟道隔离深度等问题。

65nm器件采用SBC技术,每个存储器单元仅存储1比特。SBC技术多年以来一直是标准的闪存技术,它比多层单元(MLC)技术更容易实现、更可靠,且只需要较少的测试时间。但因SBC密度较低,与MLC实现相比,它在成本上处于劣势。

群雄争锋

4Gb容量NAND闪存领域的竞争正变得异常激烈,多家供应商都提供类似的器件。目前,三星的K9F4G08U0A拥有较小的裸片面积,比紧随其后的东芝用90nm节点制造的4Gb器件的裸片面积还小5%。三星以前的4Gb器件不像东芝的90nm MLC器件那样有竞争力,很可能其新的65nm器件就是为了与东芝竞争而快速设计推出的。

三星65nm技术提供的裸片尺寸优势,使其能在一个300mm晶圆上生产出约469块裸片。该数值比东芝的4Gb器件高出6.4%,比Hynix/ST的70nm产品高11.4%。

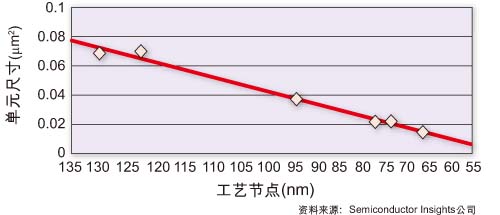

图1:三星在65nm工艺节点保持优势

但三星面临这些公司的激烈竞争。东芝在NAND市场仅位列第二,其策略是采用相对较老的工艺节点用MLC技术制造高比特效率的器件。MLC在每个存储单元内存储两比特信息,所以使得东芝能在给定的硅片面积内存储进更多比特的信息,并可降低给定容量存储器的制造成本。东芝的4Gb器件采用90nm工艺节点制造,拥有29Mb/mm2的比特效率。东芝是首家制造并能以极高比特效率实现单片4Gb器件的公司。目前只有三星的65nm 4Gb器件抢了它的风头。东芝继续其MLC战略,现已推出一款8Gb的70nm MLC器件,是目前容量最大的单片NAND闪存器件。

Hynix和ST是NAND市场的后起之秀,但也很快跻身技术竞赛之列。两家公司合资成立的Hynix/ST最新的4Gb产品是一款70nm的SBC器件,它具有144mm2的裸片大小和28.4%的比特效率,这是一项值得称道的成就,将使Hynix/ST在NAND市场占据有利位置。

裸片尺寸对上表所述的NAND闪存器件的制造成本有直接影响。利用IC Knowledge公司提供的成本模型进行计算,能估算出可用于制造器件的总裸片数量,从而反映出裸片尺寸的统计数据,还显示三星的器件能从每个晶圆中产出比排在第二位的器件多出接近30个裸片。

目前,Semiconductor Insights尚没找到IM Flash和瑞萨科技推出的4Gb产品。IM Flash需提供有竞争力的产品来与位列前三甲的NAND制造商竞争。瑞萨正生产一款90nm的4Gb MLC NAND闪存,但该公司业已声明将不再进行更先进节点的研发。

技术升级挑战

在解决若干升级挑战之后,三星成功地将其闪存技术推进至65nm节点,这些挑战包括:单元对准、沟道氧化物厚度和闪存单元耦合。 现在,三星能集中精力用65nm节点实现MLC器件,以拓展其65nm产品线,并进行55nm节点的开发。为在成本敏感的应用中与东芝的70nm MLC器件竞争,三星需要开发MLC产品。

NAND市场的竞争肯定会更加激烈,制造商需要采用领先的工艺节点制造器件。三星、东芝和Hynix/ST全都处在70nm或更先进的水平,所以,这些制造商将很快转向65或55nm工艺技术。IM Flash只有快速挺进这些节点才能有竞争力。所以,三星不能高枕无忧,它必须快速扩张其产品线并进军55nm节点。

图2:采用55nm工艺的下一代NAND闪存的单元尺寸趋势预测

用55nm节点制造的器件正在开发中,预计于2006年底或2007年初投入生产。它们可能是来自三星、东芝或Hynix/ST的16Gb MLC器件。55nm节点器件的单元大小可能在0.0084μm2左右,最初的裸片大小在140到160μm2之间。这些预测是根据历史的裸片和单元尺寸演进导出的。55nm器件将与先前的65nm和70nm器件有某些共同特性,但需处理一些关键的缩微问题,包括单元对准、沟道氧化、多晶硅层间(interpoly)电介质、相临单元间的耦合(交叉干扰)和高压晶体管设计。

随着器件尺寸越来越小,对模层之间对齐的改进明显地是一个一直需要关注的问题。越小的器件需要的工作电压越低,这种情况又导致在将电荷送往或移开浮动栅时,需更薄的沟道电介质。但薄电介质并不那么可靠。在先进节点,影响单元晶体管浮动栅的活动区域范围更小,但控制与浮动栅的耦合比例需保持恒定。所以需要一种更薄的多晶硅层间电介质。在两种电介质的情况下,高k(介电常数)材料能降低有效电厚度,且同时能够以更宽的物理厚度维持更高的可靠性。

但新材料的引入,将带来新的挑战。将单元封装得越紧,当对一个浮动栅充电时,对相临存储器单元工作产生影响的风险就越大。最终,闪存操作依靠相对高的电压对单元进行编程和擦除。用于切换这些电压的控制晶体管需尽可能保持较小,以便在给定的硅片面积内它们不会降低存储器单元的效率。

三星在市场上率先推出65nm存储器件——K9F4G08U0A。它进一步证明,三星继续致力于用先进工艺节点进行生产,以期在与其它存储器厂商竞争中占有优势。但在成本竞争激烈的存储器市场,仅在工艺节点方面占先是不够的,另外,为在对成本敏感的存储器应用中竞争,还需要诸如MLC编程等电路技术。

现在,三星有了一款能工作的65nm器件,它可能致力于通过增加MLC产品等手段丰富其65nm产品线,并将工艺节点推向55nm。

作者:Geoff MacGillivray

内存分析师

Semiconductor Insights公司