美国初创公司Ambric近日推出了一种用来设计多内核处理器的新方法,并声称采用新方法设计的处理器比当今最优秀的DSP或FPGA的性能还要高出10倍以上。该公司已经开发出了片上通信硬件和一款编程模型,最初将被用于创建标准视频处理器件,并希望在未来能扩展到更多领域。

目前有许多初创公司通过充分利用工艺技术的进步,提供多种面向多内核设计的颇具前途的架构,Ambric公司就属于其中一员。

“多年以来,我们已经拥有包含大量门电路的FPGA模型,你能够以想要的任何方式进行连接,但是我们需要构建更强大的模块来真正最充分地利用硅的价值。”Linley集团首席分析师Linley Gwennap指出。

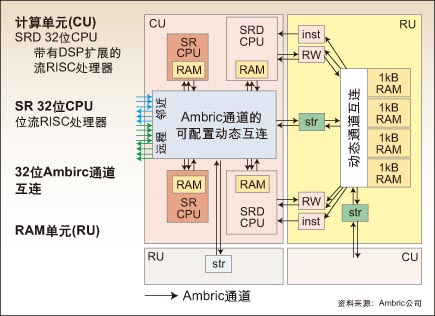

Ambric公司通过推出“bric”提升了自己在行业中的地位。“bric”本身包含了8个位流RISC处理器以及位于内核周围和内部的13kB分布式RAM。该公司采用45个bric创建了一个被称作Kestrel的130nm原型芯片,并宣称该芯片在333MHz工作时,性能超出TI的C641x DSP或赛灵思公司Virtex 4的10倍以上。

Kestrel将包含360个经过简化的32位RISC处理器内核,以及总计4.6Mb的片上RAM。该芯片的目标应用为视频处理,其最大功耗为10W。如果Ambric公司能够在视频应用中立足,他们还希望日后为其它市场推出采用同样技术的产品。

“我们还没有从同FPGA和ASIC激烈的正面交锋中取得突破。”Ambric公司的协创人兼市场和业务开发高级副总裁Jay Eisenlohr说。

“提出一些看上去颇具前途的全新架构,这相对来说比较容易,”Linley的Gwennap表示,“所有新创公司面对的共同难题是:提供客户易于使用的环境和工具。”不过,Ambric公司看来对这个挑战予以了足够重视。

“我们认为首先需要定义合适的软件编程模型,然后再开发支持它的电路。我们正是这样做的。”Ambric公司负责架构的副总裁Mike Butts透露。

在编程模型下,开发人员采用一套Java子集在固定层中创建了一组定义严谨的对象,和一个允许其相互通信的消息机制(messaging scheme)。该Java子集中没有虚拟机、垃圾回收和浮点支持,但是增加了用于处理Ambric独特寄存器硬件的类库。

为了实现Ambric芯片的异步并行执行方式,开发者必须确保对象没有漏定义的依存语法。最后生成的软件通过Ambric的工具被映像到芯片硬件上。

该处理器的杀手锏是Ambric公司的寄存器专有设计,这些寄存器可以进行异步和自动通信。“该寄存器机制从本质上消除了进行同步处理的中央和全局状态机。这些状态机难于设计、验证和测量。”Butts指出。

此外,该方法消除了对时序逼近验证的需要。因此,整体范畴的错误不可能再出现,Butts补充道。

图:用于多内核SoC的Bric架构——Ambric采用独特的异步寄存器电路

在由单独数据和控制线连接的寄存器群基础上,Ambric公司创建了片上通讯“通道”。当一个寄存器可以向邻近寄存器传递数据时,控制线就会自动通知它,这样一来就消除了对时钟同步的需求。数据经过字宽(word-wide)通道流向能缓冲两个字的寄存器。

该公司采用其独特的寄存器机制来构建处理器、bric以及芯片级互连。通道的三层架构可以将位于某个bric、其相邻的bric及远离其的bric上的各单元互相连接。

最终的Kestrel芯片马上就会面市,与目前的FPGA和DSP相比,新器件在相同售价下仅需要1/3的软件,同时却可以提供10-50倍的性能。据Ambric公司称,该架构也能以远远低于竞争对手的价格提供相似的性能。

最初的芯片有望实现60GMAC吞吐量。由于采用了多个分布式内核以及记忆库(memory bank,在软件开发者看来是海量的CPU和内存),该芯片将具有425Gbps的对分(bi-section)带宽。

Butts称,Ambric架构打破了传统的冯·诺依曼式处理架构,创建了以通讯为中心的机制,而新电路恰恰对今天的媒体流和网络中数据包的高速检验等应用更加有效。

Ambric公司在三年前由Jay Eisenlohr和Anthony Mark Jones联合创立,他们先前曾在图形芯片设计公司Rendition共事。“我们明白整个RTL流程有多么困难,Mark是一个非常聪明的人,关于如何处理这个难题他有一些新颖的想法。”Eisenlohr说。

二者从风险投资公司ComVentures那里筹集了1,040万美元的资金,开始着手建立一种方法,并通过片上并行处理进入多内核世界。

“片上网络已经变成目前互连领域最热门的话题之一,但是真正的瓶颈却是这些多内核芯片的输入输出问题。”美国西北太平洋国家实验室(华盛顿)高级研究员兼Hot Interconnects大会联合主席Fabrizio Petrini指出,“Ambric公司可能对不该优化的部分进行了优化。构建高性能片上网络其实并不存在太大的技术困难,目前的主要瓶颈在于同内存的连接。”

对此,Ambric公司的Butts表示,Ambric芯片内部处理进程和存储资源广泛分布的特性意味着,芯片并不是非常需要片外存储器。“存储器访问对我们所考虑的包括视频处理在内的大部分应用来说并不是问题。”他说。

作者:麦利