OPTION_5:HP

美国加州圣巴巴拉大学(UC Santa Barbara)和莱斯大学(Rice University)的工程研究人员发现,采用二硫化钼(MoS2)单原子层作为通道的晶体管设计,可望展现比最先进的硅晶体管更低至0.1V的切换电压,而且还可降低高达90%的功耗。

这项研究已发表于最近一期的《自然》(Nature)期刊中。

UC Santa Barbara电子与计算机工程教授Kaustav Banerjee表示,晶体管导通的陡度特点是一种被称为次阈值摆幅的参数,该参数在MOSFET时不能被降低到低于一定值。对于陡度为 60mV/decade的MOSFET,通常会是数字电路总体能效的有效限制。

为了解决这些硅晶问题,研究团队所打造的晶体管以锗作为源级,并以能够实现频段对频段穿隧的MoS2作为通道。该穿隧场效晶体管(TFET)拥有不到60mV/decade陡度的次阈值摆幅。

源极到通道的设计目的在于滤掉高能量电子,否则可能使其穿越源极/通道能量阻障层,甚至到达关断状态。研究人员表示,透过该设计保持关断电流可被忽略不计。

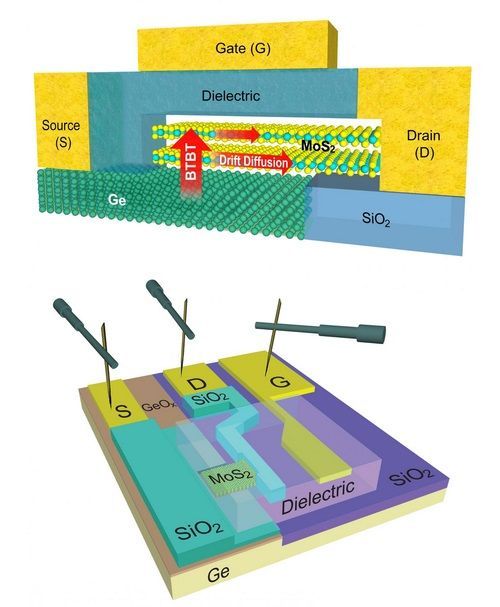

根 据UC Santa Barbara研究人员Jiahao Kang解释,如图中上图是ATLAS-TFET的横截面视图,显示锗源极/基板、MoS2通道以及频带间(band-to-band)穿隧方向。下图则 是制造组件的视图,显示锗源极/基板、原生GeOx层、MoS2通道以及其上的闸电介质。值得注意的是,源极与汲极的部份以及在MoS2周围的锗基板完全被电介质(SiO2)覆盖,以避免影响闸电极。

在UC Santa Barbara,Banerjee的纳米电子研究实验室(Nanoelectronics Research Lab)中还包括Deblina Sarkar、Xuejun Xie、Wei Liu、Wei Cao、Jiahao Kang与Stephan Kraemer,以及莱斯大学的Yongji Gong与Pulickel Ajayan均参与了这项研究。

该途径更优于使用硅或III-V族化合物半导体作为通道材料的TFET,因为TFET所使用的这些材料表面状态的密度较高,从而提高了漏电流。该论文则指出了一种在室温下达到最高30mV/decade的次阈值摆幅。

英国曼彻斯特大学(University of Manchester)物理学教授Konstantin Novoselov表示,“业界一直到最近才开始在穿隧晶体管中使用2D材料,而该研究更为这一领域带来进一步提升这种组件性能的强大推动力。” Konstantin Novoselov由于“在石墨烯材料的新发现”而在2010年成为诺贝尔物理奖的共同得主之一。

编译:Susan Hong

本文授权编译自EE Times,版权所有,谢绝转载