OPTION_5:HP

数据中心、广播、固网和高性能计算等系统要处理的数据量不断攀升,需要的带宽非常高。为此,Altera公司于近日首度公开了其集成SK Hynix堆叠宽带存储器(HBM2, High-Bandwidth Memory)和高性能Stratix 10 FPGA/SoC的“业界第一款异构系统级封装(SiP)器件”—Stratix 10 DRAM SiP。

“Altera是将这种突破性3D堆叠存储器技术和FPGA集成在一起的第一家公司。”Altera公司产品营销资深总监Patrick Dorsey说,SoC FPGA已经进入4核、16核时代,集成有500多万个逻辑单元,DSP的浮点运算能力达到了10T FLOPS,但目前面临的一个关键问题是:由于受制于存储器带宽,这些数据无法快速传输到核心处理单元。

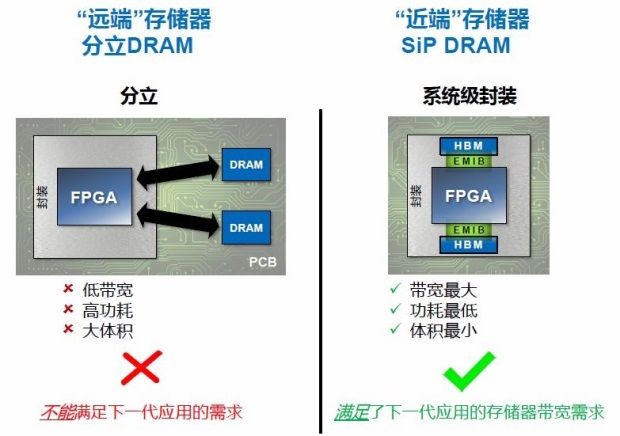

他认为新推出的Stratix 10 DRAM SiP代表了新一类器件,其特殊的体系结构设计能够实现10倍于目前的分立DRAM存储器方案,满足了下一代高性能系统对存储器带宽最严格的要求,是一个蛙跳式的进步。

SiP DRAM满足了下一代应用的存储器带宽需求

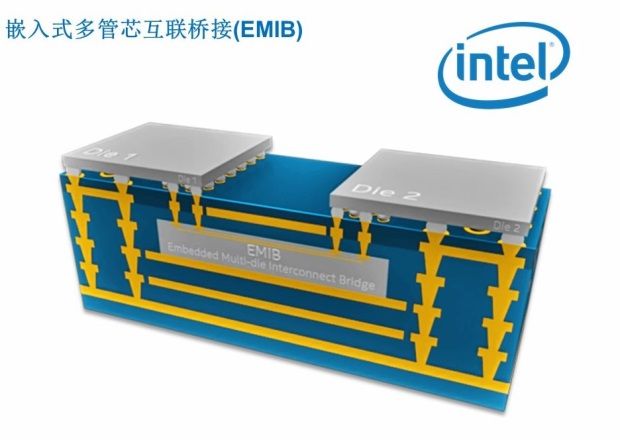

Intel嵌入式多管芯互联桥接(EMIB,Embedded Multi-Die Interconnect Bridge)技术是Stratix 10 DRAM SiP得以问世的关键。该技术采用高性能、高密度硅片短桥接在单个封装中将多个管芯连接起来,管芯之间走线非常短,能够支持Altera以高性价比方式在异构SiP中集成HBM2,让DRAM存储器尽可能靠近FPGA管芯进行封装,从而缩短了走线长度,并以最低功耗实现最大存储器带宽。

Intel嵌入式多管芯互联桥接(EMIB)技术

Patrick表示这种设计思路的优势在于单片内核架构避免了使用多个FPGA管芯来提高密度的连接问题,协议与协议之间的连接、I/O之间的连接不存在任何问题,从而进一步提高了性能,降低了复杂度和成本,增强了信号完整性。例如,使用异构3D SiP集成技术为Stratix 10器件提供了途径来实现更高的收发器速率(56Gbps)、新出现的调制格式(PAM-4)、通信标准(PCIe Gen4、多端口以太网),以及模拟和宽带存储器等其他功能。

Stratix 10今后会陆续集成新的功能模块

出于技术和商业方面的考虑,Patrick并没有透露公司下一步的产品计划,只表示仍在“持续探索中”。例如集成定制化ASIC功能,首先要考虑客户的业务量是不是足够大。因为定制化产品和标准化产品的商业模式是完全不同的;如果集成DAC/ADC和其它模拟芯片,就要考虑器件选型、系统级功耗优化等技术问题,不会一蹴而就。

其实如果不采用EMIB技术,直通硅片过孔(TSV)技术也可以实现上述目的。但在Patrick看来,EMIB提升的是系统性能,而采用TSV技术将FPGA与外部器件相连,由于更多内部连线,封装上更多金属物质的存在,会使系统在信号完整性、性能和功耗等方面大打折扣,这对于机器学习、大数据分析、图像识别、工作负载加速和8K视频处理等高存储器带宽需求的应用来说,是极为不利的。

高性能应用推动了业界对HBM2 DRAM技术的需求。SK Hynix美国技术营销副总裁Kevin Widmer说HBM2的性能达到了每秒256GB带宽,每比特功耗降低66%,这在以前是不可想象的。目前,集成在FPGA中的DRAM容量从4GB-16GB不等,Patrick表示此举只是将足够用的内存集成在FPGA中,目的在于实现最高达1TB/S的最大传输带宽, 如果还需要更多的存储,完全可以接入到更大的系统级存储。

SiP与DRAM解决了很多应用中遇到的存储器带宽难题

客户现在可以使用快速前向编译性能评估工具启动其Stratix 10设计。Altera将于2016年开始发售Stratix 10 FPGA和SoC,于2017年开始发售Stratix 10 DRAM SiP产品。

本文为《电子工程专辑》原创,版权所有,转载请注明出处并附链接