OPTION_5:HP

最近在葡萄牙孔迪镇聚集了一大群IC封装与半导体工艺处理专家,他们正在参加由欧洲最大的外包半导体装配与测试服务(OSATS)提供商Nanium S.A.公司在其总部主持召开的2015年半导体封装技术交流大会,会议最后日程是主旨演讲和参观代工厂。

这次会议讨论的焦点是大尺寸的扇出型(扩散型)封装,或在良率和封装成本压力下,OSATS提供商感到从扇出型晶圆级封装(FO-WLP)向扇出型面板级封装(FOPLP)转变的必要性。

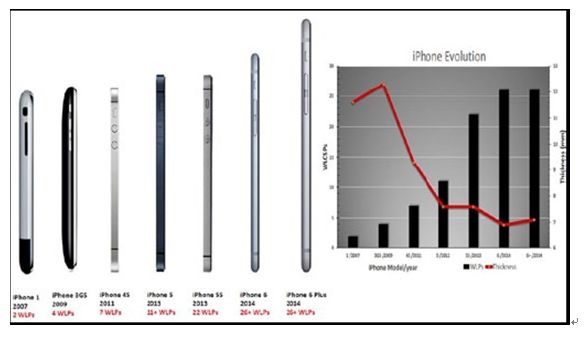

首先强调的是FO-WLP的市场驱动力,TechSearch International公司总裁E.JanVardaman指出一年年的移动设备如何通过增加晶圆级封装数量充实其电路而变得越来越薄。她用七代iPhone手机作了形象的描述,这些手机从约12mm变到7mm,同时它们的WLP容量从2个裸片增加到超过26个裸片。

图1:iPhone趋势:WLP数量越来越多。来源TechSearch International

Vardaman指出,传统的WLP趋势包括越来越多的I/O数量和越来越大的裸片。伴随着不断缩小的几何尺寸,每个裸片的I/O数量近年来有了显著增加,从几十个一下增加到了400多个,因此需要采用多裸片封装,或转向更大的FO-WLP封装,这样I/O不仅可以分布在裸片下方,还可以分布在封装四周(像围绕裸片的额外边际空间)。

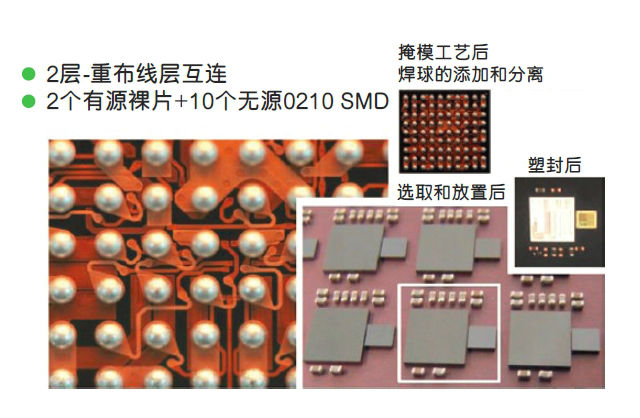

一般情况下,FO-WLP受益于同样的纤薄厚度(不到0.4mm),但可以集成来自不同技术节点的多个裸片以及一些无源器件。Nanium提供了一个很好的例子,即在一个9mm×8mm封装中将2个有源裸片和10个表贴无源器件塑封在一起。

图2:集成了无源器件的Nanium公司多裸片扇出封装。

本文下一页:市场需要更低成本的封装形式

{pagination}

市场需要更低成本的封装形式

据TechSearch预测,到2019年,FO-WLP年出货量可以达到18亿个以上,相比2014年还不到3亿个。但如果趋势持续的话,重构晶圆上的实际面积将成为最优化的更大的封装集成和成本效益的限制因素,因为元器件数量仍然是有限的,甚至在类似晶圆的基板上(随着封装的增长)有所减少。

最终产品平均售价的降低带来的进一步价格压力迫使OSATS提供商开发出更低成本的封装品种,并转向超过目前晶圆尺寸的大面积封装。“这是晶圆代工厂、后端装配和PCB细分市场合并的切合点。”Vardaman表示。

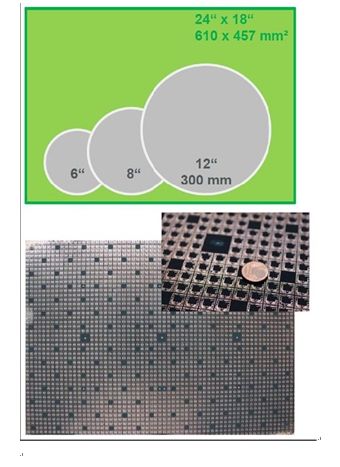

借助引用的几个高达610×457mm2的面板尺寸FO-WLP研发例子,Vardaman判断,基于面板尺寸的工艺具有光明的前景,尽管它也会带来许多技术方面的挑战。这些挑战包括大面板操作(新的基础设施将裸片从晶圆级工艺机器转移到更大的具有面板处理能力的设备)、大面板上裸片的布放精度、面板翘曲和新的扩散工艺等等,以达到足够的模塑均匀性和平坦性。

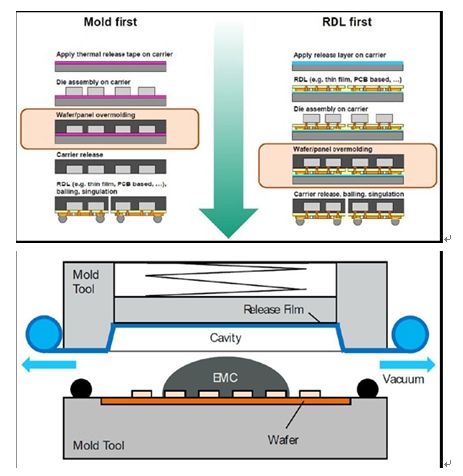

Fraunhofer IZM公司提出的一些解决方案围绕着所谓的压缩模塑展开,使用模具第一方法或再分配层第一方法。原理上看起来相当简单。一滴封装化合物被泼到重构晶圆上,然后用面板模具在真空和一定温度条件下进行压缩,直到填满裸片之间的所有空隙。

图3:Fraunhofer IZM的模塑工艺,依赖于Apic Yamada的LPM-600人工(半自动)模塑系统(适合面积达670×620mm?的面板)。

Fraunhofer IZM公司负责装配和封装的副经理Tanja Braun介绍了液体、颗粒和薄片层压模塑化合物的比较结果。虽然像粘合剂一样的液体化合物可能要求复杂的扩散图案来优化流动性能,但颗粒型材料展示了最有前景的结果,因为它在压缩过程中的熔化之前,它可以几乎均匀地分布在整个腔体内。而且它是最经济的,对大面积来说没有扩散限制(也比粘合剂扩散得更快)。

在均匀扩散过程中,被调查的颗粒材料不会受到液体化合物产生的流动标志和编织线的影响(与被调查的众多扩散图案无关)。于是实验室继续在610×457mm2面板上用450μm的模具厚度模塑250μm的薄裸片,得出的结论是:虽然FO-PLP是可行的,但从WL到PL没有简单的升级途径,新材料在被批量采纳之前必须与新工艺联合起来开发。不过研究工作很快能得到回报,因为转向大型FO-PLP可能会使封装成本降低约20%至30%,该研究人员指出。

图4:在610×457mm2面板上的Fraunhofer IZM公司FO-PLP结果。

本文下一页:业界对FO-PLP路线发展反应不一

{pagination}

业界对FO-PLP路线发展反应不一

Rudolph Technologies公司的蚀刻系统部应用经理Roger McCleary对FO-PLP路线图比较乐观,并暗示他的公司最早将于2016年开始支持大面板的预生产,并在2017年之前在再分配层蚀刻、处理超过5mm翘曲所必要的方法和补偿措施方面作好完整生产设备的准备。

“在半导体后端行业中还看不清长期前景,但我们认为扇出型封装将显著增长。”他表示,并补充道,随着封装的变大,他们将减少传统晶圆上的元器件数量,并推动制造商转向更大的基板,以便实现更低的封装成本。

McCleary期待公司的第三代Jet-Step蚀刻设备能够处理面积达650×550mm (5倍于300mm晶圆面积)的面板,并使产能与Stepper设备上的300mm晶圆处理相比有2倍的增长。他引用了一个估计的吞吐量——每小时107,113个裸片,相比目前每小时只有42,504个裸片。

SPTS公司PVD生产管理经理Chris Jones对FO-PLP则没有那么乐观。

“高带宽封装中的2.5D和3D裸片集成正在进行中,但何时能够有更广阔的市场?”他问,“关键在于成本,那么FO-WLP可以填补这个空隙吗?”

Jones透露为了处理200、300和330mm晶圆而在公司的Sigma fxP PVD系统上做的一些修改,但他热心地指出了面板级封装的分辨率和翘曲问题。

最后一位演讲者是SUSS MicroTec公司产品管理激光工艺处理总监Kevin Yang,他介绍了使用紫外线蚀刻和准分子激光烧蚀的大尺寸刻制解决方案。

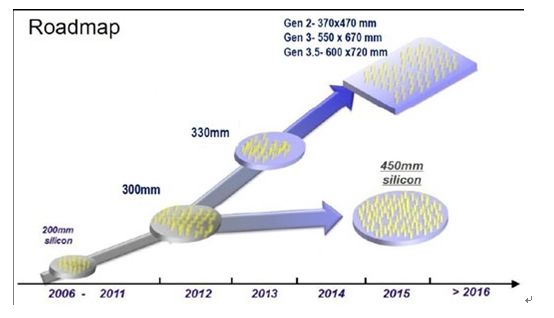

他承认,虽然所有平台可能共存,但450mm晶圆的采纳非常缓慢,这可能使得基于面板的封装变成发展更加快速的替代技术,以便降低封装成本。尽管如此,他还是提出了面板标准和基础设施方面的一些问题,什么尺寸、什么材料、什么工艺和设备?

然后他详细介绍了使用该公司的ELP600实现的规格和满意结果。ELP600是一个房间大小的准分子烧蚀系统,能够处理大到600mm×600mm的基板。

图5:一种可能的FO-WLP路线图。

Source:Yole Développement

本文为《电子工程专辑》原创,版权所有,谢绝转载