OPTION_5:HP

特殊应用IC (ASIC)往往会因为它们能透过芯片外接之DDR内存可达成的带宽而受限,不过ASIC供货商Open-Silicon声称他们透过以3D芯片堆栈方式克服了上述困难,将ASIC与高带宽内存(HBM)以1,024位并行储存器接口整合在系统级封装(SiP)中, 使其产品性能超越任何一种外接内存架构。

“我们可提供以硅中介层2.5D技术与ASIC封装整合的3D内存堆栈,”Open-Silicon硅知识产权暨工程部门(IP and Engineering Operations)副总裁Hans Bouwmeester接受EE Times美国版编辑独家专访时表示:“结果能带来更高的性能、更低的功耗以及更小的组件尺寸,这是一种三赢的方式。”

利用Open-Silicon 的HBM SiP解决方案,ASIC能改善对内存的存取──特别是与DDR4相较;该方案包括必要的IP以及兼容JEDEC标准的HBM内存,以3D堆栈方式整合。

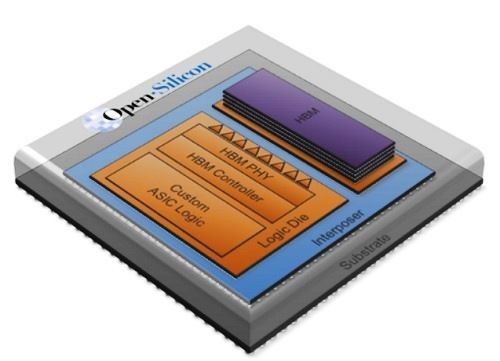

Open Silicon 的高带宽内存,以3D系统级封装为ASIC整合1,024位宽度内存路径

Source:Open Silicon

Open Silicon是采用支持1,024位平行路径的中介层,让内存与ASIC能在带宽上紧密连结,就如同竞争方案是把内存放在ASIC芯片上;但后者可能会带来较高昂的成本,以及较低的良率。

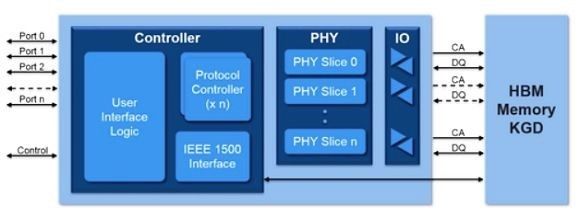

Open Silicon 的高带宽内存IP子系统功能区块,显示堆栈的KGD (Known Good Dies)接口是如何与内建IEEE 1500测试接口的ASIC整合

Source:Open Silicon

Bouwmeester 表示,该方案达到高良率的原因是:“我们只会在SiP内中介层上放置预测试过的已知良品ASIC,以及预测试过的已知良品3D HBM内存裸晶,因此良率非常高。”客户能使用他们自己的客制化逻辑IC,Open-Silicon则可提供各种能让ASIC与兼容JEDEC标准 HBM内存芯片结合的HBM IP。

大多数Open-Silicon的客户在带宽与性能上受到限制的系统,是运用于高性能运算、网络,以及高阶消费性或绘图应用;该公司表示,这些客户将能因HBM ASIC SiP方案而受惠。

编译:Judith Cheng

本文授权编译自EE Times,版权所有,谢绝转载