OPTION_5:HP

韩国内存芯片制造商海力士(SK Hynix)在2014年初发布其高带宽内存(HBM)产品,并宣称是全球首款采用2Gb、20nm节点制造的8Gb DDR4 SDRAM模块。最近,该公司在历经将近一年的时间后,总算让这款HBM模块出现在下游产品中——AMD Radeon 390X Fury显卡。

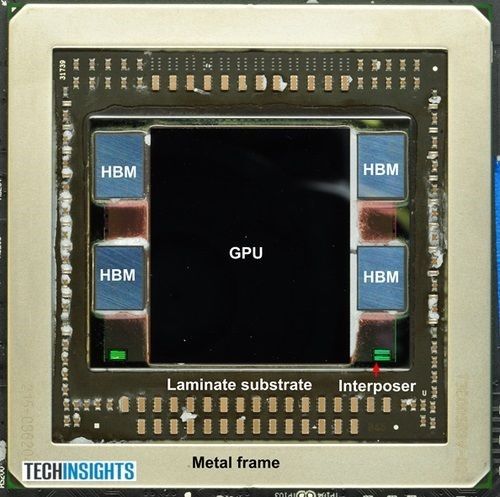

AMD 近日推出其Radeon R9 Fury X系列图形处理器(GPU),配备了海力士的4GB高带宽HBM。在TechInsights的实验室中刚好就有几款这样的Fury X显卡,其GPU如图1所示。在该模块正中央看到的是GPU芯片,四周围绕着4个海力士HBM内存模块。该GPU与HBM模块采用覆晶封装连接至联电 (UMC)制造的中介层,再连接至层迭的基板。中间这一大块GPU的尺寸为23mm x 27mm,据信是采用了台积电(TSMC)的28nm高介电金属闸极(HKMG)工艺制造。之前《电子工程专辑》发表过分析HBM文章的上部,分析了该款显卡对HBM的应用,请点击这里查看《拆解揭密海力士高带宽内存封装》

该HBM利用硅穿孔(TSV)技 术与中介层,实现比GDDR5 DRAM更高的带宽、更佳电源效率以及更小的表面积。利用TSV方式连接DRAM芯片与基础逻辑芯片,这对DRAM来说还是相当新的技术。三星 (Samsung)的20nm DDR4虽然也利用TSV连接4个堆栈DRAM芯片,但它并不是宽I/O(Wide I/O)组件,也不包含基础逻辑芯片。海力士的HBM拥有1,024位宽的总线,可实现128GB/s的性能,并足以显示它是Wide I/O。该组件利用基础逻辑芯片作为接口,连接4个DRAM芯片堆栈以及一个支持HBM模块与AMD GPU的中介层。该HBM可视为3D封装,而两旁中介层上间隔布局的GPU与HBM模块则形成2.5D封装。

图1:采用海力士HBM内存的AMD Fiji GPU

Source:TechInsights

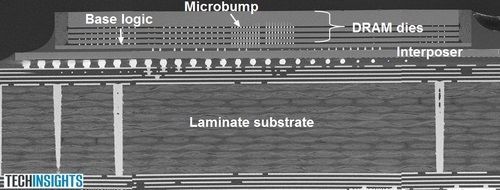

图 2是海力士HBM模块的扫描式电子显微镜(SEM)横截面,显示其中的4个SRAM芯片、基础逻辑芯片、AMD中介层以及层迭基板。底部三个DRAM芯片已经被削薄了,而顶部的DRAM芯片仍相当厚。顶部的DRAM芯片较厚应该是刻意设计的特点,可能用于为HBM模块增加机械刚度。而微凸块结构则将芯片连接在一起,并连至中介层。

图2:海力士HBM内存

Source:TechInsights

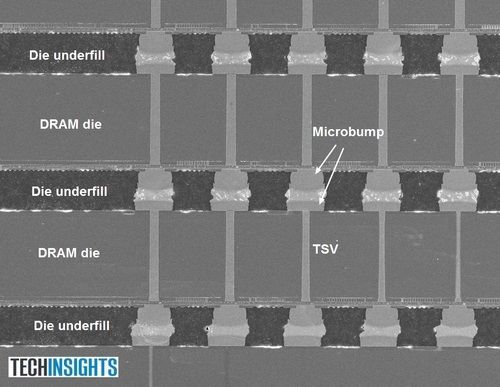

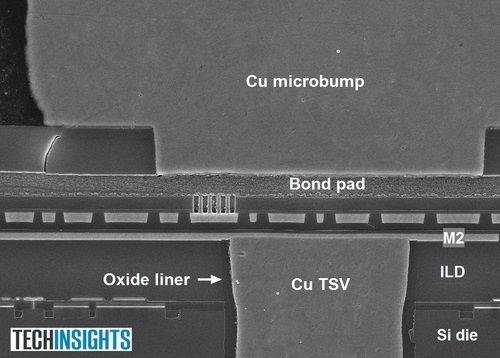

TSV 用于连接堆栈的DRAM芯片,如图3和图4中段钻孔(via middle)工艺用于形成TSV,而晶圆在前段(FEOL)工艺中制造出晶体管、触点以及金属前电介质。反应性离子蚀刻可能用于制造TSV开口,这些过孔都是微小的圆锥形,靠近主动电路的过孔顶部比底部稍宽大些。

图3:堆栈的DRAM芯片与TSV技术

Source:TechInsights

本文下一页:早期利用Bosch TSV蚀刻,现在已经取得了更好的蚀刻配方

{pagination}

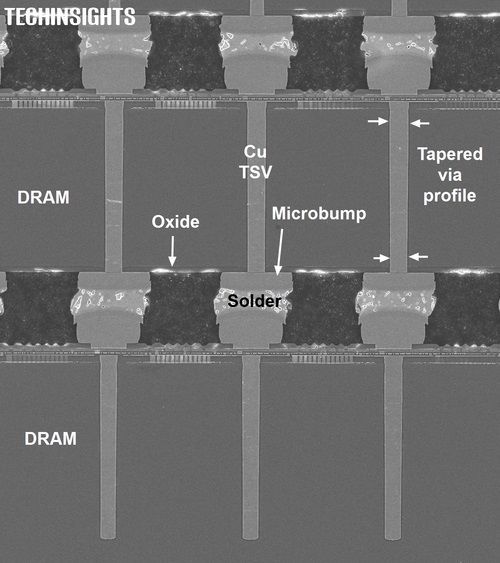

从图4可看到TSV底部接触到铜微凸块,而过孔顶部则接触DRAM芯片的铜互连。

如图2所示,最上面的DRAM芯片还包含了TSV,而这些都可以在图4底部DRAM芯片中看到。图4已经被反转了,因此,主动电路被放在顶部。底部芯片的过孔可渗透约50um深至硅基板,显示从芯片的顶部执行过孔蚀刻。TSV的顶部位于芯片焊垫下方,显示过孔开口是在后段(BEOL)工艺中制造的。

海力士分别在 2013年电子组件暨技术会议(ECTC 2013)以及2014年VLSI技术会议中发表研究报告,披露其HBM的中段钻孔工艺。利用Bosch TSV蚀刻,在钨触点连接至闸极与源极/汲极区制造后形成TSV开口。随后,氧化层沿着过孔侧壁沈积、衬盖钽(Ta)基阻障层与铜(Cu)晶种层后,再以电镀铜填充。热退火工艺用于释放铜应力;而化学机械研磨(CMP)与蚀刻工艺用于削薄DRAM晶圆背侧,从而暴露出铜TSV。然后再以氧钝化DRAM晶圆背侧,接着在背面形成微凸块。

预计还会看到一般采用Bosch蚀刻的扇形过孔侧壁,海力士表示扇形直径必须维持小于30nm。不过,一开始的过孔SEM横截面并未如预期地出现Bosch扇形,显示海力士目前已经取得了更好的蚀刻配方了。

图4:TSV以及微凸块

Source:TechInsights

图5显示TSV顶部以及一部份的DRAM金属互连。图中可看到TSV过孔穿透硅芯片以及覆盖层间电介质(ILD),并截止于铜金属2(M2)线底面。藉由氧化物从过孔开口线性扩展至ILD,确认这一中段钻孔工艺。

图5:TSV顶部

Source:TechInsights

本文下一页:DRAM芯片上的2000多个TSV焊垫有什么作用?

{pagination}

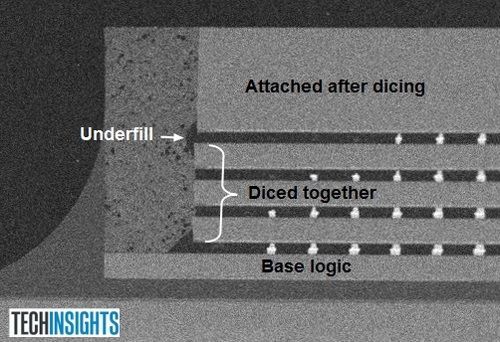

堆迭DRAM芯片与中介层似乎并不容易,但海力士在2015年的研究报告(JSSC,2015)中已经暗示如何完成了——根据该公司描述,“在晶圆上堆栈芯片、翻转与测试”。图6显示HBM模块中的芯片两端,我们可以看到芯片底部填充越过DRAM芯片底部并从DRAM芯片最顶部延伸出来。中间三款芯片两端几乎共平面,而其底部填充末端则是芯片边缘。

这显示三个底部芯片在晶圆级时堆栈在一起,然后再切割为同一组。最顶部的芯片厚度约为三款较底层芯片的2倍,而且可能在连接至DRAM堆栈以前即进行切割与测试。我们猜测4款芯片堆栈后再连接至基础逻辑芯片。

图6:HBM封装截面图

Source:TechInsights

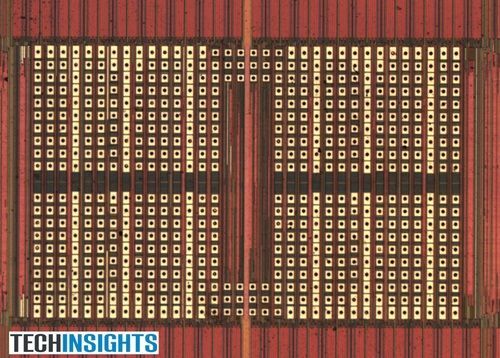

TechInsights估计在每一个DRAM芯片上大约有近2,100个TSV焊垫,如图7所示。其中更大一部份将用于电源、接地、寻址、数据I/O以及冗余,其他几个则用于作为测试TSV的控制信号。

图7:DRAM芯片TSV焊垫

Source:TechInsights

海力士在先前发表的两篇论文(JSSC 2015以及IEEE SSCC 2014)中分别讨论了对于HBM的测试策略。根据我自己对于论文的理解,我认为每一个DRAM芯片都有自已的TSV选择电路、电流源以及电子熔丝(e- Fuse)结构,而基础逻辑芯片包括用于选择个别TSV与测量其电子阻抗的测试电路。

由于每一款芯片都有自己的电子熔丝,我们预期海力士利用了电子熔丝阻断单芯片上的损坏TSV,并从一组冗余的TSV中取得好的TSV加以取代。这避免了在只有一个TSV损坏时还得完全阻断TSV垂直堆栈的必要,并进一步减少了所需冗余过孔的数目。

这 种方式十分聪明,为了了解其运作原理,我现在还在拜读该公司Dong Uk Lee等人在JSSC 2015所发表的论文——“A 1.2V 8Gb 8-Channel 128GB/s High-Bandwidth Memory(HBM) Stacked DRAM With Effective I/O Test Circuits”。 另一方面也要向海力士致敬,因为这家公司推出了全球首款高带宽内存。

编译:Susan Hong

本文授权编译自EE Times,版权所有,谢绝转载