上周参加euroasiaPRESS 1:1在硅谷的媒体活动,密集拜访了10余家半导体公司,其中包括有已跻身“亿美金俱乐部”的大公司、也有刚成立几年的小型初创公司,还有是因为和客户保密协议等原因之前没有进行过公开媒体宣传的“隐形”私有公司,本篇报道涉及的是两家比较小的公司,一家EDA公司与一家IP公司。

Calypto:专注HLS与低功耗RTL设计

Calypto是家成立于2002年的EDA公司,早先以自己的SLEC和PowerPro为业内小众设计者熟知,后来被更多中国工程师被动接受是在2011年收购Mentor的Catapult HLS产品线之后。

但总体而言Calypto在中国的整体市场接受度还并不算大,其总部在美国圣何塞,在美国和印度设有研发中心,年初在韩国设立办公室来支持韩国客户,目前在中国的业务主要通过奥肯思代理。

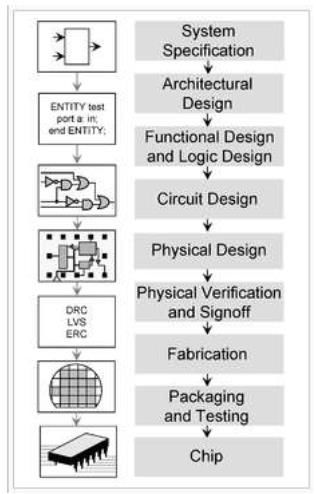

先上一张IC设计的流程图给大家个概念,在整个设计流程中,Calypto的工具主要是在功能和逻辑设计这部分,另外也包括一点点的架构设计。

在EDA行业高度整合的今天,我第一个疑问就是这种专注于设计特定阶段的软件被工程师的接纳难度,在回答这个问题时,该公司营销副总裁Mark Milligan表示,“现在业界在每一个设计环节都分的很清楚了,不同设计环节通常也是由不同的设计团队来完成的,且不同设计环节之间都有非常标准的接口。所以根本不用担心会影响和其他设计步骤的连接。”他强调Calypto的设计能很容易的导入到其他EDA厂商的后续电路设计步骤。

第4页:Arteris:新插件瞄准safety和security两种安全需求

{pagination}

两大设计平台助力速度与功耗

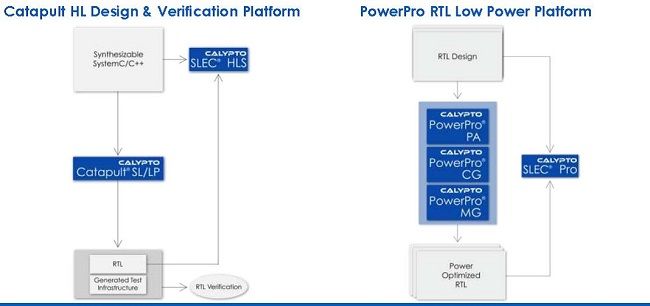

Calypto的平台包括Catapult HL设计和验证平台,以及PowerPro RTL低功耗平台。

“设计者可以先采用Catapult,综合用c++或SystemC语言的硬件描述到RTL,且不需要专有标准;之后我们的SLEC能精确验证 c++ / SystemC和RTL(SLEC HLS)之间的等效性。Milligan指出,“而竞争对手的软件则需要重新运行逻辑仿真。”

完成上述步骤之后,可以将设计好的结果再通过PowerPro来进行功耗优化。对于降低功耗,Calypto的PowerPro平台包括了多个针对性工具:

PowerPro PA用于RTL功率估算和结果分析;

PowerPro CG用于逻辑、寄存器和时钟树;

PowerPro MG用于存储;

“每一个模块都有他自己的存储器50%的设计是跟Memory有关的,通过开关Memory来优化功耗;”Milligan指出了存储器功耗优化的重要性,“另外的50%属于一些功能上的设计和创新,才是工程师需要差异化自己产品的地方。”

“与竞争对手Cadence的工具相比,他们只能支持c语言,而不能支持SystemC或C++;其次是在仿真方面的优势。” Milligan笑言,“而且我们还在不断开发新的优势。”

第4页:Arteris:新插件瞄准safety和security两种安全需求

{pagination}

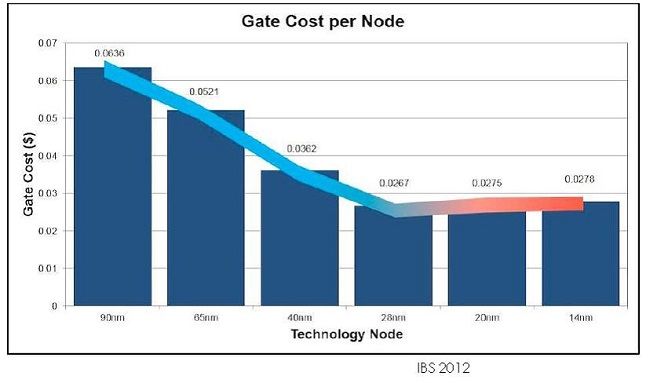

28nm门成本拐点后的HLS和微架构需求

在28nm以上时,可以通过采用更低节点工艺来获取更低的门成本,但28nm是门成本的拐点,在这之后的节点并没有在降低门成本方面取得进展,所以一些设计团队还会停留在28nm,但同时又必须在面积,性能和功耗方面得到优化,这个时候,掌握HLS以及最佳的微架构才是往前发展的正解。

目前转移到Catapult的新应用包括视频(H.264、HEVC、VP9)、4K/Ultra HD图像处理、通信(4G、802.11、Gb Optical)等。一个已有的使用案例包括谷歌通过采用Catapult设计其VP9减少了一半的设计时间

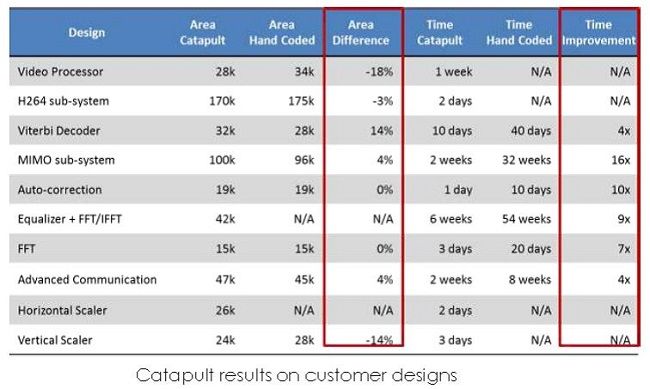

下面这张图表显示了Catapult的QoR和减少的RTL设计时间,案例选用的是某知名厂商的手机芯片组。

FinFet工艺被认为是改变了功耗的游戏规则,因为其漏电流非常低,但不幸的是动态功耗却急剧增加,可靠性高。“目前在14nm及以下就只能采用FinFet工艺了,此时随着工艺节点的缩小,泄露功耗变小,但动态功耗急剧上升。”

Milligan很看好在中国的市场推广,除了工具性能方面的优势外,他认为“美国的工程师年纪都较大,相对比较顽固,他们接受新事物的难度大,而中国工程师年轻又活力,对新工具的接受速度很快!”

第4页:Arteris:新插件瞄准safety和security两种安全需求

{pagination}

Arteris:新插件瞄准safety和security两种安全需求

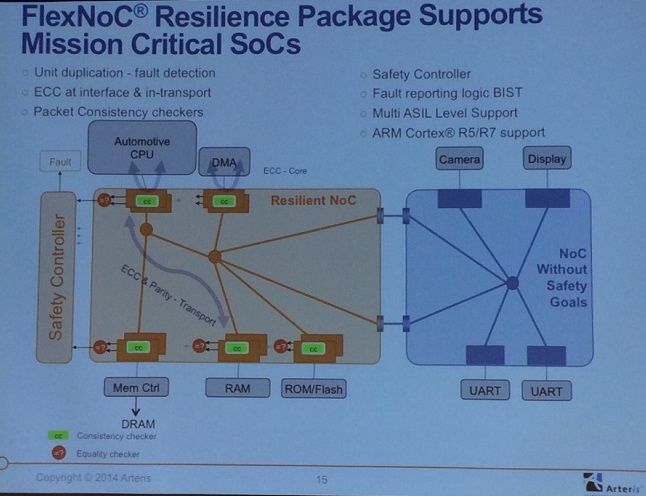

Arteris比Calypto的成立时间晚了一年,专注于提供网络芯片(Network-on-Chip)互连IP和工具,此次主要是推出其新产品FlexNoC Resilience Package,目的是为了提高可靠性,并降低SoC的开发成本,把公司的FlexNoC网络芯片架构IP推向需要容错性(fault tolerance)的汽车、航空航天、工业设备等电子领域。

“FlexNoC Resilience Package是我们FlexNoC的一个可选插件,是我们特别针对系统安全需求高的应用推出的产品。”Arteris公司营销副总裁Kurt Shuler表示。

Resilience的意思是在遇到故障和挑战时,向正常运行的器件提供和保持一个可接受的服务等级,由于我暂时找不到一个合适的中文词语来表达这个词的意思,所以后文暂时对这个词沿用英文。

“Resilience已成为多任务关键系统的一项必须的要求,一些标准已经明确指出对整个系统、包括半导体的安全性的需求,比如‘电气/电子/可编程电子安全相关系统的功能安全’的IEC61508、在汽车领域的ISO26262、医疗领域的IEC60601、工厂自动化领域的EN62601、航空航天领域的RTA/DO178B等。”Shuler表示。

FlexNoC Resilience Package的在满足汽车标准方面,在ASIL B级,支持CortexR5/R7接口,提供用户定义的数据负载保护/修正;数据包传输保护;数据包一致性检查。在ASIL C和D级还额外再增加逻辑重复与内置式自我测试(BIST)。

Arteris宣称是能提供CortexR5/R7处理器端口检测提供内置支持的第一家且唯一一家商业化互连架构IP厂商,拥有独特的先进技术包括单元重复和比较、客户传输保护、数据包有效性监测、事务超时(transaction timeout)、BIST和故障控制等,但在被问及公司在专利方面的情况时,Shuler表示公司目前没有什么专利。

对于这个令我稍微有点吃惊的回答,他指出,“美国其实抄袭也是很多的,但是专利也是一个只有大的公司他能够负得起那个专利,专利保护需要时间需要花时间投入金钱来去做这些事情虽小的公司很难做到这些,而同时做到技术领先才是重要。”

{pagination}

收购影响

去年11月高通收购Arteris后对公司的影响一直是业界关注的话题,网络上一直没有什么资料曝光详情或详关新闻稿件。相信很多人好奇这桩收购案对于其其它客户的影响,私下里有机会我问到了Shuler这个问题,他透露,“公司在被高通收购前就已经和其他的客户比如说TI,三星等达成了协议,所以对于高通的收购并没有影响之后的合作情况。”

“收购是一个双赢的事情,投资者得到了自己非常好的回报,员工也因为持有内部股票而得到一个非常好的回报,且在整个过程中没有裁员行为。”他表示,“现在我们无论是财务还是运营都是独立分开的,所以并没有受到影响。我们在2014年的客户采纳已达到63家。”

至少看到的情况是这样的,此次媒体活动从头至尾没有看到任何高通的影子。

《电子工程专辑》网站版权所有,谢绝转载