作者:Zvi Or-Bach,MonolithIC 3D有限公司

Rick Merritt在Semicon West发表的一文中写道:“摩尔定律明显降速了。”他援引Gartner公司半导体分析师Bob Johnson的话说,“不管Intel说什么,摩尔定律确实在降速。只有一些大批量高性能应用才能证明20nm及以下工艺摩尔定律仍然适用。”

不久以后,在ConFab 2014的一篇《半导体制造与设计》的博客中,Peter Singer引用IBM公司半导体研发中心副总裁Gary Patton博士的话说,“我们现在面临的挑战是双重的。首先,我们正在努力实现0.7倍线性缩放,也可能是0.8倍。其次,我们正在增加更多的复杂性,特别是当你增加双重和三重图案工艺时。”

在更近的8月初,我们终于从Intel公司获得了该公司即将推出的14nm工艺技术节点的更多信息。在我们的《Intel对Intel》博文中明确指出,Intel的数字表明摩尔定律在28/22nm节点停止了,而且同时表现在要求的培育时间和新技术节点的成本方面。

很难接受一个保持了50年、在多次预测即将终止后的许多年中仍顽强保持前行的趋势真的停止了。当我们看到在培育14nm和10nm节点方面付出的巨大努力时更加让人难以接受。现在每个人似乎都应该同意半导体行业正在经历思维定式的转变。对大多数设计来说,28nm至少在相当长一段时间内是摩尔定律的最后节点。

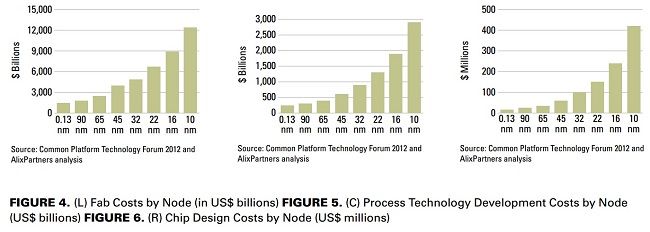

下面这些著名的图表表明了这种改变背后的理由。

图1:不同节点的工厂建造成本(左);不同节点的工艺技术研发成本(中);不同节点的芯片设计成本。单位:十亿美元

通过图1可以看出,从32nm到16nm设计成本的增加超过了1亿美元。如果我们假设32nm时一个裸片的成本是10美元,并且假设每个节点传统的成本下降仍将持续,那么我们需要超过2000万个裸片才能达到收支平衡。如果再考虑到与这种设计相关的风险,那么实际上要求超过1亿个裸片,或至少10亿美元市场,才能证明投资这种器件的合理性。很明显,很少有设计可以达到1亿片或10亿美元的市场规模。

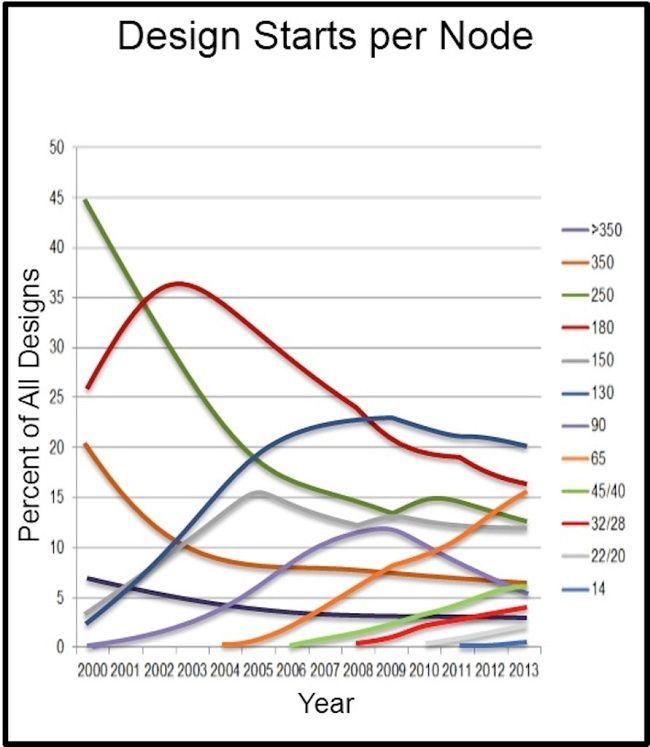

图2由IBS提供的图表展示了过去每个节点的设计启动趋势。从图中可以看出,大多数新设计仍然是在130nm节点创建,而发展速度最快的节点是65nm。

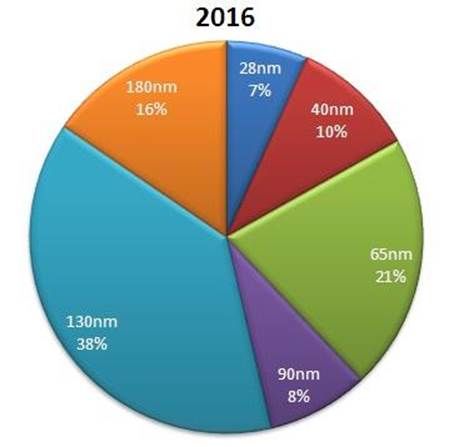

图3显示了Anysilicon公司对2016年半导体技术节点的预测。

同样,这张图表明向更先进节点转移的速度非常缓慢,可以预期的是:即使在2016年,大多数新设计仍然会在130nm节点实现。这明显是半导体行业的思维定式在转变,这是真实的反应。就在Semicon West 2014之前,我们就发现了SEMI的世界代工预测结论。这个预测使用了从底向上的方法,提供高层次的总结和图形,以及对资本支出、产能、技术和代工产品的深度分析。图4描述了这种新的模式。

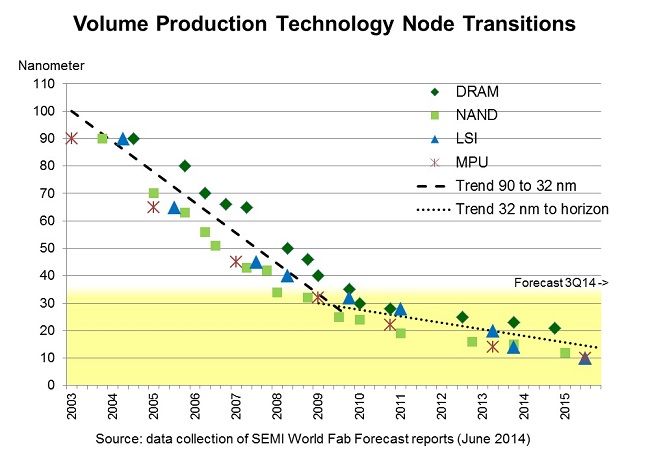

图4:批量生产技术节点转换。(来源:SEMI世界代工预测报告的数据采集(2014年6月))

报告指出:在32nm节点以下,每个晶圆的成本变得越来越重要。期望的在更小节点生产成本下降的好处在减少,并且在许多情况下跟不上缩放好处的步伐。这对长期遵循摩尔定律节奏发展的行业来说具有广泛而深远的意义。

这些也许是一些批量代工厂在启动新技术节点生产方面经常延迟的成因。现在第一次从数量上可以明显看出,前沿技术节点的批量生产缩放转换明显变慢。

在今年6月底,Rick Merritt在EE Times网站上的一个帖子中提到,大多数代工厂还没有开始购买14/16nm节点所需的资产设备,对大多数代工厂来说,这个节点是支持FinFET的首个节点,KLA-Tencor公司的Trafas表示。一些心急的公司希望从秋季开始有定单。

事实上,许多资本设备管理人员更关心的问题是,“16/14nm投资将何时开始?”

同样,Ed Sperling也表示,依靠多重图案工艺或FinFET提高能效和提升性能的工作已经在进行中。

由于28nm以下缩小特征尺寸的成本越来越高,业界正在尝试使用从近阈值计算到后向偏置和大多数精确的模拟传感器的各种方法,以期推进在成熟节点创建新的设计。

Gartner公司分析师Samuel Wang也曾表示,在FinFET生产的头两年这个短期时间内,所有代工厂加起来的月产能不用超过50000个晶圆就能满足市场对FinFET的需求。从长期来看,在2018年之前,月产能也不用超过25万个晶圆就能满足市场对FinFET的需求。

下一页:受物联网和可穿戴市场机会的驱动,SoC开发人员正在转回到已有的节点

{pagination}

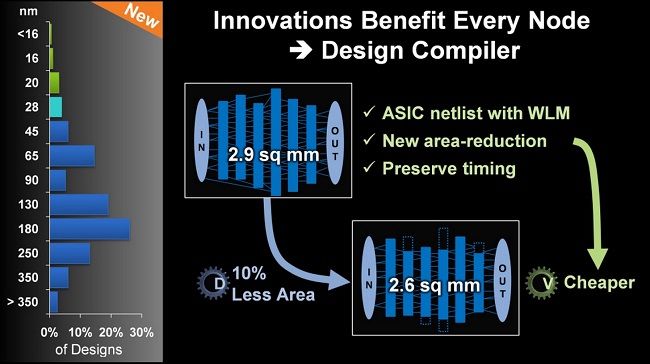

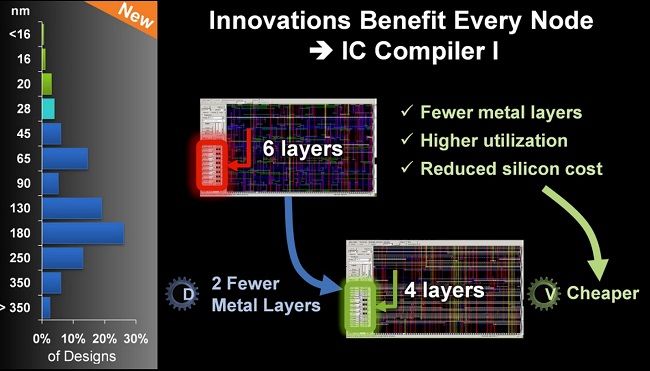

EDA行业也认识到了这种思维定式的改变。Aart de Geus博士在2014年Synopsys用户小组会议的主题演讲中用一组幻灯片承认了这种转变,并明确指出,为了支持新技术节点而开发的EDA工具同样能够让使用旧节点的设计工作受益。

图5:Aart de Geus博士在2014年Synopsys用户小组会议的主题演讲中的幻灯片(一)。

图6:Aart de Geus博士在2014年Synopsys用户小组会议的主题演讲中的幻灯片(二)。

IP行业同样认识到了这种思维定式的转变,正如Ann Steffora Mutschler在关于半导体工程技术的帖子中描述的那样:随着SoC开发人员转回到已有的节点,可以采取一些措施改进IP的功能。

受物联网和可穿戴市场机会的驱动,SoC开发人员正在转回到已有的节点。而随着IP向后移植以改进功能,在前沿节点学到的知识正在反哺已有节点。

很明显还有人在通过采用绝缘硅和被称为亚阈值设计的低Vt之类的技术给老节点增加价值和创新动力。最值得一提的是最近三星声称将来自意法半导体的FD-SOI许可给已有的28nm节点。

Cadence公司低功耗产品营销总监Krishna Balachandran指出,“诸如前向偏置等阈值电压处理方法被有选择地用于加快IP关键部分的运行速度,代价是增加了漏电流。不过这种方法仅限于对全局没有显著影响的那些IP部分。

ARM公司员工Rob Aitken表示,以不同的方式使用完全相同的处理器可以显著节省能源,而且在没有FinFET的已有工艺尺寸具有最高的效率。但它不是一个简单的工艺。“我们可以获得4倍到6倍的能耗改善。”他表示,“但达到这个结果不是没有代价的,因为我们必须对设计做出一些改变,才能允许设计在这个低能耗点工作。但如果我们做错了,那么达到这个节能效果必须增加的开销要比得到的好处还大。”

Synopsys公司Galaxy设计平台产品营销总监Mary Ann White指出,“衬底偏置是正在回收的另外一种技术。这种技术是在90nm时引入的,当时设计人员发现可以用这种技术将漏电流减小达30%。即使在45/40nm时,节能效果也能达到20%至25%的范围。但在28nm时, 块CMOS的好处下降到只有2%……当你使用偏置方法时,你是在使用额外的走线和额外的资源,其中可能包括一个或两个额外轨,但在使用平面CMOS的28nm节点,好处几乎荡然无存。让人重新燃起兴趣的是FD-SOI。其中的兴趣点在于,我们通常在需要一个块n阱或p阱引脚的后端插入偏置。但最近我们有了一个将这种功能增加进UPF的请求。虽然在对我们的产品有怀疑的情况下开展了这项工作,但我们得到了许多好处。如果你为了达到更好的功耗性能而增加5%的面积,这是值得的。”

这种思维定式转换对整个行业来说其实是一件好事。越来越高的成本促使风险投资商不再投资于半导体新创企业,并且极大地缩窄了供应商的数量和先进的新设计数量。除了奔向新技术节点,它在创新或其它方面都没有留出太多的空间。现在看来,整个新的行业动态正在发生。创新越来越盛行,新市场正在被不断开发,我们很有希望看到风险投资的回归,并在半导体供应商和技术方面加大投资。

本文来自《电子工程专辑》2014年10月刊,版权所有,谢绝转载。