OPTION_5:HP

在分开的谈话中,英特尔和台积电各自透露的两个新成就重新点燃了人们对远紫外光刻(EUV)的希望。远紫外光刻一直以来被人们看作是最有前途的工具之一,能够用来降低生产未来一代更小更快芯片的安装复杂性。

英特尔和台积电计划从大约2017年开始使用超精细制图系统生产他们的新一代7nm和10nm芯片。但这种雄心壮志已经受到许多次挫折了:远紫外光刻原本的目标是最早于2007年就开始使用。

“制造芯片变成了每个纳米都要较真的游戏,没有严格的和数学上合理的方法是不可能的。”英特尔公司首席光刻工程师Mark C.Phillips在接受《电子工程专辑》采访时表示。

图1:英特尔公司首席光刻工程师Mark C. Phillips。

在当地举行的SPIE光刻会议上,Phillips透露了ASML公司正在开发的一种新的分析工具,这种工具主要用于处理下一代芯片中的边缘布局错误——一种因多种原因造成的正在滋长的问题。只是新建模工具的一个方面“就要用大约10页纸的数学演算才能解释。”在去年一次会议之后要求ASML公司开始研究这个概念的Phillips表示。

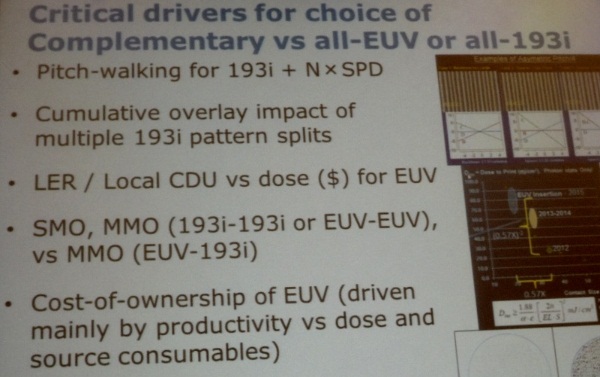

新的建模工具是所谓的互补光刻的关键。互补光刻是一种混合方法,一些任务用现有的浸润系统,另一些任务用新的远紫外光刻系统,Phillips告诉我们(见图2)。这种方法要求使用愈加严格的设计规则,并且晶圆要多次通过蚀刻系统。

图2:英特尔的互补刻蚀标准。

“有关整个行业向那个方向转变已有很多讨论——我们比大多数人开始得更早,因此在这方面有更多的经验。”他表示。

2012年时英特尔答应向远紫外光刻开发公司ASML投资约40亿美元,帮助他们推进这项工作。那年晚些时候台积电也宣布向ASML投资10亿美元。

{pagination}

电源和掩膜缺陷

就台积电而言,公司想在10nm只使用远紫外光刻,一次完成晶圆的制图,台积电公司下一代蚀刻部门经理Jack Chen表示。然而,即使这种方法奏效,台积电在7nm工艺中也需要使用不同的技术,7nm以下则使用具有更细数字孔径(NA)的升级版远紫外光刻系统。

图3:台积电公司下一代蚀刻部门经理Jack Chen。

7nm设计规则还不是很清楚,“如果没有高数字孔径解决方案,远紫外光刻不会在7nm以外工艺中使用。”他指出。

今天的远紫外光刻有两大问题。首先,它缺少足够强的电源来实现商用化所要求的每小时约200个晶圆的制图工作。另外,这种方法的掩膜仍存在不小的缺陷。

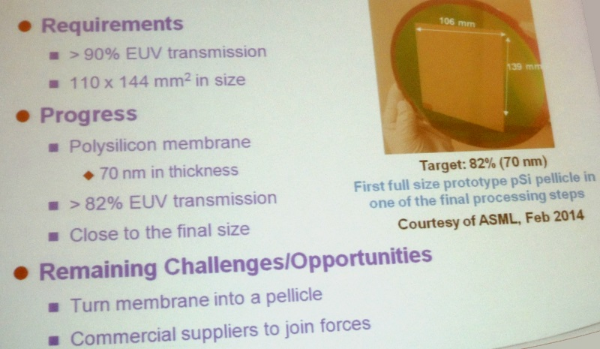

据Chen透露,ASML已经组建了一个新的工作组,准备定义一个表膜来覆盖远紫外光刻掩膜,以屏蔽掉缺陷。他指出,这将成为远紫外光刻商用化的一个必然要求。

ASML正在与位于荷兰埃因霍恩的邻居菲利浦公司合作开发一种多晶硅膜。他们的原型至今能够覆盖80%的晶圆。“下一步是将多晶硅转变为完整的表膜,并找一家商用供应商进行生产。”Chen表示。

根据Chen的报告,在通往250W远紫外光刻电源的长征途中只取得了很小的进步。他展示了台湾台积电公司使用20%占空比的新10W电源做的一个原型系统的数据,并称很快就有希望以100%的占空比驱动到30W。

图4:台积电认为远紫外光刻需要表膜。

“我们原本想要展示一些更高功率的数据来说服您远紫外光刻时代正在到来,但遗憾的是工具仍然没运行起来。“工程师们遇到一个很大的问题,由于没有对准200kW的激光器而损坏了其它一些元件。”他透露,并表示原型系统在他谈话的当天早上已经恢复工作了。

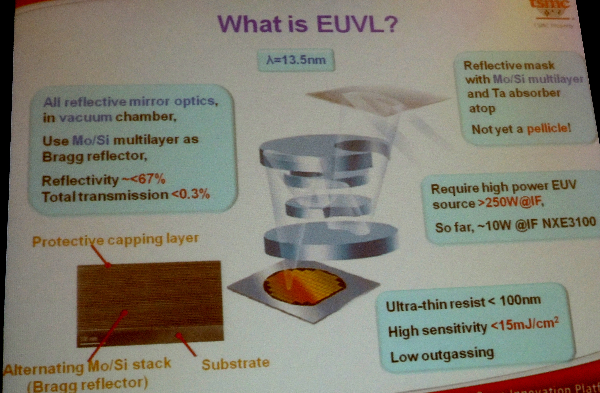

另外,他还概述了2017年在10nm节点将要部署的远紫外光刻系统所需要的部件,如图5。

图5:极远紫外光刻系统介绍。

本文来自《电子工程专辑》2014年4月刊,版权所有,谢绝转载。